# République Algérienne Démocratique et Populaire

Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

Université de Batna

Faculté des Sciences de l'Ingénieur

Département d'Informatique

# THESE

# Présentée par AMOKRANE Samah

En vue de l'obtention du diplôme de Magister en Informatique Option : Informatique Industrielle

# **THEME**

Algorithme Génétique pour le Problème d'Ordonnancement dans la Synthèse de Haut Niveau pour Contrôleurs Dédiés.

Soutenue le ..... devant le jury composé de :

| Dr Abdelmadjid ZIDANI       | M.C            | Université de Batna       | Président   |

|-----------------------------|----------------|---------------------------|-------------|

| Dr Mohamed BENMOHAMED       | M.C            | Université de Constantine | Rapporteur  |

| Dr Azzeddine BILAMI         | M.C            | Université de Batna       | Examinateur |

| Dr Mohamed Salah KHIREDDINE | $\mathbf{C.C}$ | Université de Batna       | Examinateur |

# <u>Résumé</u>

Le progrès offert par la technologie de fabrication des circuits micro-électroniques a ouvert la voie à la conception de systèmes digitaux d'une grande complexité. D'où la nécessité progressive de concevoir des circuits à de plus haut niveaux d'abstraction comme le niveau algorithmique. La synthèse de haut niveau consiste en la traduction d'une description comportementale (algorithmique) en une description équivalente au niveau transfert de registres. Le processus de synthèse de haut niveau est composé de plusieurs phases entre autres la phase d'ordonnancement. Cette phase, qui a une grande influence sur la qualité du circuit final, définit une date d'exécution pour chaque opération de la description algorithmique tout en respectant certaines contraintes. Une grande variété d'algorithmes existe dans la littérature pour résoudre efficacement le problème d'ordonnancement, reconnu comme étant un problème NP-Complet.

Cette thèse présente un aperçu sur les différentes techniques d'ordonnancement connues actuellement. Ces algorithmes ont été classifiés, selon leur domaine d'application, en deux catégories : des algorithmes orientés flot de données et ceux orientés flot de contrôle. Pour chaque catégorie un ensemble d'algorithmes sont décrits brièvement. Finalement, on propose une technique d'ordonnancement GPBS, pour les circuits de contrôle, basée sur la combinaison de l'algorithme d'ordonnancement à base de chemins et d'un algorithme génétique.

<u>Mots-clés</u>: CAO/VLSI, Synthèse de haut niveau, Ordonnancement, Algorithme d'ordonnancement à base de chemin, Algorithmes génétiques.

# <u>Abstract</u>

The progress offered by the technology of micro-electronics circuits manufacture opened the way to the conception of digital systems of a big complexity. From where the progressive necessity to conceive circuits to higher levels of abstraction as the algorithmic level. The High-Level Synthesis consists in the translation of a behavioral description (algorithmic) in an equivalent description at the Register-Transfer Level. The High-Level Synthesis process is composed of several phases among others the phase of scheduling. This phase, which has a tremendous impact on the final design quality, defines a date of execution for every operation of the algorithmic description while respecting some constraints. A big variety of algorithms exists in the literature to solve efficiently the problem of scheduling, recognized as being an NP-complete problem.

This thesis presents a preview on the different scheduling techniques known currently. These algorithms have been classified, according to their domain of application, in two categories,: data flow oriented algorithms and those control flow oriented. For every category a whole of algorithms is described briefly. Finally, we propose a scheduling technique GPBS, for circuits of control, based on the combination of the Path-Based Scheduling algorithm and a genetic algorithm.

<u>Key-words:</u> CAD/VLSI, High-Level Synthesis, Scheduling, Path based scheduling algorithm, Genetic algorithms.

# Remerciements

Je tient avant tout à exprimer ma profonde reconnaissance à Mr Mohamed BENMOHAMMED Maître de Conférence à l'Université de Constantine, qui a assuré la direction de ma thèse, pour son suivi et ses conseils judicieux. Qu'il trouve ici l'expression de mon profond respect.

Je remercie Mr ZIDANI, Maître de Conférence à l'Université de Batna, de m'avoir fait l'honneur de présider le jury de ma thèse.

Je remercie, également, Mr BILAMI Maître de Conférence à l'Université de Batna et Mr KHIREDDINE Chargé de Cours à l'Université de Batna, qui ont accepté d'être membres du jury de cette thèse.

Je remercie Mr DEKHINET pour toute la documentation qu'il m'a fourni, ainsi que Mr ABDESSEMED Ridha pour son aide.

Un très grand et très spécial merci à mes parents, et à toute ma famille.

Que toutes les personnes et tous mes amis qui m'ont soutenu moralement soient assurés de l'expression de ma reconnaissance.

A mon père et ma mère, A ma sœur et mes frères.

# Liste des figures

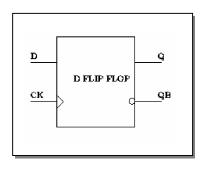

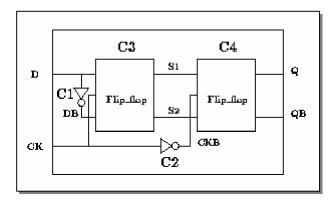

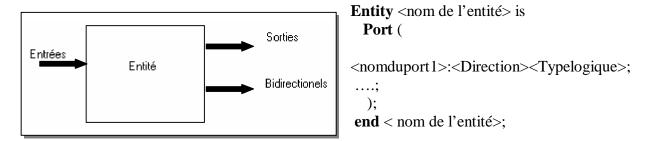

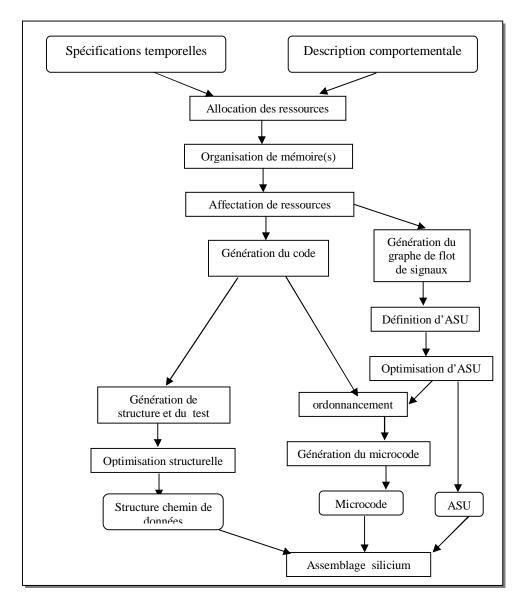

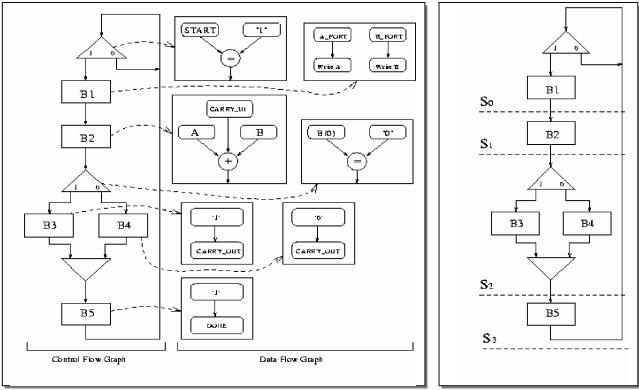

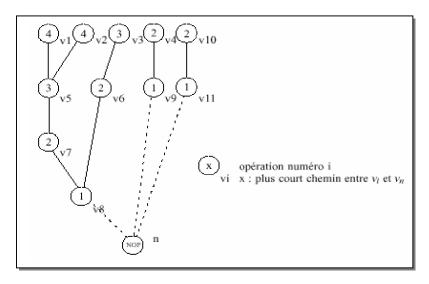

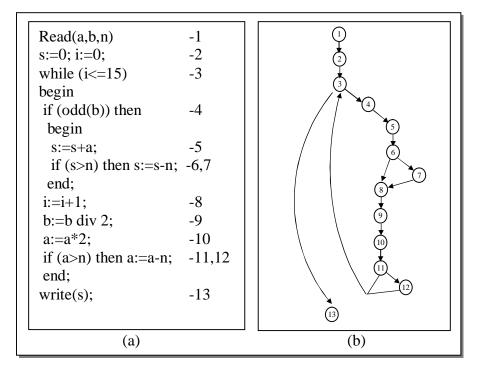

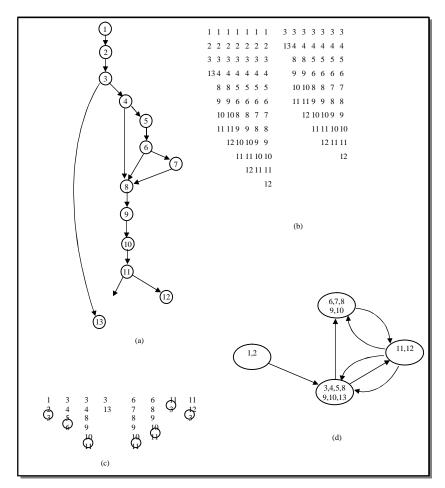

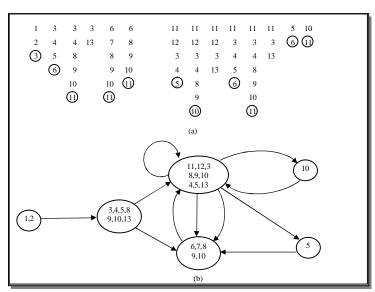

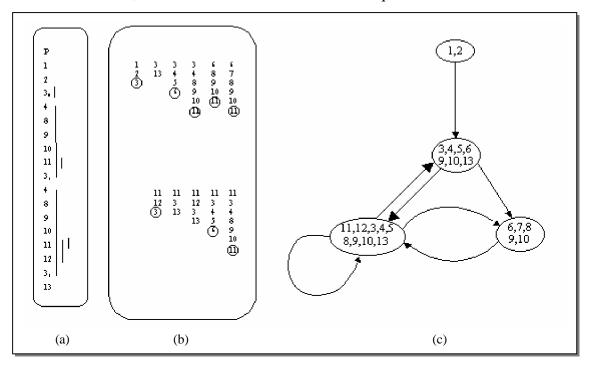

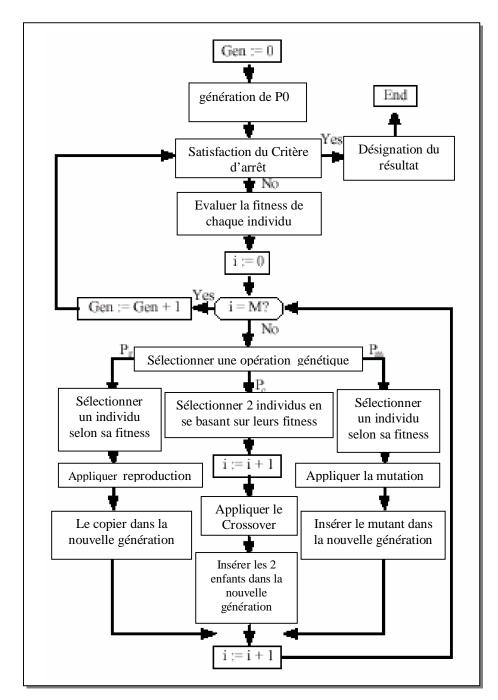

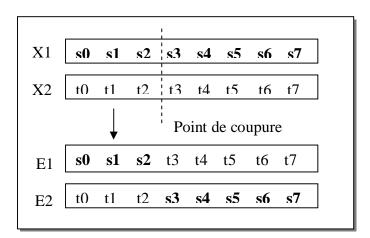

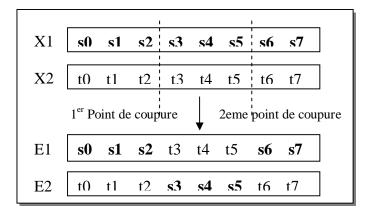

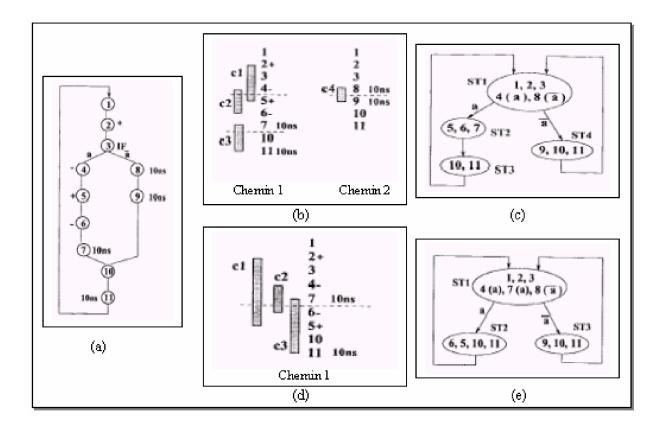

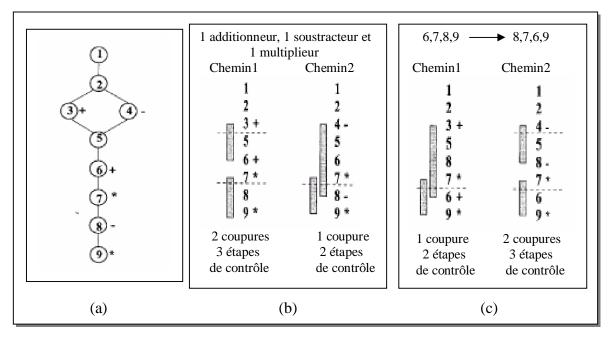

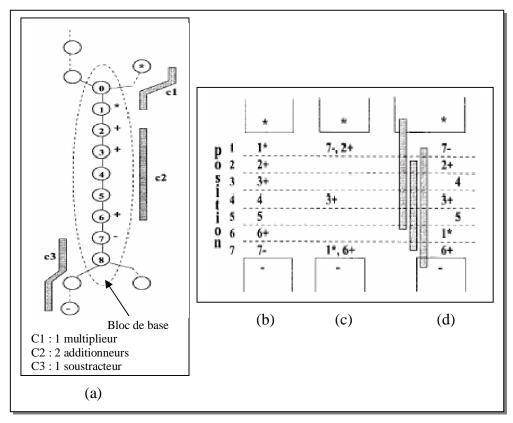

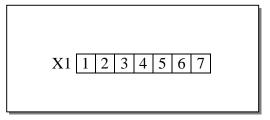

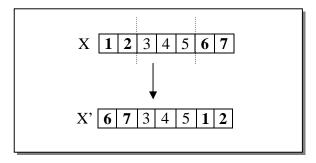

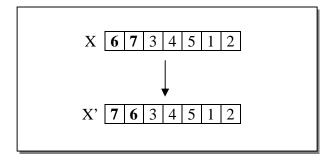

Figure 2.1 : Domaines de représentation et niveaux d'abstraction (diagramme en Y de Gajski) Figure 2.2 : Description Silage d'un filtre récursif Figure 2.3 : Exemple de description Verilog Figure 2.4 : Bascule D et Description VHDL correspondante Figure 2.5 : Vision structurelle de la bascule Figure 2.6 : Vue générale de la syntaxe d'une déclaration d'entité Figure 2.7 : Exemple d'entité avec déclaration de bibliothèque Figure 2.8 : Vue générale de la syntaxe d'une déclaration d'architecture Figure 3.1 : La synthèse de haut niveau **Figure 3.2** : Graphe de flot de contrôle Figure 3.3 : Graphe de flot de données **Figure 3.4** : Graphe de flot de données et de contrôle **Figure 3.5** : Architecture au niveau transfert de registres **Figure 3.6**: Architecture cible de Behavioral Compiler Figure 3.7 : Flot de synthèse de BC **Figure 3.8**: Architecture cible de CATHEDRAL-2/3 **Figure 3.9**: Flot de conception de CATHEDRAL-2/3 Figure 3.10: Architecture cible d'AMICAL Figure 3.11 : Flot de synthèse d'AMICAL Figure 4.1 : CDFG de l'additionneur Figure 4.2 : Ordonnancement du CDFG Figure 4.3 : Ordonnancement (a) flot de données (b) flot de contrôle Figure 4.4 : Ordonnancement sous contraintes matérielles et minimisation du nombre d'étapes de contrôle Figure 4.5 : Ordonnancement sous contraintes temporelles et minimisation du nombre d'opérateurs **Figure 5.1**: Algorithme ASAP Figure 5.2 : Ordonnancements ASAP et ALAP **Figure 5.3**: Algorithme ALAP Figure 5.4 : Algorithme d'ordonnancement par liste sous contraintes matérielles Figure 5.5 : Priorités associées aux opérations Figure 5.6 : Algorithme d'ordonnancement par les forces Figure 5.7 : Description algorithmique de la fonction ab mod n et CFG correspondant Figure 5.8 : Chemins ordonnées et FSM pour l'ordonnancement à base de chemin Figure 5.9 : FSM pour l'ordonnancement à boucle dynamique Figure 5.10 : FSM pour l'ordonnancement pipeliné à base de chemin Figure 6.1 : Organigramme d'un algorithme génétique type (simple) Figure 6.2 : Opérateur de croisement à un seul point de coupure Figure 6.3 : Opérateur de croisement à deux points de coupure Figure 6.4 : Opérateur de croisement uniforme Figure 6.5 : Opérateur de mutation Figure 6.6 : Exemple d'un ordonnancement à base de chemins Figure 6.7 : Effet du réordonnement sur l'ensemble des chemins Figure 6.8 : Algorithme de réordonnement

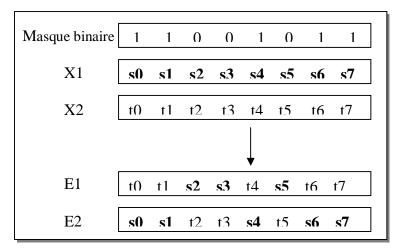

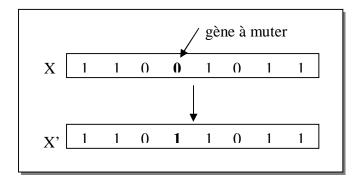

Figure 6.9 : Codage du chromosome Figure 6.10 : Exemple de croisement Figure 6.11 : Exemple de mutation

# Liste des tableaux

Tableau 2.1 : Différentes architectures associées à une même spécification d'entité

Tableau 3.1 : Outils de synthèse orientés flot de données Tableau 3.2 : Outils de synthèse orientés flot de contrôle Tableau 3.3 : Récapitulatif des trois outils de synthèse

**Tableau 4.1 :** Modes d'ordonnancement

# Table des matières

| Chapitre 1 : Introduction                               | 1  |

|---------------------------------------------------------|----|

| 1.1 Introduction                                        | 1  |

| 1.2 Structure du mémoire                                | 2  |

|                                                         |    |

| Chapitre 2 : Synthèse de circuits                       | 3  |

| 2.1 Introduction                                        |    |

| 2.2 Niveaux d'abstraction                               |    |

| 2.3 Flot de conception d'un circuit                     |    |

| 2.3.1 Synthèse au niveau système                        |    |

| 2.3.2 Synthèse de haut niveau                           |    |

| 2.3.3 Synthèse au niveau transfert de registres         |    |

|                                                         |    |

| 2.3.4 Synthèse logique                                  |    |

| 2.3.5 Synthèse physique                                 |    |

| 2.4 Langages de description                             |    |

| 2.4.1 Langages déclaratifs                              |    |

| 2.4.1.1 Silage                                          |    |

| 2.4.2 Langages procéduraux                              |    |

| 2.4.2.1 Verilog                                         |    |

| 2.4.2.2 VHDL                                            |    |

| 2.4.3 Quel langage utiliser?                            |    |

| 2.5 VHDL                                                | 11 |

| 2.5.1 Description d'un module en VHDL                   | 12 |

| 2.5.1.1 L'énoncé Entity                                 | 12 |

| 2.5.1.2 L'énoncé Architecture                           | 14 |

| 2.5.2 L'énoncé Process                                  | 14 |

| 2.5.3 Les signaux et les variables                      | 15 |

| 2.5.4 Les types de données                              | 16 |

| 2.5.5 Instructions concurrentes                         | 18 |

| 2.5.6 Instructions conditionnelles                      |    |

| 2.5.7 Instructions itératives                           |    |

| 2.5.8 Programmation modulaire                           |    |

| 2.5.8.1 Procédures et fonctions                         |    |

| 2.5.8.2 Les paquetages et les librairies                |    |

| 2.5.9 Les paramètres génériques                         |    |

| 2.6 Conclusion                                          |    |

| 2.0 Conclusion                                          | ∠+ |

| Chapitre 3 : Synthèse de haut niveau                    | 25 |

| 3.1 Introduction                                        |    |

| 3.2 Principe général de la synthèse de haut niveau      |    |

|                                                         |    |

| 3.3 Domaine d'application de la synthèse de haut niveau |    |

| 3.4 Représentation interne                              |    |

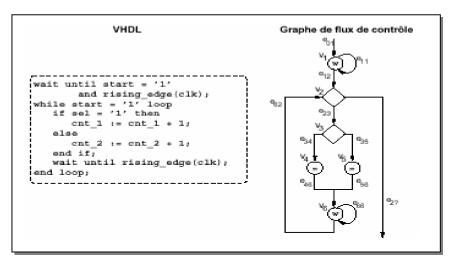

| 3.4.1 Graphe de flot de contrôle                        |    |

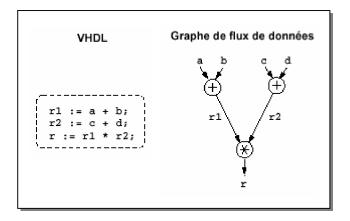

| 3.4.2 Graphe de flot de données                         |    |

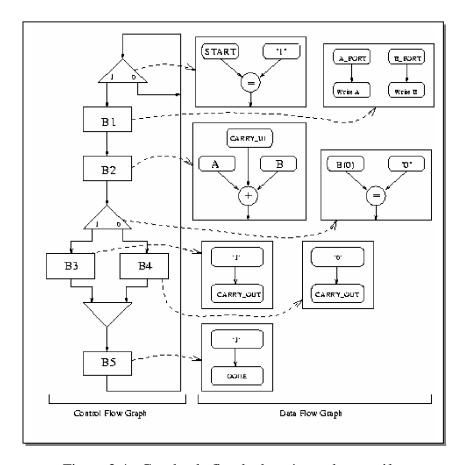

| 3.4.3 Représentation interne des applications mixtes    |    |

| 3.5 Flot de la synthèse de haut niveau                  |    |

| 3.5.1 Description comportementale                       |    |

| 3.5.2 Compilation de la description comportementale     |    |

| 3.5.3 Ordonnancement                                    | 33 |

| 3.5.4 Allocation/Assignation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 3.5.5 Génération d'architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38                                                                               |

| 3.6 Outils de synthèse de haut niveau                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38                                                                               |

| 3.6.1 Behavioral Compiler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 3.6.1.1 Flot de synthèse de BC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 3.6.1.2 Points forts et limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| 3.6.2 Cathedral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| 3.6.2.1 Flot de synthèse de Cathedral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 3.6.2.2 Points forts et limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

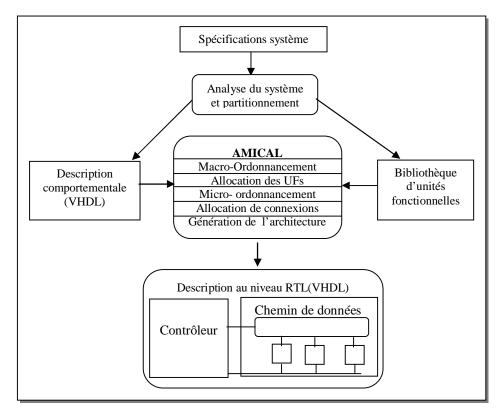

| 3.6.3 Amical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| 3.6.3.1 Flot de synthèse d'Amical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

| 3.6.3.2 Points forts et limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 49                                                                               |

| 3.7 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50                                                                               |

| Chapitre 4 : Formalisation du problème d'ordonnancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                                               |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

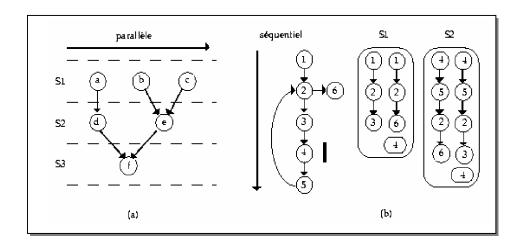

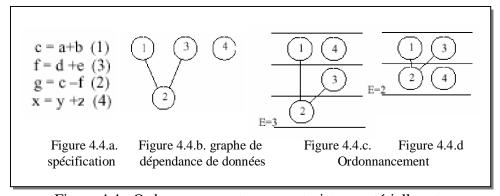

| 4.2 Mode d'ordonnancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| 4.3 Différents types d'ordonnancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 4.3.1 Algorithmes orientés flot de données                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| 4.3.1.1 Ordonnancement sans contraintes US                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| 4.3.1.2 Ordonnancement sous contraintes de ressources RCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

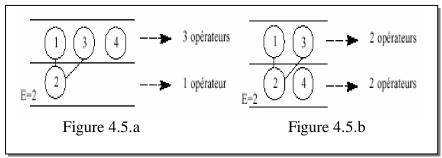

| 4.3.1.3 Ordonnancement sous contraintes de temps TCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| 4.3.1.4 Ordonnancement sous contraintes de temps et de ressourc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| 4.3.2 Algorithmes orientés flot de contrôle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| 4.4 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| 4.4 Coliciusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 01                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| Chapitre 5 : Algorithmes d'ordonnancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62                                                                               |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62                                                                               |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62<br>62                                                                         |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62<br>62<br>63                                                                   |

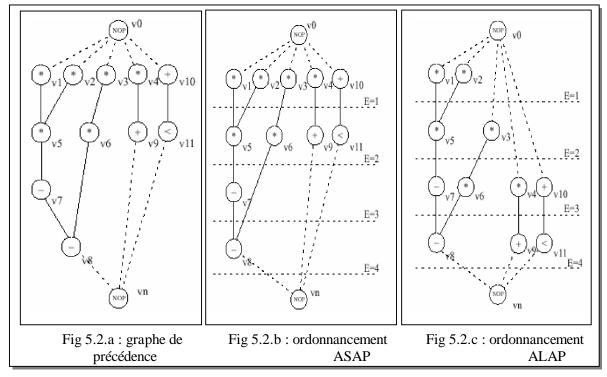

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62<br>62<br>63<br>64                                                             |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62<br>62<br>63<br>64<br>65                                                       |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62<br>62<br>63<br>64<br>65                                                       |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62<br>62<br>63<br>64<br>65                                                       |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62<br>62<br>63<br>64<br>65<br>65                                                 |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62<br>62<br>63<br>64<br>65<br>65<br>66                                           |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS                                                                                                                                                                                                                                                                                                                                                                                                                                | 62<br>62<br>63<br>64<br>65<br>65<br>66<br>69                                     |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR                                                                                                                                                                                                                                                                                                                                                                                            | 62<br>62<br>63<br>64<br>65<br>66<br>66<br>69                                     |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle                                                                                                                                                                                                                                                                                                                                | 62<br>62<br>63<br>64<br>65<br>66<br>69<br>69                                     |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS                                                                                                                                                                                                                                                                                    | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>69                                     |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS                                                                                                                                                                                                                                       | 62<br>62<br>63<br>64<br>65<br>66<br>69<br>69<br>71<br>71                         |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS  5.4.3 Algorithme d'ordonnancement pipeliné à base de chemins PPS                                                                                                                                                                     | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>71<br>71<br>72                         |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS  5.4.3 Algorithme d'ordonnancement pipeliné à base de chemins PPS  5.4.4 Dominator-Path Scheduling                                                                                                                                    | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>71<br>71<br>72<br>74                   |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS  5.4.3 Algorithme d'ordonnancement pipeliné à base de chemins PPS  5.4.4 Dominator-Path Scheduling  5.4.5 Software pipelining                                                                                                         | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>71<br>71<br>72<br>74<br>76             |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS  5.4.3 Algorithme d'ordonnancement pipeliné à base de chemins PPS  5.4.4 Dominator-Path Scheduling                                                                                                                                    | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>71<br>71<br>72<br>74<br>76             |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS  5.4.3 Algorithme d'ordonnancement pipeliné à base de chemins PPS  5.4.4 Dominator-Path Scheduling  5.4.5 Software pipelining                                                                                                         | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>71<br>72<br>74<br>76<br>76             |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS  5.4.3 Algorithme d'ordonnancement pipeliné à base de chemins PPS  5.4.4 Dominator-Path Scheduling  5.4.5 Software pipelining  5.5 Conclusion  Chapitre 6 : Algorithme d'ordonnancement                                               | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>71<br>72<br>74<br>76<br>77             |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS  5.4.3 Algorithme d'ordonnancement pipeliné à base de chemins PPS  5.4.4 Dominator-Path Scheduling  5.4.5 Software pipelining  5.5 Conclusion  Chapitre 6 : Algorithme d'ordonnancement                                               | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>71<br>71<br>72<br>74<br>76<br>77       |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS  5.4.3 Algorithme d'ordonnancement pipeliné à base de chemins PPS  5.4.4 Dominator-Path Scheduling  5.4.5 Software pipelining  5.5 Conclusion  Chapitre 6 : Algorithme d'ordonnancement  6.1 Introduction  6.2 Algorithmes génétiques | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>71<br>71<br>72<br>74<br>76<br>76<br>77 |

| Chapitre 5 : Algorithmes d'ordonnancement  5.1 Introduction  5.2 Classification des algorithmes d'ordonnancement  5.3 Algorithmes d'ordonnancement orientés flot de données  5.3.1 Algorithme ASAP  5.3.2 Algorithme ALAP  5.3.3 Programmation en nombres entiers ILP  5.3.4 Algorithme d'ordonnancement par liste LS  5.3.5 Algorithme d'ordonnancement par liste statique SLS  5.3.6 Ordonnancement orienté par les forces FDS  5.3.7 Réordonnancement itératif IR  5.4 Algorithmes d'ordonnancement orientés flot de contrôle  5.4.1 Ordonnancement à base de chemins PBS  5.4.2 Ordonnancement à boucle dynamique DLS  5.4.3 Algorithme d'ordonnancement pipeliné à base de chemins PPS  5.4.4 Dominator-Path Scheduling  5.4.5 Software pipelining  5.5 Conclusion  Chapitre 6 : Algorithme d'ordonnancement                                               | 62<br>62<br>63<br>65<br>65<br>66<br>69<br>71<br>71<br>72<br>74<br>76<br>76<br>77 |

| 6.2.2 Génération de la population initiale                                 | . 81 |

|----------------------------------------------------------------------------|------|

| 6.2.3 Fonction de mérite                                                   | 82   |

| 6.2.4 Sélection                                                            | . 83 |

| 6.2.5 Croisement                                                           |      |

| 6.2.6 Mutation                                                             | . 85 |

| 6.3 Les algorithmes génétiques au service d'autres algorithmes             | . 86 |

| 6.4 Algorithme GPBS (Genetic Path Based Scheduling)                        | 86   |

| 6.4.1 Algorithme à base de chemins PBS                                     | 87   |

| 6.4.2 Combinaison de l'algorithme PBS avec un algorithme génétique         | 89   |

| 6.4.3 Différentes étapes de l'algorithme GPBS                              | . 92 |

| 6.4.4 Définition de l'algorithme génétique et de ses différents opérateurs | 93   |

| 6.5 Conclusion                                                             | 98   |

| Chapitre 7 : Conclusion et perspectives                                    | 99   |

| 7.1 Synthèse                                                               |      |

| 7.2 Perspectives                                                           | 100  |

| Bibliographie:                                                             | 101  |

# Chapitre 1 Introduction

# 1.1. Introduction

La technologie VLSI (Very Large Scale Integration) a connu une grande évolution, permettant l'intégration de systèmes complexes, composés de millions de transistors, sur une seule puce. Avec de tels systèmes, le processus de conception devient très difficile à gérer sans l'utilisation efficace d'outils CAO (Conception Assistée par Ordinateur).

Les outils CAO aident à automatiser une grande partie du processus de conception, permettant ainsi au concepteur de ne pas se préoccuper des considérations de bas niveau. Ceci a permis une réduction considérable du temps de conception, améliorant ainsi le temps d'arrivée sur marché - Time to market - qui est un facteur crucial de réussite pas moins important que la surface ou la vitesse. Ceci a permis aussi aux concepteurs de manipuler des circuits plus complexes et d'étudier facilement les effets de variation des paramètres de conception sur le circuit final, en d'autres termes l'exploration complète de l'espace de conception.

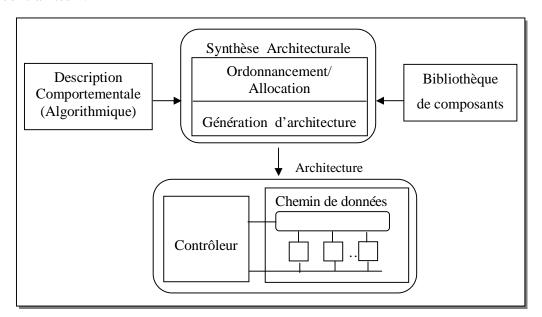

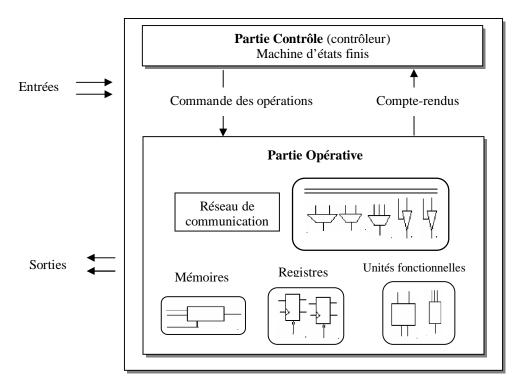

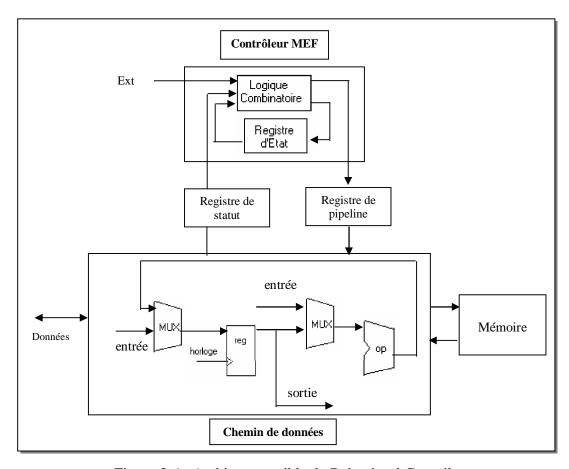

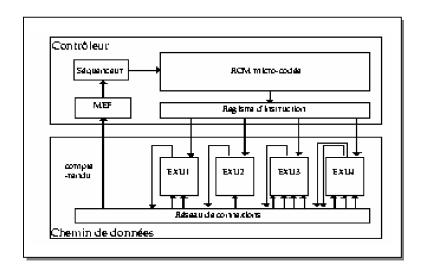

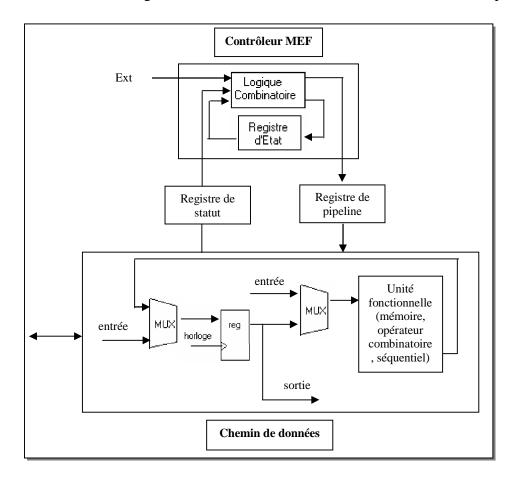

En plus, avec l'accroissement de la complexité des circuits, apparaît le besoin de travailler à de plus haut niveaux d'abstraction, favorisant ainsi le développement de nouvelles méthodologies de conception comme la synthèse de haut niveau appelée aussi synthèse comportementale. Cette dernière traduit une description comportementale d'un circuit en une description structurelle au niveau transfert de registres, suivant certains critères. Le comportement d'un circuit est décrit à l'aide d'un langage de description de matériel HDL (VHDL, HARDWARE C,...). Alors que la sortie au niveau RTL (Register Transfert Level) est composée d'un contrôleur et d'un chemin de données. Le contrôleur est défini comme une machine d'états finis FSM (Finites States Machine), alors que le chemin de données est décrit à l'aide d'instances d'unités fonctionnelles, d'unités de stockage et d'unités de communication interconnectées. La machine d'états finis spécifie quelles sont les opérations que doit exécuter le chemin de données à chaque étape de contrôle.

La nature de l'application traitée, qu'elle soit orientée flot de contrôle ou orientée flot de données, fait que l'effort d'optimisation soit consacré en grande partie à la génération de la partie contrôle ou la partie opérative.

Le processus de synthèse de haut niveau est exécuté en une séquence d'étapes, dont l'ordonnancement des opérations, l'allocation des ressources aux opérations et l'assignation des ressources aux opérations sont les étapes les plus marquantes.

L'objectif de ce mémoire est double. D'une part, présenter les différentes tâches de la synthèse de haut niveau et étudier, plus spécialement, les algorithmes d'ordonnancement dans leur globalité. D'autre part, choisir parmi les algorithmes étudiés ceux qui s'adaptent le mieux aux besoins des circuits de commande. La majorité des algorithmes d'ordonnancement existants traitent les applications dominées par le flot de données et concentrent principalement sur les calculs à l'intérieur d'un bloc de base. Alors que les circuits dominés par le contrôle ont une structure de flot de contrôle complexe contenant des boucles et des instructions conditionnelles. Il est donc nécessaire de prendre en compte les caractéristiques de ces applications et de développer un ensemble de techniques qui permettent de minimiser le coût de la partie contrôle. Pour cela, notre choix a porté sur l'algorithme d'ordonnancement à base de chemin PBS (Path Based Scheduling Algorithm) qui est à la base de la majorité des algorithmes d'ordonnancement des circuits de contrôle.

L'apport de ce mémoire concerne l'extension de l'algorithme PBS par l'introduction d'un algorithme génétique qui a pour rôle le réordonnement des opérations. Ce travail est proposé dans l'optique d'apporter plusieurs améliorations et optimisations par rapport à l'algorithme PBS pré-existant.

# 1.2. Structure du mémoire

Le déroulement de ce mémoire suivra les étapes suivantes:

Le chapitre suivant présente en premier les différents niveaux d'abstraction ainsi que le flux de conception d'un circuit intégré, suivi d'une brève description des langages de description de matériel et spécialement le langage VHDL.

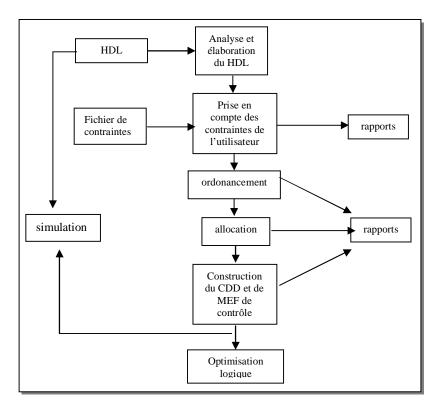

Le chapitre 3 est une introduction à la synthèse de haut niveau constituée de plusieurs étapes, dont l'ordonnancement et l'allocation sont les plus importantes. Outre une brève présentation de ces différentes étapes et des différentes représentations intermédiaires, ce chapitre présente trois outils de synthèse de haut niveau, à savoir AMICAL, CATHEDRAL-2/3 et SYNOPSYS Behavioral Compiler.

Le chapitre 4 décrit le problème d'ordonnancement, ainsi qu'une classification des différents types d'ordonnancement. Cette classification se base sur les représentations intermédiaires de la description comportementale.

Le chapitre 5 dresse un état de l'art sur les différentes approches et algorithmes proposés pour résoudre le problème d'ordonnancement considéré comme un problème NP-Complet.

Le chapitre 6 donne une présentation globale des algorithmes génétiques ainsi que les différents opérateurs génétiques mis en œuvre. Il présente, également, une nouvelle technique d'ordonnancement des circuits dominés par le flot de contrôle GPBS, qui consiste à utiliser un algorithme génétique en conjonction avec l'algorithme d'ordonnancement à base de chemin PBS.

Le chapitre 7 conclut et présente les perspectives de notre travail.

# Chapitre

2

# Synthèse de circuits

# 2.1. Introduction

L'évolution de la technologie des circuits intégrés a permis de réaliser des systèmes de plus en plus complexes et même leur intégration sur une seule puce. Cette évolution demande des niveaux d'intégration de plus en plus élevés, motivée par les besoins de systèmes plus performants, légers, compacts et consommant un minimum de puissance. Dans de telles circonstances, le raisonnement sur un circuit au niveau transistor ou au niveau porte devient une tâche pénible et coûteuse quand on considère les contraintes de mise en marché d'un produit. De plus, en se dégageant des niveaux de spécification ou de description les plus élémentaires, la fonctionnalité est plus facilement compréhensible et peut donc être plus aisément corrigée ou modifiée. De ce fait, et afin de réduire le coût et le temps de conception des circuits, l'automatisation du processus de conception et l'abstraction du niveau de conception sont privilégiées [1].

La synthèse automatique est l'une des approches les plus prometteuses. Elle consiste en la traduction d'une description abstraite d'un circuit en une description plus concrète. Elle permet d'évaluer plusieurs possibilités d'implémentation. Elle contribue aussi à l'amélioration de la qualité des circuits [1,2].

Pour la conception d'un système électronique, l'une des méthodes que peut utiliser un concepteur est la méthode " top down design". Un système est construit comme une hiérarchie d'objets où les détails de réalisation se précisent au fur et à mesure que l'on descend dans cette hiérarchie; à un niveau donné de la hiérarchie, les détails de fonctionnement interne des niveaux inférieurs sont invisibles. Plusieurs réalisations d'une même fonction pourront être envisagées, sans qu'il soit nécessaire de remettre en cause la conception des niveaux supérieurs; plusieurs personnes pourront collaborer à un même projet, sans que chacun ait à connaître tous les détails de l'ensemble.

# 2.2. Niveaux d'abstraction

En général, la conception d'un circuit est un processus itératif. Dans les premières étapes, le système est représenté par une description comportementale. Puis, les détails structurels (i.e. comment sont interconnectés les sous-modules pour former un module) sont ajoutés au fur et à mesure, jusqu'à l'obtention d'une description structurelle (i.e. composée des éléments de base tels que portes, bascules, etc et leurs interconnexions). Enfin, les éléments de la description structurelle sont implémentés par des éléments physiques (par exemple, dessin de masque représentant une bascule) [1].

L'abstraction, d'un composant par exemple, est une description succincte qui supprime les détails d'implantation inutiles pour en comprendre la fonctionnalité. Donc, on identifie dans chaque abstraction deux niveaux : le niveau succinct le plus élevé, ou *spécification*, et le niveau détaillé le plus bas, ou *réalisation* [3]. On distingue trois domaines de représentation d'un circuit : [2]

# - Domaine comportemental:

On s'intéresse à ce que fait le circuit et non pas à sa mise en œuvre. On décrit le comportement de chaque sortie en fonction des entrées et du temps. Le fonctionnement du circuit peut être spécifié par des équations booléennes, des tables de valeurs des entrées et des sorties, ou des algorithmes écrits en langages de haut niveau standards ou des langages de description de matériel spéciaux (HDLs) tels que VHDL, Verilog.

# - Domaine structurel :

Il sert de lien entre le domaine comportemental et le domaine physique. Le circuit y est représenté comme une interconnexion de composants de base (portes, bascules, etc.).

# - Domaine physique:

On spécifie comment construire une structure qui a la connectivité nécessaire pour implémenter la fonctionnalité prescrite. Généralement le circuit se présente dans ce domaine sous la forme de dessin de masque. La fonctionnalité est ignorée, dans la mesure du possible, on décrit les objets réels (par exemple les transistors d'un circuit).

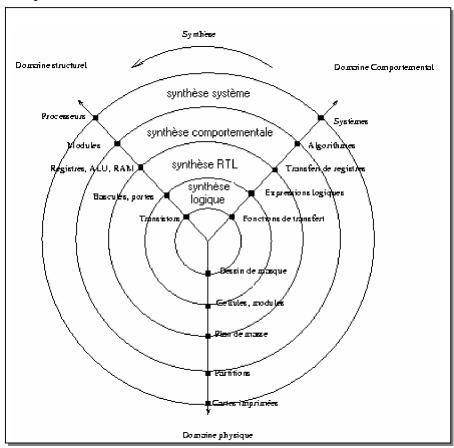

Le diagramme en Y de Gajski et Kuhn [1,2,4] illustre les différents types de synthèse et les différents niveaux d'abstraction. Les trois domaines de description : comportemental, structurel et physique sont représentés par trois axes. Les cercles concentriques présentent les différents niveaux d'abstraction et leurs représentations dans chacun des trois domaines. Plus on s'éloigne du centre plus le niveau devient plus abstrait. Une tâche de synthèse peut être vue comme une transformation d'un axe à un autre et/ou une transformation d'un niveau d'abstraction à un autre [4].

Un niveau d'abstraction est caractérisé par les objets qu'il manipule. Un objet peut être un rectangle (niveau Layout), un transistor, un opérateur complexe, etc [5]. Différents niveaux d'abstraction ont été identifiés [1,4,6]:

# - Niveau système (System level) :

Le niveau système est utilisé pour spécifier des systèmes entiers, comprenant des parties logicielles et des parties matérielles. Les descriptions comportementales du niveau système sont généralement données en terme de processus communicants. Dans le domaine structurel, les descriptions sont en terme d'interconnexions d'éléments tels que processeurs, mémoires,

unités périphériques, etc. L'étape de base est la transaction de communication pour contrôler l'enchaînement des processus.

# - Niveau algorithmique (Algorithm level) :

La description à ce niveau s'attache à décrire le fonctionnement (comportement) d'un modèle sans se soucier de la structure. Les objets manipulés à ce niveau sont des variables et des opérateurs. L'étape de base est le pas de calcul. Un pas de calcul se compose d'un ensemble d'opérations exécutées entre deux points successifs d'entrées/sorties et/ou de synchronisation. Il peut durer plusieurs cycles d'horloge.

#### - Niveau transfert de registres (Register Transfert Level) :

Le comportement à ce niveau est décrit par des transferts et des opérations entre registres. La structure est représentée par l'interconnexion de registres, d'opérateurs arithmétiques et logiques, etc. (on spécifie une opération et non pas une implémentation spécifique de l'opération). Le temps est divisé en intervalles appelés états de contrôle.

# - Niveau logique (Gate level) :

A ce niveau, la description comportementale se fait avec des équations booléennes, qui sont représentées dans le domaine structurel par des blocs logiques (bascules, portes).

# - Niveau physique (Circuit level):

C'est le niveau d'abstraction le plus bas. Le comportement à ce niveau est décrit par des fonctions de transferts. La structure est représentée par l'interconnexion de composants électroniques tels que transistors, diodes, etc.

Figure 2.1: Domaines de représentation et niveaux d'abstraction (diagramme en Y de Gajski)

La décomposition en niveaux d'abstraction peut varier selon les auteurs. Certains auteurs [2,5,7] n'utilisent que quatre niveaux d'abstraction ( pour certains [2] les niveaux système et comportemental ne font qu'un seul niveau, pour d'autres [5,7] le niveau logique et physique sont réunis en un seul).

Ces niveaux d'abstraction correspondent aux étapes de la conception d'un circuit sur silicium. Le passage d'un niveau de représentation à un niveau inférieur est réalisé par ce qu'on appelle des "compilateurs de silicium".

# 2.3. Flot de conception d'un circuit

Les circuits actuels sont si complexes qu'il a bien fallu développer un ensemble de niveaux d'abstraction afin de diviser le flot de synthèse en sous-problèmes simplifiés.

Comme dit précédemment, la synthèse peut être vue comme un changement de domaine de représentation et/ou de niveau d'abstraction. Suivant le niveau d'abstraction de la description d'entrée et celui de la sortie, plusieurs types de synthèse peuvent être considérés, comme illustré par la figure 2.1 : synthèse au niveau système, synthèse comportementale, synthèse au niveau transfert de registres, synthèse logique, et synthèse physique.

# 2.3.1. Synthèse au niveau système

La première étape du flot de synthèse se situe au niveau système, c'est l'étape de partitionnement. Le partitionnement consiste, à partir des spécifications, à découper le système en sous-systèmes (processus) communicants. Un processus peut être partitionné une nouvelle fois en un ensemble de processus communicants. Le niveau système est utilisé pour spécifier des systèmes entiers, comprenant des parties logicielles et des parties matérielles. Le partitionnement peut être guidé par de nombreux paramètres comme la fonctionnalité, la synchronisation et la concurrence de tâches [7], le partitionnement matériel/logiciel [1], etc.

# 2.3.2. Synthèse de haut niveau

La synthèse de haut niveau (dite aussi synthèse architecturale ou comportementale) prend en entrée une spécification algorithmique de la fonction réalisée par le système à concevoir. Cette description sera traduite, par un outil de synthèse architecturale, en une description structurelle au niveau transfert de registres. La synthèse comportementale peut être décomposée en trois étapes majeures : l'ordonnancement, l'allocation, et l'assignation des ressources.

# 2.3.3. Synthèse au niveau transfert de registres

La synthèse RTL traduit une description de niveau transfert de registres, composée généralement d'une partie contrôle et une partie chemin de données, en une description au niveau porte. Elle transforme la spécification d'un circuit en un ensemble d'équations logiques en effectuant, elle aussi, une allocation de ressources [3]. Les opérations effectuées sur le contrôleur décrit par une machine d'états, pour une implémentation en terme d'architecture, sont l'affectation d'états (state encoding), la minimisation d'états, etc. Les opérations effectuées sur la partie chemin de données concernent le partage de ressources et le retiming [1].

# 2.3.4. Synthèse logique

Les outils de synthèse logique prennent en entrée une description sous forme de blocs logiques interconnectés. Le but est d'optimiser les blocs logiques en terme de surface du circuit généré [1,7]. Une fois les équations optimisées, celles-ci sont décomposées sur la bibliothèque de composants technologiques dont le concepteur dispose pour l'implémentation. Cette étape de recouvrement ne modifie pas la structure des équations, mais choisit un ensemble optimal de portes pour minimiser le ou les critères d'optimisation.

# 2.3.5. Synthèse physique

La synthèse physique consiste à générer les motifs géométriques des masques de fabrication des circuits. Cette étape de placement et de routage des descriptions des architectures résultantes sur le silicium termine le flot de conception.

# 2.4. Langages de description