## République Algérienne Démocratique Et Populaire Ministère de l'enseignement supérieur et de la recherche scientifique

## Université colonel HADJ LAKHDAR –BATNA-Faculté des sciences de l'ingénieur Département d'informatique

## Mémoire

présenté

pour obtenir le grade de Magistère en informatique

par

## Malika Bachir

Spécialité : Système d'Information et de Communication (SIC)

## **Titre**

## Tolérance aux fautes des systèmes temps-réel embarqués basée sur la redondance

Encadreur : Dr Zidani Abdelmadjid

Co-Encadreur : Dr Kalla Hamoudi

## Composition du jury :

| Dr | Mohammed Benmohammed (prof.) | Président     | Université de Constantine |

|----|------------------------------|---------------|---------------------------|

| Dr | Belami Azzedine (MCA)        | Examinateur   | Université de Batna       |

| Dr | Belattar Brahim (MCA)        | Examinateur   | Université de Batna       |

| Dr | Zidani Abdelmadjid (MCA)     | Rapporteur    | Université de Batna       |

| Dr | Kalla Hamoudi (MCB)          | Co-Rapporteur | Université de Batna       |

## Table des matières

| Liste des figures  |                                                                                     | ۰۰۰۰۰۰۰۰۱ |

|--------------------|-------------------------------------------------------------------------------------|-----------|

| Liste des tableaux |                                                                                     | v         |

| Chapitre 1         | Introduction générale                                                               |           |

| 1.1.Problématique  | e générale                                                                          |           |

| 1.2.Apport du mén  | noire                                                                               | 9         |

| 1.2.1Méthodo       | logie AAA-FAULT <sup>t.ind</sup>                                                    | 9         |

| 1.2.2Méthodo       | logie AAA-FAULT <sup>t.dep</sup>                                                    | 9         |

| 1.3.Plan du mémo   | ire                                                                                 | 10        |

| Chapitre 2         | Introduction à l'ordonnancement dans les système<br>distribués temps réel embarqués | S         |

| 2.1.Définitions    |                                                                                     | 1         |

| 2.1.1.Système      | réactif et système temps réel                                                       | 1         |

| 2.1.2.Système      | distribué et système embarqué                                                       | 15        |

| 2.2.Spécifications | des systèmes distribués temps réel embarqués                                        | 16        |

| 2.2.1.Spécific     | ation algorithmique                                                                 | 16        |

| 2.2.2.Spécific     | ation matérielle                                                                    | 17        |

| 2.2.3.Contrair     | ites temporelles et d'embarquabilités                                               | 18        |

| 2.3.Problème de d  | istribution et d'ordonnancement temps réel                                          | 19        |

| 2.3.1.Termino      | logies                                                                              | 19        |

| 2.3.2.Présenta     | tion du problème de distribution/ordonnancement                                     | 20        |

| 2.4.Classes d'algo | rithmes de distribution et d'ordonnancement temps réel                              | 20        |

| 2.4.1.Algorith     | mes hors-ligne et enligne                                                           | 21        |

| 2.4.2.Algorith     | mes exactes et approchés                                                            | 21        |

| 2.5.Algorithme de  | distribution et d'ordonnancement de SYNDEX                                          | 2         |

| 2.5.1.Spécific     | ation de l'Algorithme de distribution/ordonnancement de SynDEx                      | 22        |

| 2.5.2.Présenta     | tion de l'algorithme de distribution et d'ordonnancement de SynDEx                  | 23        |

| 2.6 Conclusion     |                                                                                     | 26        |

Table des matières iv

| Chapitre 3 | Tolérance aux fautes dans les systèmes distribués temps |

|------------|---------------------------------------------------------|

|            | réel embarqués                                          |

| 3.1.Introduction    |                                                            | 27              |

|---------------------|------------------------------------------------------------|-----------------|

| 3.2.Terminologies   |                                                            | 28              |

| 3.2.1.Degré de      | e permanence des fautes                                    | 30              |

| 3.2.2.Hypothè       | ses de défaillances (Classes de défaillances)              | 31              |

| 3.2.3.Techniqu      | ues de tolérance aux fautes                                | 32              |

| 3.2.4.Algorith      | mes de la tolérance aux fautes                             | 33              |

| 3.2.5.Problème      | e de distribution et d'ordonnancement temps réel et toléra | nt aux fautes36 |

| 3.3.Conclusion      |                                                            | 37              |

| Chapitre 4          | Description du problème                                    |                 |

| 4.1.Introduction    |                                                            | 38              |

| 4.2.Classification  | des machines                                               | 38              |

| 4.2.1.Traiteme      | ent (séquenceur)                                           | 39              |

| 4.2.2.Mémoire       | 2                                                          | 40              |

| 4.2.3.Commur        | nication                                                   | 40              |

| 4.3.Modèle d' arch  | nitecture                                                  | 42              |

| 4.3.1.Architec      | ture à liaisons point à point                              | 45              |

| 4.3.2.Architec      | ture à liaisons bus                                        | 46              |

| 4.4.Modèle d'algor  | rithme                                                     | 47              |

| 4.5.Modèle d'impl   | antation                                                   | 49              |

| 4.6.Conclusion      |                                                            | 52              |

| Chapitre 5          | Etat de l'Art                                              |                 |

| 5.1.Introduction    |                                                            | 53              |

| 5.2.Stratégies de r | éplication                                                 | 54              |

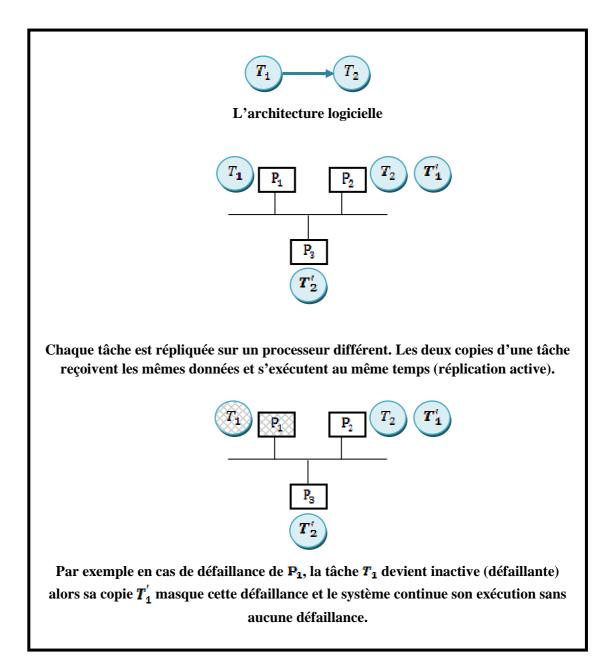

| 5.2.1.Réplicati     | ion active                                                 | 54              |

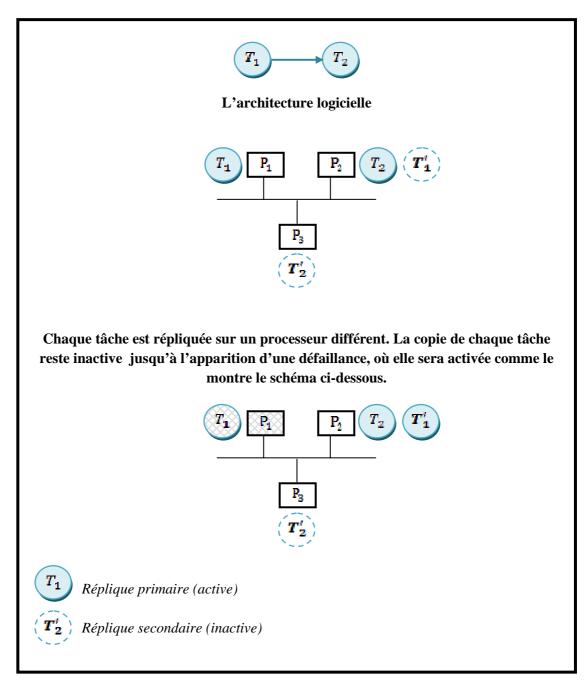

| 5.2.2.Réplicati     | ion passive                                                | 56              |

| 5.2.3.Réplicati     | ion semi-active (hybride)                                  | 59              |

| 5.3.Conclusion      |                                                            | 61              |

# Chapitre 6 Méthodologies proposées pour des architectures à liaison bus

| 6.1.Introduction                                                                                                                                                                                                                                                                                                                                                     | 62                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 6.2. Présentation de l'algorithme de distribution/ordonnancement tolérant aux fau                                                                                                                                                                                                                                                                                    | utes des            |

| tâches indépendantes AAA-FAULT <sup>t.ind</sup>                                                                                                                                                                                                                                                                                                                      | 64                  |

| 6.2.1.Modèle de fautes                                                                                                                                                                                                                                                                                                                                               | 64                  |

| 6.2.2.Données du problème                                                                                                                                                                                                                                                                                                                                            | 64                  |

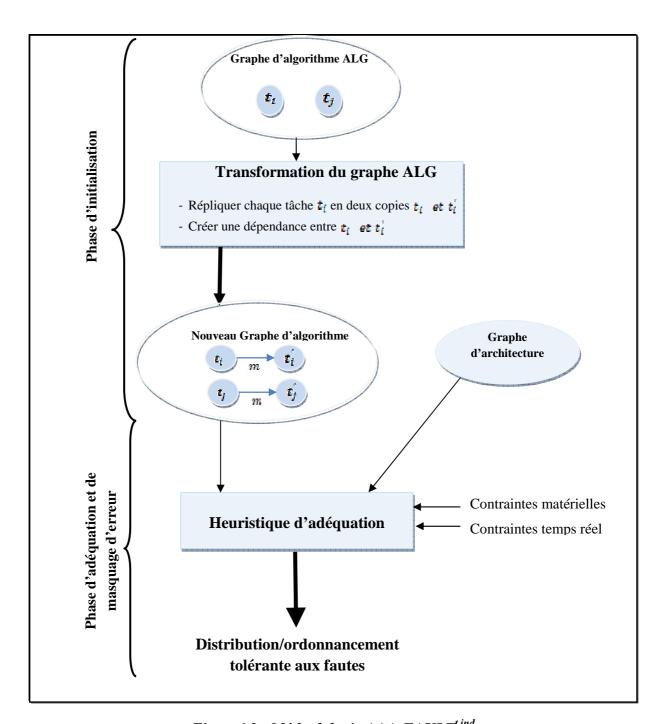

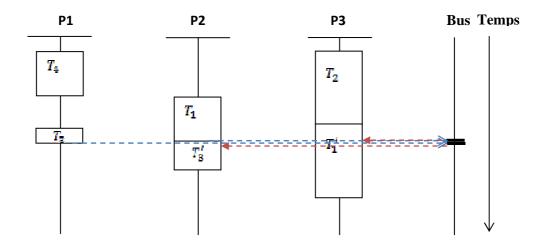

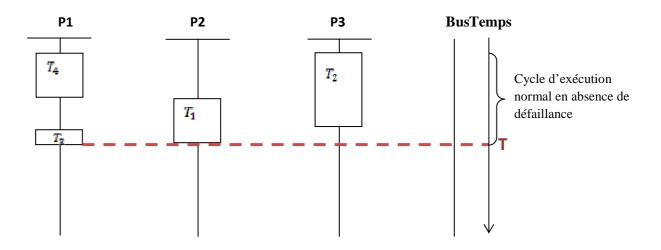

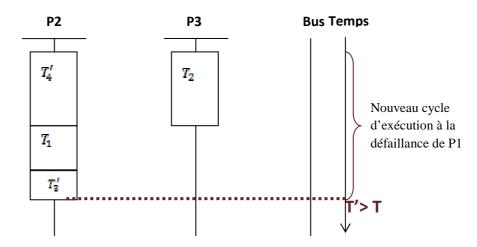

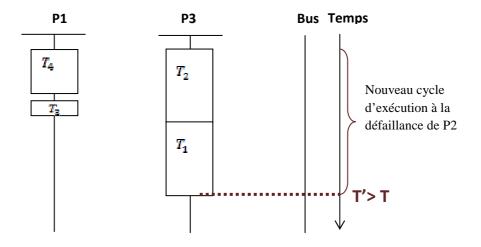

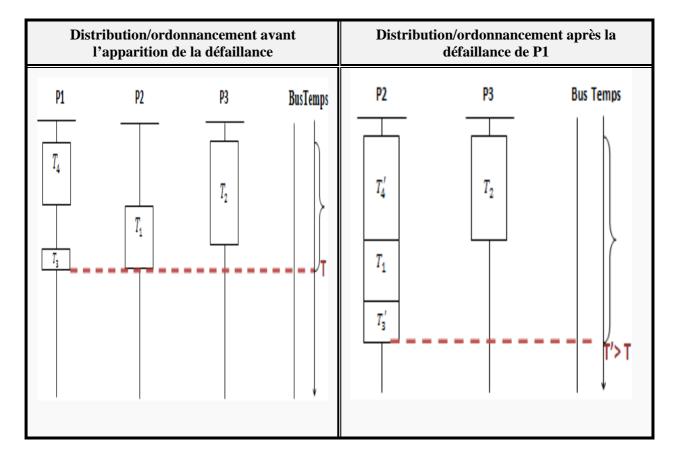

| 6.2.3.Principe général de la méthodologie AAA-FAULT <sup>t.ind</sup>                                                                                                                                                                                                                                                                                                 | 65                  |

| 6.3. Présentation de l'algorithme de distribution/ordonnancement tolérant aux fau                                                                                                                                                                                                                                                                                    | utes des            |

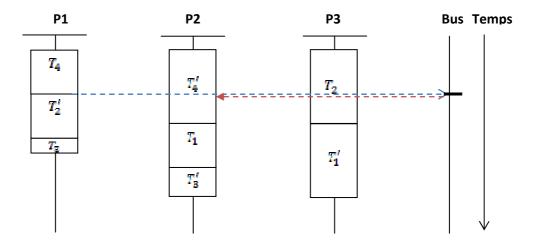

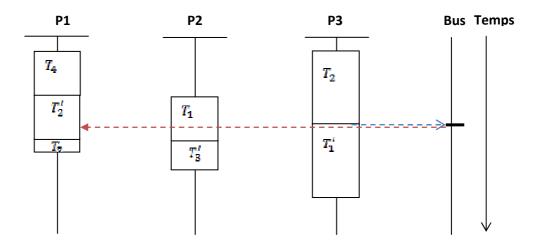

| tâches dépendantes AAA-FAULT <sup>t.dep</sup>                                                                                                                                                                                                                                                                                                                        | 77                  |

| 6.3.1.Modèle de fautes                                                                                                                                                                                                                                                                                                                                               | 77                  |

| 6.3.2.Données du problème                                                                                                                                                                                                                                                                                                                                            | 77                  |

| 6.3.3.Principe général de la méthodologie AAA-FAULT <sup>t.dep</sup>                                                                                                                                                                                                                                                                                                 | 78                  |

| 6.4.Prédiction du comportement temps réel                                                                                                                                                                                                                                                                                                                            | 89                  |

| 6.5.Conclusion                                                                                                                                                                                                                                                                                                                                                       | 89                  |

| Chapitre 7 Evaluation de la méthodologie AAA-FAULT <sup>t.</sup>                                                                                                                                                                                                                                                                                                     | dep                 |

|                                                                                                                                                                                                                                                                                                                                                                      |                     |

| Chapitre 7 Evaluation de la méthodologie AAA-FAULT <sup>t.</sup> 7.1.Introduction                                                                                                                                                                                                                                                                                    | 90                  |

| 7.1.Introduction                                                                                                                                                                                                                                                                                                                                                     | 90<br>90            |

| 7.1.Introduction                                                                                                                                                                                                                                                                                                                                                     | 90<br>90<br>91      |

| 7.1.Introduction                                                                                                                                                                                                                                                                                                                                                     | 90<br>90<br>91      |

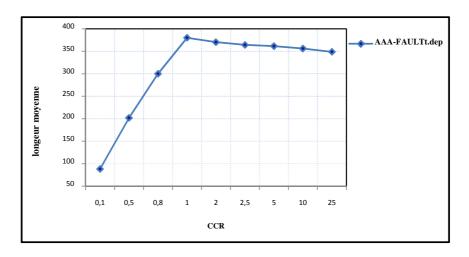

| <ul> <li>7.1.Introduction</li> <li>7.2.Paramètres d'évaluation</li> <li>7.3.Les résultats</li> <li>7.3.1. Effet du rapport entre le temps moyen de communication et le temps moyer</li> </ul>                                                                                                                                                                        | 90<br>90<br>91<br>n |

| 7.1.Introduction  7.2.Paramètres d'évaluation  7.3.Les résultats  7.3.1. Effet du rapport entre le temps moyen de communication et le temps moyer d'exécution sur AAA-FAULT <sup>t.dep</sup>                                                                                                                                                                         | 90<br>91<br>n<br>91 |

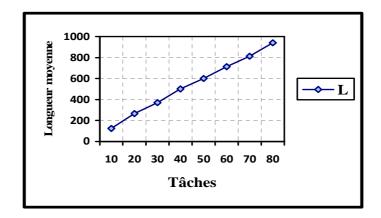

| 7.1.Introduction 7.2.Paramètres d'évaluation 7.3.Les résultats 7.3.1. Effet du rapport entre le temps moyen de communication et le temps moyer d'exécution sur AAA-FAULT <sup>t.dep</sup> 7.3.2. Effet du nombre de tâches sur AAA-FAULT <sup>t.dep</sup>                                                                                                            | 9091 n919191        |

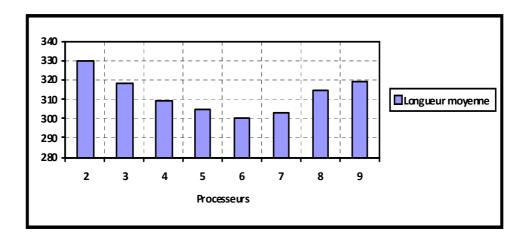

| 7.1.Introduction                                                                                                                                                                                                                                                                                                                                                     | 9091919191          |

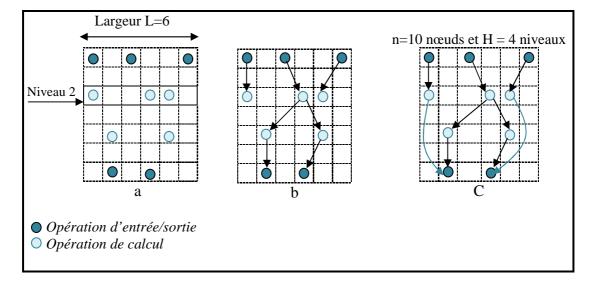

| 7.1.Introduction 7.2.Paramètres d'évaluation 7.3.Les résultats 7.3.1. Effet du rapport entre le temps moyen de communication et le temps moyer d'exécution sur AAA-FAULT <sup>t.dep</sup> 7.3.2. Effet du nombre de tâches sur AAA-FAULT <sup>t.dep</sup> 7.3.3. Effet du nombre de processeurs sur AAA-FAULT <sup>t.dep</sup> 7.4.Générateur de graphe d'algorithme | 9091919191          |

| 7.1.Introduction 7.2.Paramètres d'évaluation 7.3.Les résultats 7.3.1. Effet du rapport entre le temps moyen de communication et le temps moyer d'exécution sur AAA-FAULT <sup>t.dep</sup> 7.3.2. Effet du nombre de tâches sur AAA-FAULT <sup>t.dep</sup> 7.3.3. Effet du nombre de processeurs sur AAA-FAULT <sup>t.dep</sup> 7.4.Générateur de graphe d'algorithme | 9091 n91919293      |

# Liste des figures

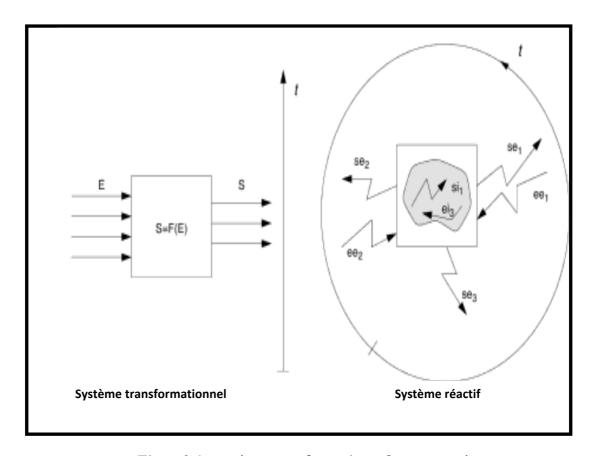

| 2.1 | Système transformationnel versus système réactif               | 12 |

|-----|----------------------------------------------------------------|----|

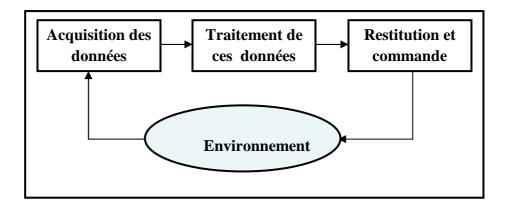

| 2.2 | Schéma d'un système temps réel                                 | 13 |

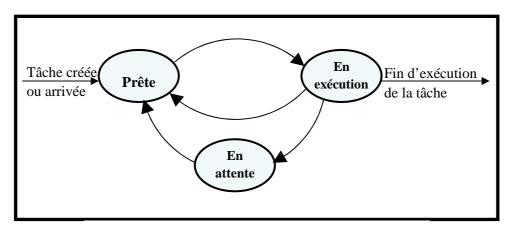

| 2.3 | Etats d'une tâche                                              | 14 |

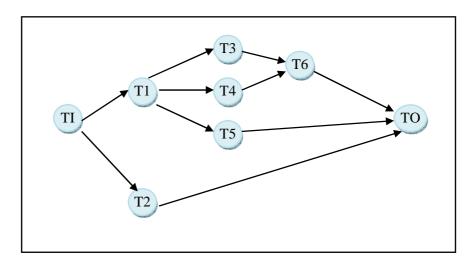

| 2.4 | Exemple d'architecture logicielle                              | 17 |

| 2.5 | Exemple d'une architecture distribuée                          | 18 |

| 3.1 | Arbre des systèmes sûrs de fonctionnement                      | 28 |

| 3.2 | Classes de fautes                                              | 29 |

| 3.3 | Relation entre faute, erreur et défaillance                    | 30 |

|     | Couverture entre hypothèses de défaillances                    |    |

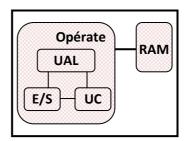

| 4.1 | Exemple d'un processeur                                        | 43 |

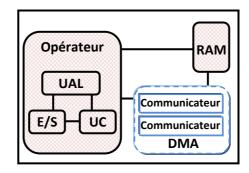

| 4.2 | Exemple d'un processeur doté d'un DMA                          | 44 |

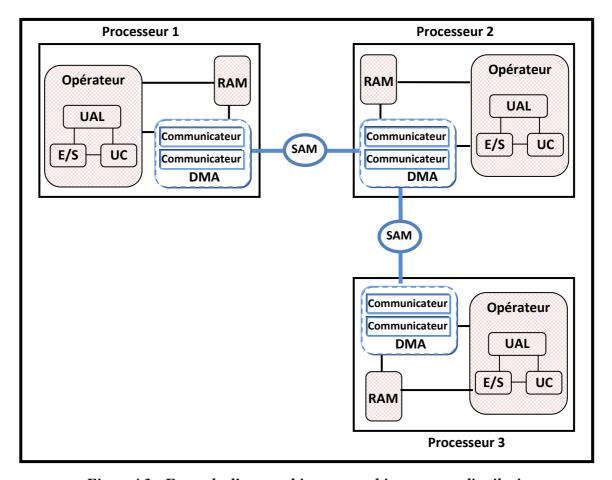

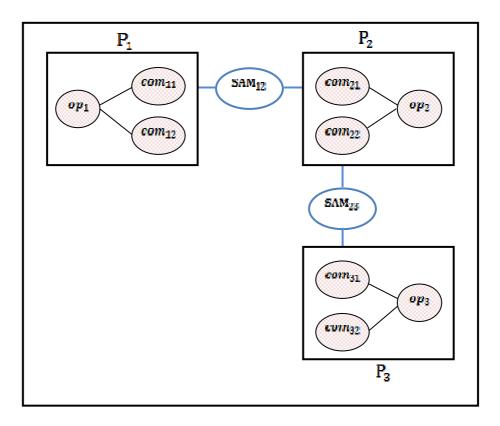

| 4.3 | Exemple d'une architecture multiprocesseur distribuée          | 44 |

| 4.4 | Exemple d'une architecture à liaisons point à point            | 45 |

| 4.5 | Exemple d'une architecture à liaisons bus                      | 46 |

| 4.6 | Communication intra-processeurs                                | 47 |

| 4.7 | Communication inter-processeurs                                | 47 |

| 4.8 | Exemple d'un graphe d'algorithme                               | 48 |

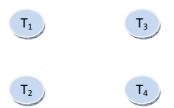

| 4.9 | Exemple d'un graphe d'algorithme sans dépendances de données   | 48 |

| 5.1 | Exemple de la réplication active                               | 55 |

| 5.2 | Exemple de la réplication passive                              | 58 |

| 6.1 | Architecture liaison à bus                                     | 64 |

| 6.2 | Exemple d'un graphe d'algorithme avec tâches indépendantes     | 65 |

| 6.3 | Méthodologie AAA-FAULT <sup>t.ind</sup>                        | 68 |

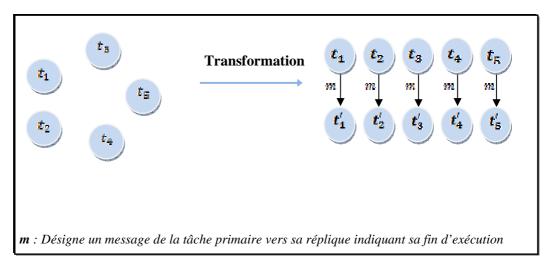

| 6.4 | Exemple de transformation d'un graphe d'algorithme             | 69 |

|     | Exemple d'un graphe d'algorithme avec tâches dépendantes       |    |

| 6.6 | Méthodologie AAA-FAULT <sup>t.dep</sup>                        | 81 |

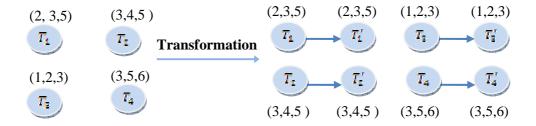

|     | Exemple de transformation d'un graphe flot de données          |    |

| 7.1 | Effet de la réplication passive pour P = 6 et N = 50           | 91 |

| 7.2 | Effet de N sur AAA-FAULTt.dep et AAA pour p=5 et CCR=2         | 92 |

| 7.3 | Effet du nombre de processeurs sur le surcoût pour N= 40 CCR=1 | 92 |

| 7.4 | Etapes de génération aléatoire d'un graphe d'algorithme        | 93 |

## Liste des tableaux

| 4.1 | Durée d'exécution des tâches sur les processeurs | 51 |

|-----|--------------------------------------------------|----|

| 4.2 | Durée de transfert des données entre les tâches  | 51 |

## Chapitre 1

## Introduction générale

## 1.1. Problématique générale

Les systèmes *temps réel embarqués* ont depuis toujours acquis une importante place dans le développement des systèmes informatiques, ils sont de plus en plus utilisés dans divers domaines applicatifs importants comme les véhicules (automobiles, robots, avions, satellites, bateaux) et les systèmes de contrôle de processus industriels. Pour répondre aux nombreuses demandes de traitement, ils sont généralement composés de plusieurs processeurs spécialisés et *distribués* (interconnectés par un réseau). Une des caractéristiques importantes de ces systèmes est d'être réactif, un système réactif est un système qui réagit continûment à des stimuli externes d'un environnement à la vitesse imposée par cet environnement (la régulation de niveau d'eau dans un réservoir est un exemple). Il reçoit ces stimuli par l'intermédiaire de capteurs, il les traite en effectuant un certain nombre d'opérations et produit, grâce à des actionneurs, des sorties utilisables par l'environnement, appelées réactions.

Une application temps-réel effectue des fonctions de contrôle et de pilotage. Chaque fonctionnalité est assumée par une *tâche temps-réel*. Certaines fonctions sont critiques et ne peuvent pas être retardées, c.-à-d. que les tâches correspondantes doivent impérativement avoir terminé leur traitement sous un délai donné, à partir de leur date de réveil. Dans le cas contraire, les résultats produits sont faux et la tâche est considérée être invalide. De telles tâches sont dites *critiques*. Les systèmes temps réel embarqués sont des systèmes de traitement dont la validité est conditionnée non seulement par la correction des résultats mais surtout par les dates auxquelles ceux-ci sont délivrés. En effet, ces systèmes

sont essentiellement caractérisés par des *contraintes de temps* sur les actions à entreprendre, qu'il faut respecter de manière plus ou moins critique.

Grand nombre de systèmes distribués temps réel et embarqués, tels que l'aéronautique et le secteur militaire, réalisent des tâches complexes et critiques ce qui les rend plus sensibles aux fautes, ils sont soumis à de fortes contraintes en terme de temps et de fiabilité, si elles ne sont pas respectées elles peuvent conduire à une défaillance grave qui peut engendrer des conséquences catastrophiques (perte d'argent, de temps ou pire de vies humaines). La solution de distribution et d'ordonnancement temps réel s'impose afin d'assurer le respect de ces contraintes temporelles. L'ordonnancement consiste à organiser dans le temps la réalisation des tâches, compte tenu des contraintes temporelles (délais, contraintes d'enchaînement) et des contraintes portant sur la disponibilité des ressources requises. Puisque la présence de certaines fautes qu'elles soient matérielles ou logicielles, accidentelles ou intentionnelles est inévitable, ce type de systèmes doit être sûr de fonctionnement. La sûreté de fonctionnement d'un système informatique est définie comme la propriété qui permet à ses utilisateurs de placer une confiance justifiée dans le service qu'il délivre [21]. Pour assurer la sûreté de fonctionnement des systèmes temps réel critiques plusieurs méthodes sont utilisées dans la littérature [2, 21], parmi plusieurs autres on trouve la technique de la tolérance aux fautes qui est l'objet de ce mémoire. La tolérance aux fautes est définie par la capacité du système de se conformer à ses spécifications en dépit de présence des fautes dans n'importe lequel de ses composants (logiciels ou matériels). La redondance des composants matériels ou logiciels est la technique la plus efficace utilisée pour assurer la tolérance aux fautes.

La croissance continue de la complexité des processeurs et l'arrivée de nouvelles technologies indiquent la persistance du problème des fautes des processeurs, qui peuvent devenir pire dans l'avenir [1], donc ce mémoire est consacré à l'étude du problème de la tolérance aux fautes des processeurs dans les systèmes temps réel embarqués dans un environnement distribué. L'architecture matérielle de ces systèmes est composée de plusieurs calculateurs, capteurs et actionneurs. Ces composants sont reliés par un réseau de communication (dans notre cas, un bus). Dans les systèmes embarqués, le nombre de ces éléments est réduit au strict minimum pour satisfaire les contraintes de coût, de consommation électrique, de taille, ...etc.

Pour réaliser des systèmes temps réel embarqués tolérants aux fautes dans un environnement réparti, nous cherchons plus particulièrement à résoudre un problème NP-difficile appelé problème de la distribution/ordonnancement temps réel tolérant aux fautes et *prédictif*. Nous tenons à proposer des techniques qui permettent de placer et d'ordonnancer les composants logiciels (tâches) sur les composants matériels tout en satisfaisant les contraintes temporelles, les contraintes de distribution et les contraintes de tolérance aux fautes.

• Les contraintes temporelles consistent à définir une limite ou une borne de l'exécution de l'algorithme sur le matériel.

- Les contraintes de distribution consistent à définir une relation d'exclusion entre certains composants matériels et certains composants logiciels (par exemple, une telle tâche ne peut pas s'exécuter sur tel processeur).

- Les contraintes de tolérance aux fautes définissent des hypothèses sur le nombre maximal de fautes des processeurs que le système doit tolérer.

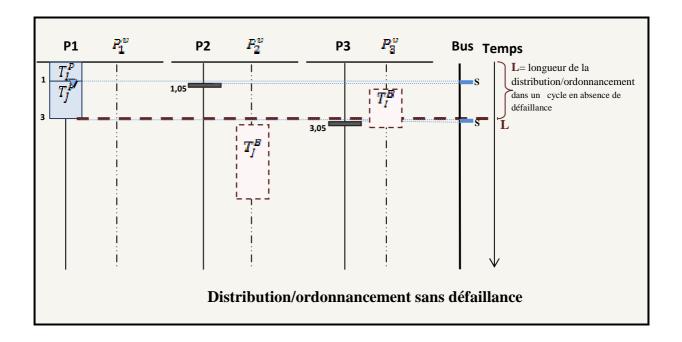

En fin, la distribution/ordonnancement doit être prédictive ce qui signifie qu'il est possible de déterminer, avant la mise en exploitation du système, si les contraintes temps réel sont respectées ou non en présence et en absence de fautes.

## 1.2. Apport du mémoire

Dans ce mémoire, nous proposons deux heuristiques, basées sur la méthodologie AAA implantée dans SynDEx, qui permettent la réalisation des systèmes répartis temps réel et embarqués sûrs de fonctionnement en optant à la technique de la tolérance aux fautes des composants matériels et plus particulièrement les processeurs. Vu que les systèmes embarqués exigent certaines caractéristiques comme : la taille, le coût, le poids, la consommation électrique qui doivent être réduits au minimum, nous nous sommes intéressés uniquement aux *solutions logicielles* basées sur la redondance des *composants logiciels* pour assurer la tolérance aux fautes. Nous avons considéré le cas le plus simple qui est les fautes permanentes d'un seul processeur dans un système silence sur défaillance (ou bien fonctionne, et donne un résultat correct délivré à temps ou bien il est en panne, et ne fait rien).

## 1.2.1 Méthodologie AAA-FAULT<sup>t.ind</sup>

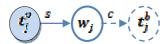

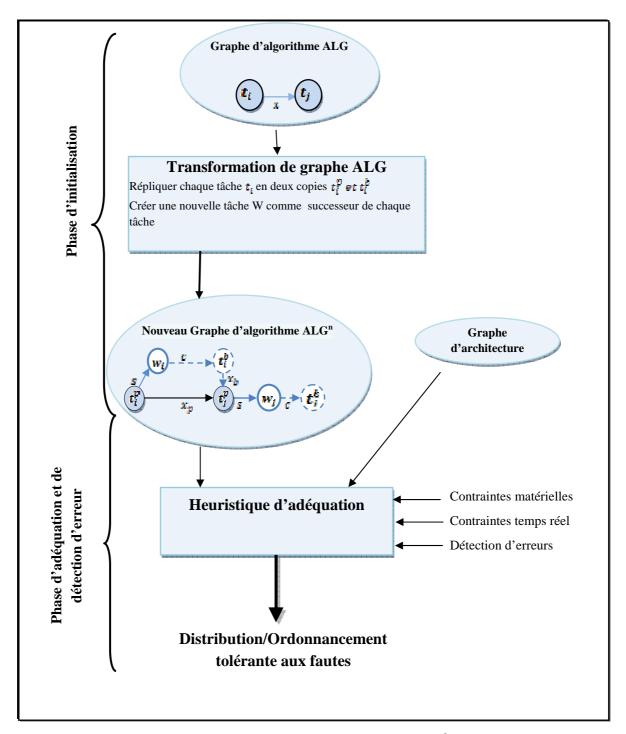

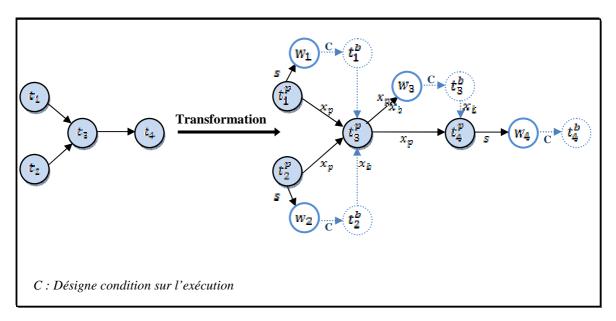

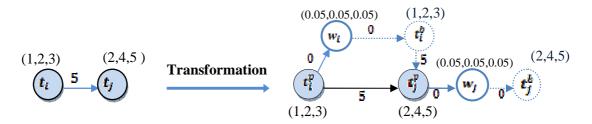

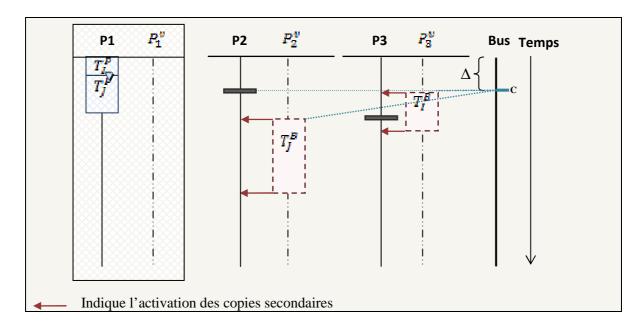

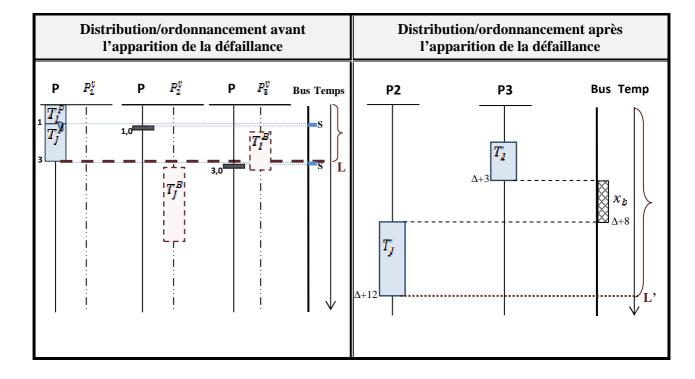

Cette première méthodologie proposée consiste à générer automatiquement une distribution et un ordonnancement d'une architecture logicielle composée de tâches indépendantes (pas de communication entre elles) sur une architecture matérielle distribuée et hétérogène munie d'un bus de communication (liaison multipoint). La tolérance aux fautes est assurée par le principe de la redondance *active* des composants logiciels. Elle permet de tolérer hors-ligne une ou plusieurs fautes permanentes d'un seul processeur en deux phases. La première phase consiste à transformer le graphe d'algorithme non redondant en un nouveau graphe redondant avec des tâches dépendantes, alors que la deuxième consiste à générer une distribution/ordonnancement de ce nouveau graphe sur le graphe d'architecture matérielle, tout en garantissant que les contraintes citées précédemment soient respectées.

## 1.2.2 Méthodologie AAA-FAULT<sup>t.dep</sup>

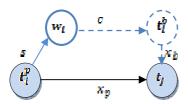

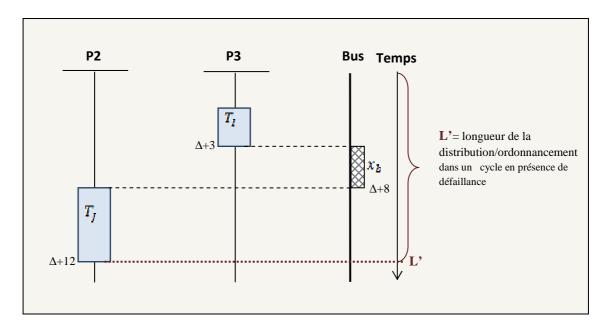

La méthodologie AAA-FAULT<sup>t.dep</sup> consiste à générer automatiquement une distribution et un ordonnancement temps réel d'une architecture logicielle composée de tâches dépendantes sur une architecture matérielle distribuée et hétérogène munie d'un bus de communication (liaison multipoint). La tolérance aux fautes est assurée par le principe de la redondance *passive* des composants logiciels. Elle permet de tolérer une ou plusieurs fautes permanentes d'un seul processeur en deux phases. La première phase consiste à

transformer le graphe d'algorithme non redondant en un nouveau graphe redondant. La deuxième phase, consiste à allouer spatialement et temporellement les composants logiciels de ce nouveau graphe d'algorithme avec redondance sur les composants matériels tout en garantissant le respect des mêmes contraintes. Dans cette heuristique l'implantation d'un mécanisme de détection d'erreurs est obligatoire.

## 1.3. Plan du mémoire

Le mémoire est divisé en sept chapitres :

- ➤ Le chapitre 1 est une introduction générale sur le problème de la tolérance aux fautes dans les systèmes distribués temps réel embarqués.

- Le chapitre 2 définit des notions sur ces systèmes et présente leurs caractéristiques et leurs spécifications. Par la suite, le problème de la conception de ces systèmes est exposé en présentant uniquement les principes des méthodologies basées sur la théorie d'ordonnancement. Le chapitre se termine par une présentation de l'algorithme de distribution et d'ordonnancement de SynDEx qui est la base de notre travail.

- ➤ Le chapitre 3 présente une technique qui assure la sûreté de fonctionnement et qui est l'objet de ce mémoire, c'est la tolérance aux fautes. Tout d'abord une introduction aux notions de base de la sûreté de fonctionnement est présentée, ensuite les terminologies liées à la tolérance aux fautes et ses phases de réalisation sont exposées. A la fin de ce chapitre, le problème de la génération de distribution/ordonnancement temps réel et tolérant aux fautes est présenté.

- ➤ Le chapitre 4 présente une modélisation du problème de la distribution et d'ordonnancement temps réel en décrivant le modèle d'algorithme, le modèle d'architecture et le modèle d'exécution. Le modèle d'algorithme décrit les spécifications des composants logiciels, le modèle d'architecture décrit les spécifications des composants matériels et le modèle d'exécution décrit le mode d'exécution des composants logiciels sur les composants matériels.

- ➤ Le chapitre 5 présente un état de l'art des méthodes existantes qui réalisent une génération d'une distribution et d'un ordonnancement temps réel tolérante aux fautes. Plusieurs travaux ont effectivement traité ce genre de problème, mais nous cherchons à réduire au mieux la longueur de la distribution/ordonnancement temps réel tolérante aux fautes.

- ➤ Dans le chapitre 6, nous proposons deux heuristiques pour traiter ce problème dans un environnement distribué et hétérogène muni d'un réseau de communication composé uniquement de liaison multipoint (bus).

- ➤ *Le chapitre* 7 présente quelques résultats donnés par la méthodologie AAA-FAULT<sup>t.dep</sup>.

Nous concluons enfin par un résumé des problèmes posés et traités dans ce mémoire et nous présentons les perspectives.

## Chapitre 2

# Introduction à l'ordonnancement dans les systèmes distribués temps réel embarqués

Ce chapitre a pour objectif de présenter le cadre de départ de notre travail. Nous introduisons dans un premier temps les principales caractéristiques des systèmes temps réel embarqués distribués. Nous présentons par la suite, le problème de distribution et d'ordonnancement dans ces systèmes en donnant tout d'abord les terminologies liées à ce problème, puis une classification des algorithmes d'ordonnancement pouvant le résoudre. Et enfin nous nous concentrons sur un algorithme de distribution et d'ordonnancement que nous exploitons dans ce travail.

## 2.1. Définitions

## 2.1.1. Système réactif et système temps réel

Selon la classification des systèmes informatiques introduits par D-Harel et A-Pnueli [6], un système est transformationnel, interactif, ou réactif.

**Définition 1 (système transformationnel) :** Le système transformationnel s'exécute avec des données en entrée et après un certain temps il termine en fournissant un résultat en sortie.

**Définition 2 (système interactif) :** Le système interactif réagit constamment avec son environnement mais à sa vitesse propre comme les systèmes d'exploitation.

Définition 3 (système réactif): Un système réactif est tout système de traitement de l'information qui répond continuellement à des stimuli externes d'un environnement à la

vitesse imposée par ce dernier. En d'autre terme, un système réactif réagit continuellement et instantanément à des événements ou stimuli qu'ils soient internes ou externes [5].

Figure 2.1 : système transformationnel versus système

Nous pouvons représenter un système réactif comme étant composé de :

- L'environnement à contrôler.

- Un système de contrôle qui représente le système d'exploitation au dessus duquel l'application sera exécutée.

- l'application.

L'introduction de contraintes de temps inhérentes à l'application en spécifiant des délais avec lesquels seront fournies les réponses aux stimuli, permet d'introduire la notion de système temps réel.

**Définition 4 (système temps réel) :** Est un système qui permet de réaliser certaines tâches ou fonctions en réagissant avec son environnement qui lui-même évolue avec le temps, il exploite des ressources limitées. La correction d'un système temps réel ne dépend pas seulement des valeurs des résultats produits, mais également des délais dans lesquels ces résultats sont réalisés.

En d'autre terme, un système est temps réel s'il est capable de respecter des échéances temporelles [5].

La figure 2.2 schématise le comportement du système temps réel.

Figure 2.2 : Schéma d'un système temps

En fonction du niveau de sévérité des contraintes temporelles qu'un système temps réel doit satisfaire, on considère usuellement deux grandes catégories :

- Système temps réel souple (ou système à contraintes relatives)

- Système temps réel dur (ou système à contraintes strictes)

## a) Système temps réel souple

Dans ces systèmes, un retard dans l'obtention du résultat réduit progressivement son intérêt (dégradation des performances), mais les pénalités ne sont pas dramatiques. L'application de distributeur de billets est un exemple sur ce type de système.

## b) Système temps réel dur

Dans ces systèmes, la réponse dans les délais est vitale. L'absence ou le retard d'une réponse est catastrophique, ainsi que celle erronée. Le système de contrôle d'avion, de freinage ABS et de détection de missile sont de bons exemples.

## Remarque:

Le plus souvent, les systèmes temps réel sont embarqués, c'est-à-dire, physiquement liés au processus contrôlé.

## Exemples de systèmes réactifs temps réel

- Contrôle des fonctions d'un véhicule automobile.

- Guidage d'une fusée.

- Simulation de vol.

- Contrôle d'une unité de production industrielle (usine chimique, traitement des centrales nucléaires).

- Contrôle des fonctions d'un satellite de télécommunication.

Dans un système temps réel, un processus est appelé tâche. Les états classiques d'une tâche et les transitions possibles entre eux sont donnés par la figure suivante :

Figure 2.3 : Etats d'une tâche

Une tâche temps réel est associée à des contraintes de temps et de ressources. Dans un système temps réel, les contraintes temporelles portent essentiellement sur les dates de début et de fin d'exécution des tâches. Les contraintes temporelles sont modélisées par les paramètres suivants [34] :

**Date de création** : c'est la date d'arrivée de la tâche au processeur (date de sa création ou éventuellement date à laquelle une tâche transférée par un autre processeur est reçue).

**Temps d'exécution**: c'est la durée d'exécution de la tâche (le temps entre la création d'une tâche et sa fin d'exécution). Il est déterminé par des simulations ou par une étude poussée du code source avant l'exécution.

**Echéance** : la date au plus tard à laquelle une tâche peut terminer son exécution.

Période : est le temps entre deux créations consécutives d'une tâche

*Date de début d'exécution* : la date à laquelle une tâche peut commencer son exécution. Certaines tâches sont dépendantes et ne peuvent commencer leurs exécutions que si les tâches qui les précèdent ont terminé.

En ce qui concerne la période, les tâches peuvent être classifiées comme tâches périodiques et tâches apériodiques. Les tâches périodiques se produisent à plusieurs reprises après une durée fixe de temps, tandis que les tâches apériodiques sont déclenchées par certains événements comprenant ceux externes au système. Les temps d'arrivée de ces événements ne sont pas connus à l'avance.

Les tâches sporadiques sont un cas particulier des tâches apériodiques où deux exemples successifs quelconques d'une tâche ont lieu séparément par un temps minimum.

En ce qui concerne les temps d'arrivée des tâches, les systèmes temps réel peuvent être classifiés dans les deux classes suivantes :

- Systèmes statiques: Sont ceux où les dates de début d'exécution de toutes les tâches sont connues avant l'exécution du système. Ils se composent typiquement des tâches périodiques.

- Systèmes dynamiques: Sont ceux où les tâches peuvent arriver au système pendant son fonctionnement (exécution) et les dates de début d'exécution ne sont pas connues à l'avance. Plus souvent, les systèmes dynamiques doivent considérer des tâches périodiques ou apériodiques produites par des événements externes.

Exactement comme dans un système d'exploitation, dans un système temps réel plusieurs tâches peuvent arriver en même temps. Le système doit décider quelle tâche doit s'exécuter d'abord. Cette décision dépend d'un algorithme appelé algorithme d'ordonnancement que nous allons voir en détails dans la suite de ce chapitre.

## 2.1.2. Système distribué et système embarqué

**Définition 5 (système distribué) :** Un système distribué est un ensemble d'ordinateurs indépendants, liés par un ensemble de moyens de communication comme la mémoire partagée, le bus et la liaison point-à-point qui apparait à l'utilisateur comme un système unique et cohérent. WWW, banques et système de fichier distribué sont des exemples parmi plusieurs autres de ce type de système.

Les systèmes distribués sont populaires pour plusieurs raisons :

- Accès distant : un même service peut être utilisé par plusieurs acteurs situés à des endroits différents.

- **Redondance :** des systèmes redondants permettent de pallier une faute matérielle ou de choisir le service équivalent avec le temps de réponse le plus court.

- **Performance :** la mise en commun de plusieurs unités de calcul permet d'effectuer des calculs parallélisables en des temps plus courts.

- **Confidentialité**: les données brutes ne sont pas disponibles partout, au même moment, seules certaines vues sont exportées.

**Définition 6 (système embarqué) :** Un système embarqué est une combinaison autonome de matériel et de logiciel (électronique plus informatique) dédié à réaliser généralement

une *tâche précise* en interaction avec son environnement et en respectant des contraintes souvent sévères tel que : consommation, poids, fiabilité, temps de réponse, coût, ...etc.

## **Remarque:**

Un système embarqué est souvent utilisé dans un environnement réactif soumit à des contraintes temps réel.

La conception des systèmes temps réel embarqués et distribués nécessite la description et l'expression des contraintes temps réel, la prédiction et l'estimation des temps de réponses et la sélection de l'architecture du matériel et du logiciel. Dans ce qui suit nous allons présenter ces spécifications.

## 2.2. Spécifications des systèmes distribués temps réel embarqués

La spécification des systèmes distribués temps réel et embarqués est réalisée en trois phases [1]: La spécification fonctionnelle, la spécification architecturale et la spécification des contraintes. La spécification fonctionnelle consiste à définir l'algorithme représentant les fonctionnalités du système, la spécification architecturale décrit le matériel sur lequel va s'exécuter l'algorithme et la spécification des contraintes consiste à attribuer des contraintes temporelles et matérielles à l'exécution de l'algorithme sur l'architecture.

## 2.2.1. Spécification algorithmique

Les fonctionnalités des systèmes temps réel embarqués combinent contrôle et traitement de données. Les fonctionnalités de traitement de données consistent à effectuer des calculs sur des données, alors que celles de contrôle consistent à mettre en séquence ces calculs [8]. L'algorithme représentant ces fonctionnalités est constitué de plusieurs composants logiciels où chaque composant peut être lui-même composé de plusieurs sous-composants et assure une fonctionnalité spécifique du système.

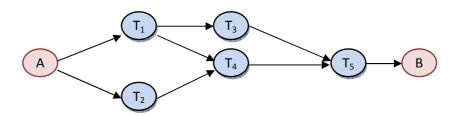

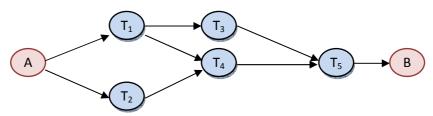

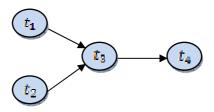

Dans ce mémoire, nous avons utilisé la spécification flot de données pour modéliser l'algorithme temps réel embarqué et distribué, où les nœuds sont les tâches de calcul de l'algorithme et les arcs sont les dépendances de données entre tâches. Une dépendance de données présentée par A→B, désigne que la tâche B ne peut s'exécuter que lorsque la tâche A termine son exécution ; C'est-à-dire B s'exécute lorsque ses données d'entrée sont présentées.

Une tâche sans prédécesseur (resp. sans successeur) représente une interface d'entrée, c'est-à-dire un capteur, (resp. une interface de sortie, c'est-à-dire un actionneur) avec l'environnement.

Le graphe présenté dans la page suivante montre un exemple de la modélisation de l'algorithme où les nœuds nommés Ti sont les tâches accomplies par le système, et les arcs entre ces nœuds sont les dépendances de données qui expriment un ordre partiel d'exécution sur les tâches.

Figure 2.4: Exemple d'architecture logicielle

## 2.2.2. Spécification matérielle

L'architecture matérielle consiste à spécifier le matériel qui doit être utilisé pour satisfaire la réalisation d'un système distribué temps réel embarqué. Dans les systèmes distribués, l'architecture matérielle est composée de plusieurs machines mono ou multiprocesseurs, de moyens de communication et de plusieurs capteurs et actionneurs.

La spécification de l'algorithme est très liée à la spécification du matériel à titre d'exemple, les contraintes temporelles(échéance, durée d'exécution, ...) des composants logiciels sont issues du type de matériel de calcul (ou de traitement) et de communications utilisées; ainsi par exemple, pour gérer les communications inter-processeur entre des composants logiciels dépendants placés sur des processeurs distincts, il est nécessaire de connaître le type du réseau de communication (bus, liaison point à point, mémoire partagée, ...). Pour cela, la spécification de l'architecture matérielle consiste à caractériser tous les composants de l'architecture et à choisir la topologie du réseau de communication.

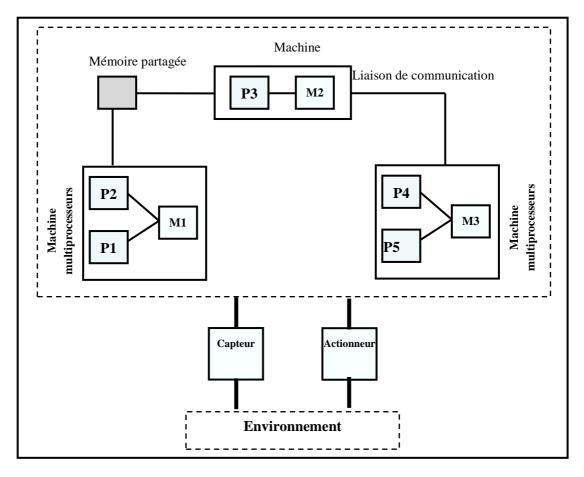

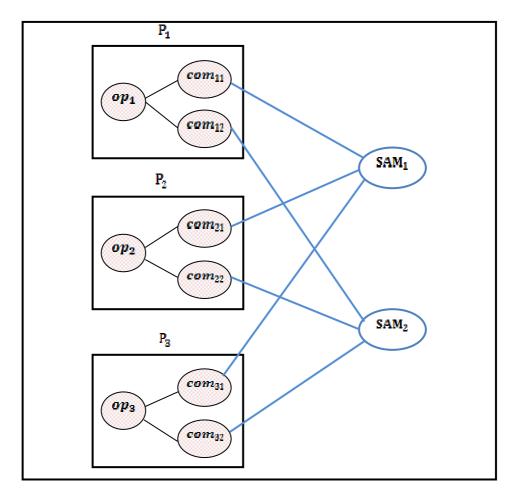

La Figure 2.5 [1], représente un exemple d'une architecture distribuée. L'architecture est composée de cinq processeurs (P1 à P5), de trois mémoires locales (M1 à M3), d'un capteur et d'un actionneur. Les processeurs communiquent entre eux via un réseau de communication composé d'une mémoire partagée et d'une liaison physique de communication.

Figure 2.5 : Exemple d'une architecture distribuée

## 2.2.3. Contraintes temporelles et d'embarquabilités

Le système temps réel embarqué permet, d'une part, de réaliser une spécification fonctionnelle conduisant à l'algorithme (ou l'ensemble d'algorithmes) qu'il faudra implanter sur une spécification matérielle et d'autre part de réaliser une spécification de contraintes. En ce qui concerne les contraintes temps réel, pour chaque composant logiciel de l'algorithme, on détermine une date de début d'exécution, et une date de fin d'exécution avant une échéance. Si ces dates ne sont pas respectées l'environnement risque de ne plus être contrôlé, ceci pouvant conduire à des conséquences catastrophiques. Les contraintes temporelles attribuées aux composants de l'algorithme peuvent être des mesures exactes, moyennes, ou majoritaires; ceci dépend des moyens utilisés pour obtenir ces mesures[1]. En plus de ces contraintes temps réel, le système est soumis à des contraintes technologiques d'embarquabilité (matérielles) et de coût, qui incitent à minimiser les ressources matérielles nécessaires à sa réalisation.

## 2.3. Problème de distribution et d'ordonnancement temps réel

Etant donné, que notre objectif dans ce travail est de proposer une nouvelle heuristique pour la résolution du problème de la tolérance aux fautes dans les systèmes répartis temps réel embarqué, l'algorithme proposé est un ensemble de tâches qui s'exécutent sur plusieurs processeurs et satisfaisant certaines contraintes temporelles d'où l'ordonnancement et la distribution de ces tâches sur les différents processeurs s'imposent.

Pour bien présenter notre objectif, nous commençons d'abord par l'introduction de certaines définitions et terminologies concernant le problème de la distribution et d'ordonnancement temps réel.

## 2.3.1. Terminologies

**Définition 7 (Ordonnancement temps réel):** Le problème d'ordonnancement met en relation des tâches à exécuter, des machines pour les exécuter et le temps [9]. Il détermine l'ordre d'exécution des tâches selon les critères (contraintes) spécifiés (échéance, temps de réponse, durée d'exécution, contraintes d'enchainement,...). L'ordonnancement est dit faisable s'il respecte toutes les contraintes temporelles.

**Définition 8 (Ordonnancement statique et dynamique):** dans l'ordonnancement statique, la séquence d'exécution des tâches est déterminée avant le début d'exécution de l'algorithme et ne change pas durant cette exécution, tandis que dans l'ordonnancement dynamique la séquence déterminée au préalable est mise à jour et réordonnancée en fonction des nouvelles tâches créées.

**Définition 9 (Allocation statique et dynamique) :** l'allocation statique consiste à placer un ensemble de tâches sur un réseau de processeurs avant leur exécution, en respectant et optimisant certains critères. Par contre l'allocation dynamique désigne le placement des tâches créées durant l'exécution.

**Définition 10 (Fonction de coût) :** Le rôle d'une fonction de coût est d'associer un poids à chaque composant logiciel, et ceci afin de calculer un ordre d'exécution entre ces composants.

**Définition 11 (Algorithme de distribution/ordonnancement temps réel):** c'est l'algorithme qui permet d'ordonnancer et de placer les tâches sur les processeurs en utilisant la fonction de coût dans un environnement distribué pour optimiser les performances du système temps réel.

#### Remarque:

Pour des raisons de lisibilité, parfois nous utilisons dans la suite de ce mémoire le terme « distribution/ordonnancement » au lieu de « distribution et ordonnancement temps réel »

## 2.3.2. Présentation du problème de distribution/ordonnancement

Le problème de distribution/ordonnancement consiste à trouver une allocation spatiale (distribution) et temporelle (ordonnancement) des composants logiciels sur l'architecture matérielle. Cette allocation doit être valide, c'est-à-dire elle satisfait les contraintes temporelles et matérielles. Ce problème devient d'ordre d'optimisation, lorsqu'il s'agit de rechercher une allocation valide qui doit optimiser en plus certains critères comme la réduction des coûts de communication. Si une telle solution existe, elle est dite optimale. Un problème d'optimisation peut être soit NP-difficile soit polynomiale [10].

On peut formaliser le problème de distribution et d'ordonnancement temps réel comme suit :

## **Problème 1<sup>1</sup>:** Etant donné:

- Une architecture matérielle hétérogène AMH composée de n composants matériels :  $AMH = \{P_1, \dots, P_n\}$

- Un algorithme ALG composé de m composants logiciels :  $ALG = \{T_1, \dots, T_m\}$

- Des coûts d'exécution C<sub>exe</sub> des composants d'ALG sur les composants d'AMH

- Des contraintes temps réel  $C_{tr}$  et matérielles  $C_{mt}$

- Un ensemble de critères à optimiser

Il s'agit de trouver une application A qui associe chaque composant  $T_i$  de ALG à un composant  $P_j$  de AMH, et qui lui assigne un ordre d'exécution  $\mathcal{O}_k$  sur son composant matériel :

$$A: ALG \rightarrow AMH$$

$$T_i \rightarrow A (T_i) = (P_j, O_k)$$

Qui doit satisfaire  $C_{mt}$  et  $C_{tr}$ , et optimiser les critères spécifiés.

# 2.4. Classes d'algorithmes de distribution et d'ordonnancement temps réel

La résolution d'un problème d'ordonnancement consiste à choisir puis à placer dans le temps des tâches sur les processeurs compte tenu de contraintes temporelles et matérielles (contraintes portant sur l'utilisation et la disponibilité des ressources requises par les tâches). Pour atteindre ce but plusieurs classes d'algorithmes d'ordonnancement se présentent dans la littérature, nous ne nous intéressons qu'aux deux grandes classes à savoir les algorithmes enligne/hors-ligne et les algorithmes exacts/approchés.

-

<sup>&</sup>lt;sup>1</sup> Problème de distribution et d'ordonnancement temps réel

## 2.4.1. Algorithmes hors-ligne et enligne

Selon les caractéristiques du système à réaliser et les contraintes temporelles qui sont connues avant l'exécution du système ou fixées au moment de son exécution, on trouve les algorithmes hors-ligne et les algorithmes enligne.

Dans les algorithmes hors-ligne, la séquence d'ordonnancement est pré-calculée avant l'exécution effective du système (ordonnancement statique) ainsi que l'allocation des tâches sur les processeurs est déterminée (allocation statique). Alors que dans les algorithmes enligne, Les décisions d'ordonnancement et le placement des tâches sur les processeurs sont prises au cours de l'exécution du système.

## 2.4.2. Algorithmes exacts et approchés

Lorsqu'on aborde la résolution d'un problème d'ordonnancement, on peut choisir entre deux grands types de stratégies, visant respectivement à l'optimalité des solutions par rapport à un ou plusieurs critères, ou plus simplement à leur admissibilité vis-à-vis des contraintes [10]. Une méthode utilisant un critère d'optimisation est exacte si elle garantit l'optimalité des solutions trouvées ; sinon elle est dite approchée, ou heuristique, lorsqu'on observe empiriquement qu'elle fournit de « bonnes » solutions.

Les algorithmes hors-ligne et enligne qui trouvent une solution optimale, si celle-ci existe, appartiennent à la classe des algorithmes exacts puisqu'ils renvoient toujours une solution optimale. Cependant, dans le cas général, ce problème est NP-difficile et la complexité est exponentielle. Trouver une solution optimale pour le problème de distribution/ordonnancement n'est pas usuellement une contrainte d'un système temps réel embarqué à contraintes strictes. C'est pourquoi, pour résoudre ce problème dans un temps polynomial, plusieurs heuristiques ont été développées dans la littérature pour chercher une solution valide et si possible proche de la solution optimale. Ces algorithmes de distribution et d'ordonnancement appartiennent à la classe des algorithmes approchés.

Parmi tous les algorithmes proposés dans la littérature, nous ne nous intéressons dans ce travail qu'aux algorithmes hors/ligne approchés basés sur celles de SynDEx.

## 2.5. Algorithme de distribution et d'ordonnancement de SynDEx

L'heuristique de distribution/ordonnancement implanté dans SynDEx<sup>2</sup> est un algorithme de type hors/ligne approché proposé dans sa première version en 1991 [11], ensuite il a été amélioré afin de pouvoir traiter des problèmes réalistes de types industriels où l'on cherche à distribuer des algorithmes de plusieurs centaines de composants logiciels sur quelques dizaines de processeurs et médias de communication.

21

<sup>&</sup>lt;sup>2</sup> SynDEx est un environnement graphique interactif de développement pour applications temps réel. http://www.syndex.org

# 2.5.1. Spécification de l'Algorithme de distribution/ordonnancement de SynDEx

Une application SynDEx est composée d'un graphe d'algorithme (définitions des tâches que l'application peut exécuter) et d'un graphe d'architecture (définitions d'un ensemble de processeurs reliés ensemble et circuits intégrés spécifiques). Exécuter une adéquation signifie l'exécution de l'heuristique cherchant l'implantation optimisée d'un algorithme donné sur une architecture donnée.

Dans le graphe d'algorithme, graphe flot de données, les sommets sont les tâches de l'algorithme et les arcs sont les dépendances de données entre ces tâches. Une tâche ne peut s'exécuter que lorsqu' elle reçoit ses données d'entrée. Elle consomme ses données et produit des données en sortie, qui sont ensuite utilisées par ses successeurs. Une tâche sans prédécesseur (resp. sans successeur) représente une interface d'entrée, c'est-à-dire un capteur, (resp. une interface de sortie, c'est-à dire un actionneur) avec l'environnement.

Le graphe d'architecture est spécifié par un graphe non orienté dans lequel les sommets désignent les processeurs et les mémoires, les arrêtes désignent les liaisons physiques entre mémoires et processeurs. Chaque processeur est composé d'une unité de calcul, d'une mémoire locale, et d'une ou plusieurs unités de communication pour communiquer avec les périphériques ou d'autres processeurs.

A chaque tâche  $T_i$  du graphe d'algorithme est associé un coût d'exécution  $C_{exe}(T_i, P_k)$  sur chaque processeur  $P_k$  du graphe d'architecture. Ce temps d'exécution désigne une borne supérieure (WCET) du temps d'exécution de la tâche sur chaque processeur, il est déterminé par le concepteur du système en utilisant des méthodes statiques ou dynamiques [12]. Puisque l'architecture est hétérogène, alors ces coûts d'exécutions peuvent être distincts pour un même composant logiciel du graphe d'algorithme. De plus, à chaque dépendance de données  $(T_i, T_j)$  de l'architecture logicielle est associé un coût de transfert de données  $C_{exe}(T_i, T_j, L_k)$  sur le lien de communication  $L_k$  de l'architecture matérielle.

Les contraintes matérielles sont spécifiées par l'association de la valeur 1 à  $C_{exe}(T_i, P_k)$ , ce qui signifie que la tâche  $T_i$  ne peut pas être implantée sur le processeur  $P_k$ . Enfin, une seule contrainte temps réel  $C_{ir}$  est prise en compte dans l'algorithme de distribution/ordonnancement, qui est la contrainte de la latence, c'est-à-dire que la longueur de la distribution/ordonnancement du graphe d'algorithme sur le graphe d'architecture doit être inférieure à un seuil défini par la latence.

# 2.5.2. Présentation de l'algorithme de distribution et d'ordonnancement de SynDEx

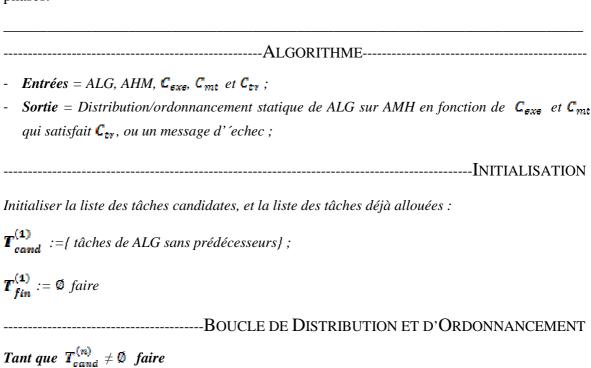

Le but principal de l'heuristique de distribution/ordonnancement de SynDEx est de chercher une allocation spatiale et temporelle du graphe d'algorithme ALG sur le graphe d'architecture AMH, tout en respectant les contraintes temps réel  $C_{tr}$ .

Tout d'abord, avant de présenter l'heuristique nous donnons les notations suivantes qui seront utilisées par cette heuristique et aussi dans le reste de ce travail :

$pred(T_i)$ : l'ensemble des tâches prédécesseurs de la tâche  $T_i$

$succ(T_i)$ : l'ensemble des tâches successeurs de la tâche  $T_i$

$C_{exe}(T_i, P_j)$ : Le coût d'exécution de  $T_i$  sur le processeur  $P_j$

$X^{(n)}$ : n désigne l'étape de l'heuristique, c'est-à-dire après avoir alloué la  $n^{i n}$  tâche; donc, X(n) désigne l'ensemble X à l'étape n de l'heuristique

$T_{\tt card}^{(n)}$ : représente la liste des tâches candidates ; une tâche de ALG est dite candidate si elle est implantable, c'est-à-dire que tous ses prédécesseurs sont déjà alloués

$T_{fin}^{(n)}$ : représente la liste des tâches déjà allouées

$St_{T_i,P_j}^{(n)}$ : représente la date de début au-plus-tôt de  $T_i$  sur  $P_j$ , depuis le début [13]

$\mathsf{st}_{T_i,P_j}^{(n)}$ : représente la date de début au-plus-tard de  $T_i$  sur  $P_j$ , depuis le début [13]

$\vec{\mathbf{st}}_{t\bar{t}}^{(m)}$ : représente la date de début au-plus-tard de  $T_t$ , depuis la fin [13]

L'heuristique de distribution/ordonnancement est un algorithme glouton [14] de type ordonnancement de liste, basé sur une fonction de coût appelée la pression d'ordonnancement dont l'objectif est de minimiser la longueur de la distribution/ordonnancement.

**Définition 12 (longueur d'une distribution/ordonnancement):** La longueur de la distribution/ordonnancement d'un graphe d'algorithme sur un graphe d'architecture, noté  $R^{(n)}$ , est la durée d'exécution de ce graphe d'algorithme sur ce graphe d'architecture, c'est-à-dire la date de terminaison du dernier processeur en exécution.

**Définition 13 (Pression d'ordonnancement):** La pression d'ordonnancement, notée  $\sigma_{Ti,Pj}^{(n)}$ , est une fonction de coût qui induit des priorités d'ordonnancement entre les opérations d'ALG. Elle mesure à la fois la marge d'ordonnancement F(n) et l'allongement P(n) de la longueur de la distribution/ordonnancement. Elle est calculée pour chaque tâche candidate  $T_i$  sur chaque processeur  $P_i$  par :

$$\sigma_{Ti,Pj}^{(n)} = P_{Ti,Pj}^{(n)} - F_{Ti,Pj}^{(n)}$$

(2-1)

**Définition 14 (Pénalité d'ordonnancement) :** La pénalité d'ordonnancement, notée  $P_{Ti,Pj}^{(n)}$ , est une fonction qui mesure l'allongement de la longueur de la distribution/ordonnancement  $R_{Ti,Pj}^{(n)}$  après avoir allouer  $T_i$  sur  $P_j$  à la  $n^{ième}$  étape de l'heuristique, en tenant compte des coûts de communication engendrés par l'allocation. Elle est définie par :

$$P_{Ti,Pj}^{(n)} = R_{Ti,Pj}^{(n)} - R^{(n-1)}$$

(2-2)

**Définition 15 (Flexibilité d'ordonnancement) :** La flexibilité d'ordonnancement, notée  $F_{T_i,P_j}^{\{n\}}$ , est une fonction qui mesure la marge d'ordonnancement de  $T_i$  sur  $P_j$  à la  $n^{i\`{e}me}$  étape de l'heuristique. Elle est définie par :

$$\mathbf{F}_{Ti,Pi}^{(n)} = st_{Ti,Pi}^{(n)} - St_{Ti,Pi}^{(n)}$$

(2-3)

En utilisant l'équation suivante [13] :

$$st_{Ti,Pj}^{(n)} = R_{Ti,Pj}^{(n)} - \overline{st}_{Ti}^{(n)}$$

(2-4)

et les équations (2.1), (2.2) et (2.3), la pression d'ordonnancement est définie par :

$$\sigma_{Ti,Pj}^{(n)} = St_{Ti,Pj}^{(n)} + \overline{St}_{Ti}^{(n)} - R^{(n-1)}$$

(2-5)

Avant de présenter l'algorithme de distribution et d'ordonnancement de SynDEx nous décrivons en premier ces grandes lignes, alors :

- L'exécution de l'algorithme est effectuée par plusieurs itérations; à chaque itération une liste des tâches candidates  $T_{cand}^{(n)}$  est établie.

- Pour chaque tâche  $T_i$  de  $T_{cand}^{(n)}$ , une pression d'ordonnancement  $\sigma_{Ti,Pj}^{(n)}$  sur chaque processeur  $P_j$  de AMH est calculée, puis le processeur  $(P_{best})$  qui minimise cette pression d'ordonnancement est sélectionné.

- Parmi les couples (T<sub>i</sub>, P<sub>best</sub>), celui qui maximise la pression d'ordonnancement est sélectionné (t<sub>best</sub>, P<sub>best</sub>). C'est-à-dire la tâche T<sub>best</sub> sera placée et ordonnancée sur le processeur P<sub>best</sub>.

- Ce processus d'allocation est répété pour toutes les tâches restantes, jusqu'à ce qu'il n'en reste plus.

L'heuristique de distribution/ordonnancement a donc la forme qui suit :

2.5.2. Présentation de l'algorithme de distribution et d'ordonnancement de SynDex

Fin tant que -----Fin de L'Algorithme

## 2.6. Conclusion

Nous avons présenté dans ce chapitre les terminologies liées à la distribution et à l'ordonnancement temps réel, ainsi que les algorithmes utilisés pour résoudre le problème d'ordonnancement dans les systèmes distribués temps réel et embarqués. Parmi la multitude des solutions proposées dans la littérature concernant le problème de distribution et d'ordonnancement temps réel hors-ligne, nous avons choisi de se baser dans le reste du mémoire sur l'algorithme de SynDEx pour des raisons de simplicité et d'efficacité. Des terminologies de base de la tolérance aux fautes vont être exposer dans le chapitre suivant.

## Chapitre 3

Tolérance aux fautes dans les systèmes distribués temps réel embarqués

## 3.1. Introduction

Dans les systèmes temps réel embarqués et distribués le respect des contraintes temporelles tout au long de la vie du système est crucial, il constitue une condition nécessaire mais pas suffisante pour le bon fonctionnement de ces systèmes puisque quelles que soient les précautions prises, l'occurrence de fautes est inévitable (erreur humaine, malveillance, vieillissement du matériel, catastrophe naturelle, etc.). Au vu des conséquences catastrophiques (perte d'argent, de temps ou pire de vies humaines) que pourrait entraîner une faute dans un système temps réel critique, la présence des techniques qui assurent la sureté de fonctionnement [2, 21] est vitale dans la conception de ces systèmes. La tolérance aux fautes est l'une des méthodes utilisées dans la littérature pour assurer la sureté de fonctionnement des systèmes temps réel embarqués et distribués ; elle permet la conception des systèmes qu'ils continuent à rendre le service attendu (éventuellement un service gradé) même en présence de fautes. Les systèmes temps réel critiques doivent ainsi couvrir une propriété importante des systèmes sûrs de fonctionnement qui est la *fiabilité*. La fiabilité est la probabilité pour qu'un système soit continûment en fonctionnement sur une période donnée (entre 0 et t).

Dans ce mémoire, nous nous intéressons uniquement au concept de la tolérance aux fautes, nous commençons tout d'abord par les notions de base de la sûreté de fonctionnement qui nous permettront de cerner plus précisément la tolérance aux fautes. Ensuite Nous présentons les terminologies liées à la tolérance aux fautes et ses phases de

réalisation. Nous reprenons pour cela la taxonomie développée, entre autres, par Jean-Claude Laprie, Brian Randell et Algirdas Avizienis, qui fait largement référence.

## 3.2. Terminologies

**Définition 16 (sûreté de fonctionnement) :** La sûreté de fonctionnement d'un système est définie comme la propriété qui permet à ses utilisateurs de placer une confiance justifiée dans la qualité du service qu'il leur délivre.

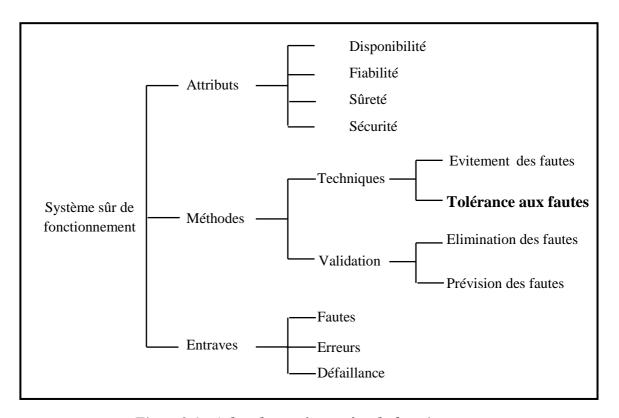

La figure 3.1 montre les notions de base reliées aux systèmes sûrs de fonctionnement

Figure 3.1 : Arbre des systèmes sûrs de fonctionnement

Dans ce qui suit nous présentons quelques définitions classiques utilisées dans le domaine de la tolérance aux fautes d'où faute, erreur et défaillance sont les trois termes importants.

**Définition 17 (Faute) :** Est un défaut qui se produit dans certain composant matériel ou logiciel, c'est toute cause (événement, action, circonstance) pouvant provoquer une erreur. La faute ne produit pas immédiatement des erreurs, elle reste dormante durant l'exécution du système, et elle sera activée par un évènement intentionnel ou accidentel.

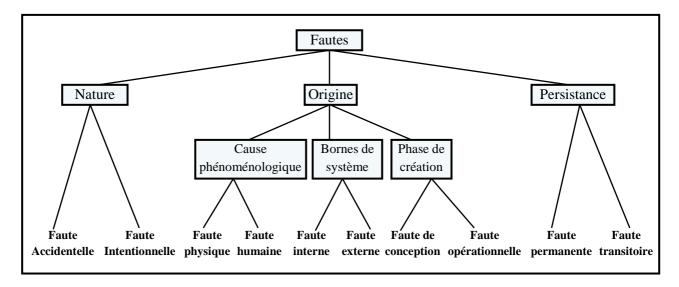

La faute peut être classifiée selon plusieurs critères qui sont récapitulés dans la figure 3.2 :

- par leur nature : accidentelle ou intentionnelle ;

- par leur origine : physique, humaine, interne, externe, conception, opérationnelle ;

- par leur persistance : permanente, transitoire ou intermittente.

*Exemples*: faute de programmation, malveillance, catastrophe naturelle, etc.

Figure 3.2 : Classes de fautes

**Définition 18 (Erreur) :** une erreur est une manifestation d'une faute activée, c'est un état (ou partie de l'état) du système susceptible de provoquer une défaillance.

**Exemple logiciel:** la valeur d'une table ne vérifie pas un invariant spécifié.

**Exemple matériel :** une connexion est coupée entre deux points qui devraient être reliés entre eux.

## Notes:

- Une erreur est latente tant qu'elle n'a pas provoqué de défaillance.

- Le temps entre l'apparition de l'état d'erreur et la défaillance est le délai de latence.

- plus le délai de latence est long, plus la recherche des causes d'une défaillance est difficile

**Définition 19 (Défaillance) :** Une défaillance d'un système est une déviation de celui-ci au service exigé, le système dans ce cas ne respect pas sa spécification. Les défaillances sont classifiées selon les critères suivants :

- par leur domaine :Défaillance de valeur et/ou défaillance temporelle ;

- par leur perception : par l'utilisateur ;

- par leurs conséquences : sur l'environnement.

Donc, la défaillance d'un système est la conséquence d'une erreur, et l'erreur est la conséquence d'une faute activée. En plus, étant donné qu'un système informatique est souvent composé de plusieurs sous-systèmes, la défaillance d'un sous-système peut créer et/ou activer une faute dans un autre sous-système ou dans le système lui même. La

relation entre ces trois termes faute, erreur et défaillance relativement aux sous systèmes du système peut être représentée par la figure suivante [1].

# Sous-système Sous-système Sous-système Fautes Erreur Défaillance Défaillance du système Erreur Fautes

Figure 3.3 : Relation entre faute, erreur et défaillance

Une défaillance dans un sous-système peut être vue comme une défaillance dans le système global.

Suivant les exigences fonctionnelles et temporelles d'un système temps réel embarqué et distribué, la défaillance de ce système peut être la conséquence de deux sources de fautes : fautes fonctionnelles (ou fautes de valeur) et fautes temporelles.

**Définition 20 (Faute fonctionnelle) :** La valeur délivrée par le système est fausse, c'est-à-dire qu'elle n'est pas conforme à sa spécification ou elle est en dehors de l'intervalle des valeurs attendues [1].

**Définition 21 (Faute temporelle) :** L'instant auquel la valeur est délivrée est en dehors de l'intervalle de temps spécifié. Dans ce cas, la valeur est considérée soit temporellement délivrée trop tôt, soit trop tard, soit infiniment tard (jamais délivrée). La faute temporelle dans le cas où la valeur n'est jamais délivrée est appelée « faute par omission » [1].

## 3.2.1. Degré de permanence des fautes

Les défaillances n'ont pas un comportement uniforme dans le temps, suivant la persistance temporelle d'une faute on distingue trois types de fautes: fautes permanentes, transitoires et intermittentes.

**Définition 22 (Faute permanente) :** Une faute permanente se caractérise par sa durée permanente, une fois activée, durant l'exploitation du système. Elle persiste donc indéfiniment (jusqu'à réparation) après son occurrence. Une faute de conception d'un composant matériel est un exemple typique de faute permanente.

**Définition 23 (Faute transitoire):** Une faute transitoire se caractérise par sa durée limitée, une fois activée, durant l'exploitation du système. Les fautes transitoires sont souvent observées dans les systèmes de communication, où la présence des radiations électromagnétiques peut corrompre les données envoyées sur une liaison physique de communication. Ceci provoque une faute transitoire qui ne dure que la période de la présence de ces radiations.

**Définition 24 (Faute intermittente) :** Une faute intermittente est une faute transitoire qui se reproduit sporadiquement.

## 3.2.2. Hypothèses de défaillances (Classes de défaillances)

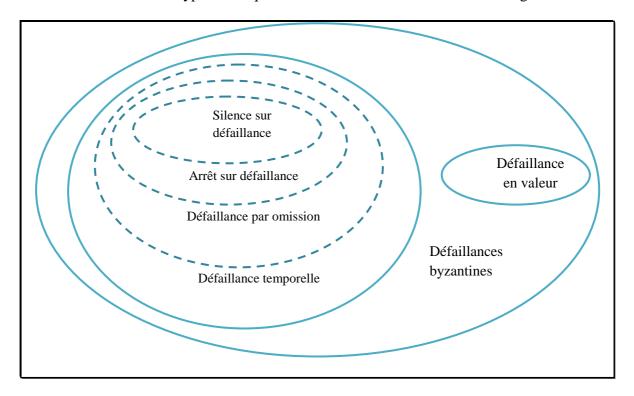

Il n'existe pas de méthodes de tolérance aux fautes valables dans l'absolu, seulement des méthodes adaptées à des hypothèses particulières d'occurrence de fautes. Ces hypothèses doivent donc être explicitement formulées après analyse soigneuse. Les hypothèses de défaillance des systèmes les plus utilisées dans la littérature [1] sont :

Définition 25 (Systèmes à défaillances en valeur): Ces systèmes supposent que les valeurs sont délivrées à temps et qu'ils défaillent uniquement si les valeurs délivrées sont fausses.

**Définition 26 (Systèmes à silence sur défaillances):** Un système à silence sur défaillances ou bien fonctionne et donne un résultat correct délivré à temps, ou bien il est en panne et ne fait rien (arrête de fonctionner).

Définition 27 (Systèmes à arrêt sur défaillances): Ce sont des systèmes à silence sur défaillances mais, avant que le système arrête son fonctionnement, il délivre un message aux autres systèmes indiquant son arrêt. Un exemple de ces systèmes est le processeur à arrêt sur défaillance [3]. Ce processeur est un composant physique qui en présence de fautes spécifiées dans ses hypothèses de défaillances génère un message indiquant son arrêt.

**Définition 28 (Systèmes à défaillances par omission):** Le système perd des messages entrants (omission en réception), sortants (omission en émission) ou les deux ; il n'y a pas d'autres déviations par rapport aux spécifications c.-à-d. dans ces systèmes les valeurs sont correctes, ils défaillent uniquement si la valeur n'est jamais délivrée.

**Définition 29** (**Systèmes à défaillances temporelles**): Les déviations par rapport aux spécifications concernent uniquement le temps (par exemple temps de réaction à un événement). Ces systèmes supposent que les valeurs délivrées sont correctes, et qu'ils défaillent uniquement si la valeur est temporellement délivrée trop tôt (en avance par rapport à sa plage de temps spécifiée) ou trop tard (en retard par rapport à sa plage de temps spécifiée).

Définition 30 (Systèmes à défaillances byzantines): Ces systèmes défaillent d'une manière arbitraire. Le système peut faire n'importe quoi (y compris un comportement

malveillant). Ce mode de défaillance est parfois considéré par des systèmes à très haute fiabilité (nucléaire, spatial).

Notons qu'une hypothèse de défaillance peut couvrir une ou plusieurs autres hypothèses. La couverture entre les hypothèses que nous avons citées est illustrée sur la figure 3.2

Figure 3.2 : Couverture entre hypothèses de défaillances

Comme notre objectif est de réaliser des systèmes temps réel embarqués et distribués sûrs de fonctionnement, il ya plusieurs méthodes dans la littérature qui s'intéressent à donner les meilleurs résultats. Deux grandes classes de ces méthodes sont : l'évitement des fautes qui vise à empêcher l'occurrence de fautes par la prévention, l'évaluation ou la vérification des fautes, et la tolérance des fautes qui est l'objectif de notre mémoire. La tolérance aux fautes vise à préserver le service du système malgré l'occurrence de fautes.

Plusieurs travaux dans la littérature ont défini le concept de la tolérance aux fautes [4, 6, 7, 15], la définition suivante est la définition originale donnée par Algirdas Avizienis [7] en 1967:

**Définition 31 (Tolérance aux fautes) :** On dit qu'un système informatique est tolérant aux fautes si ses programmes peuvent être exécutés correctement même en présence de fautes.

## 3.2.3. Techniques de tolérance aux fautes

Les méthodes de tolérances aux fautes sont basées sur deux classes de techniques :

- Traiter les fautes.

- Traiter les erreurs

#### a. Traitement des fautes

Dans ce cas, l'algorithme de tolérance aux fautes vise à empêcher les fautes d'être activées. Elle concerne au moins deux étapes qui sont le diagnostique des fautes et l'inactivation des fautes.

- **Diagnostique des fautes :** détermine les causes de l'erreur en termes de location et de nature.

- **Inactivation des fautes :** prévient l'activation des fautes une autre fois (en les rendant passives).

#### b. Traitement des erreurs

Dans ce cas, l'algorithme de tolérance aux fautes consiste à détecter l'existence d'un état incorrect (erreur), puis remplacer l'état incorrect par un état correct conforme aux spécifications.

Dans tous les cas, la redondance est le principe unique utilisé afin de traiter les erreurs, il y a trois formes de redondance :

- Redondance matérielle: comporte les composants matériels ajoutés au système pour supporter la tolérance aux fautes (par exemple, utiliser un processeur disponible si l'un des processeurs en exécution est en panne),

- Redondance logicielle (ou d'information): inclut tous les programmes et les instructions qui sont utilisés pour supporter la tolérance aux fautes (par exemple, en utilisant deux réalisations du même module).

- Et redondance temporelle: consiste à accorder un temps supplémentaire pour accomplir l'exécution des tâches pour supporter la tolérance aux fautes (par exemple, exécuter de nouveau un module plus tard).

## Remarque:

Ce travail concerne les techniques de tolérance aux fautes basées sur le traitement d'erreurs.

## 3.2.4. Algorithmes de la tolérance aux fautes

Prenant la technique de tolérance aux fautes basées sur le traitement des erreurs, l'algorithme de tolérance aux fautes est réalisé en deux phases complémentaires : une phase de détection des erreurs et une phase de traitement des erreurs.

## 3.2.4.1. Phases d'un algorithme de tolérance aux fautes

#### a. Détection des erreurs

C'est la phase la plus importante, puisque la réussite de l'algorithme dépend d'elle, elle permet :

- D'identifier le type et l'origine des erreurs,

- De prévenir (si possible) l'occurrence d'une défaillance provoquée par l'erreur,

- D'éviter la propagation de l'erreur à d'autres composants

Cette détection peut être faite soit au niveau de l'environnement du système, soit au niveau de l'application du système [16]. Au niveau de l'environnement, c'est l'exécutif de l'application qui se charge de détecter certaines erreurs qui peuvent être par exemple de type : division par zéro, erreur d'entrée/sortie, accès interdit au périphérique. Au niveau de l'application, ce sont les composants redondants qui se chargent de réaliser cette tâche de détection.

Il ya plusieurs techniques de détection d'erreurs au niveau de l'application, parmi les techniques de base, on trouve la comparaison des résultats de composants répliqués et le contrôle de vraisemblance (vérification des temps de délivrance des résultats). La réussite d'une telle technique de détection des erreurs dépend de deux paramètres qui sont la latence (délai entre la production et la détection de l'erreur) et le taux de couverture (pourcentage d'erreurs détectées).

## b. Traitement des erreurs

Cette phase consiste à traiter les états erronés (ou erreurs) détectés par la première phase, éliminer des erreurs de l'état du système à l'aide de l'une des deux techniques de base à savoir le recouvrement ou la compensation .

#### Recouvrement des erreurs

Le recouvrement consiste à remplacer l'état d'erreur par un état correct, il nécessite pour cela la détection d'erreurs au moyen d'un test de vraisemblance explicite ou implicite. Il utilise soit la technique de la reprise soit la technique de la poursuit. La reprise consiste à mettre le système dans un de ses états précédents corrects (retour en arrière vers un état antérieur dont on sait qu'il est correct), et la poursuite permet soit la reconstitution d'un état courant correct (sans retour en arrière), soit la reconstitution partielle d'un état correct qui permet au système de fonctionner en mode dégradé.

#### > Compensation des erreurs

L'état possède une redondance interne d'informations suffisante pour détecter et corriger l'erreur (les tests externes de vraisemblance sont inutiles) pour masquer (rendre invisibles aux utilisateurs) ses conséquences.

Le choix entre ces deux techniques est un compromis entre plusieurs facteurs, tels que la complexité du système, les contraintes temporelles et matérielles et la criticité du système. Etant donné que nous visons des systèmes temps réel embarqués et distribués critiques, nous ne nous intéressons dans ce travail qu'aux techniques basées sur la redondance d'informations, donc aux techniques de compensation des erreurs.

## 3.2.4.2. Tolérance aux fautes matérielles et logicielles

La défaillance d'un système est due soit aux fautes matérielles, soit aux fautes logicielles.

## a. Tolérance aux fautes logicielles

Les fautes logicielles sont dues aux erreurs de conception des composants logiciels de l'algorithme. L'explosion de la fusée Ariane 5 en juin 1996 à cause des erreurs de conception du logiciel est un exemple de ce type de fautes [17, 18]. Les techniques utilisées pour tolérer les fautes logicielles d'un système sont divisées en deux grands groups [19] : l'uni-version du logiciel et la multi-version du logiciel.

## Uni-version du logiciel

La technique uni-version se concentre sur l'amélioration de la tolérance aux fautes en utilisant une seule version du logiciel ou d'un de ses composants en ajoutant des mécanismes dans la conception visant la détection et le traitement des erreurs provoquées par l'activation des fautes de conception. Elle est basée sur l'utilisation de la redondance appliquée à une version unique d'un composant logiciel pour détecter et récupérer des fautes. Parmi les approches utilisant cette technique, on trouve : le traitement d'exception, la détection d'erreur et le point de reprise.

## > Multi-version du logiciel

Cette technique emploie des versions multiples (ou des variantes) d'un composant logiciel dans une manière structurée d'une façon à s'assurer que les fautes de conception dans une version ne causent pas des défaillances du système. Elle est basée sur le principe de la redondance logicielle, où chaque composant logiciel est répliqué en plusieurs versions différentes. Parmi les approches utilisant cette technique, on trouve : N-vérification automatique de programmation et N-version de programmation qui est le cas des commandes de vol des avions Airbus et Boeing [20].

#### b. Tolérance aux fautes matérielles