# **People's Democratic Republic of Algeria** Ministry of Higher Education and Scientific Research

**University of Batna** Faculty of Science Department of Physics

# STUDY AND MODELING OF NANOSCALE GCGS DG MOSFET

« Étude et modélisation du transistor GCGS DG MOSFET nanométrique »

A Thesis Presented to the University of Batna

Department of Physics

By

# **Toufik BENTRCIA**

In Partial Fulfillment of the Requirements for the degree of Master of Science in Physics

Advisor

## Dr. Fayçal DJEFFAL

Approved by:

# JURY

| M. Chahdi  | Prof.      | University of Batna       | Thesis Committee President |

|------------|------------|---------------------------|----------------------------|

| F. Djeffal | Assoc.Prof | University of Batna       | Thesis Advisor             |

| A. Bellel  | Prof.      | University of Constantine | Thesis Committee Member    |

| R. Mahamdi | Prof.      | University of Batna       | Thesis Committee Member    |

November 2010

# **ACKNOWLEDGMENTS**

First and foremost, my unconditional praise and thankfulness goes to Allah, the Most Compassionate, and the Most Merciful for his countless bounties and blessings.

I am indebted to my advisor: Dr. Fayçal DJEFFAL, for his able guidance and productive comments without which this thesis would not have been completed.

Dr. DJEFFAL pushed me toward excellence by promoting high-quality research. He continuously challenged the feasibility of my ideas and the validity of the mathematical analysis and simulation. During co-authoring papers, Dr. DJEFFAL has substantially improved my writing and presentation skills: I have learned how to make trade-offs between conciseness and comprehensiveness.

I am very grateful to Professors: Mohammed CHAHDI from the university of Batna for being the president of the examination committee, Ahmed BELLEL from the university of Constantine and Ramdan MAHAMDI from the university of Batna, for having accepted to be in the jury of my thesis. Their feedback and comments provided me worthy ideas for further improvements and future work directions.

Throughout the preparation of my thesis, I spent fun times with many friends, thanks go to: Dr. Redha Benzid, Mohammed Amir, Toufik, Mohamed, Fouzi, NasrEddine, NourEddine, AzzEddine, Yacine, Mourad and Abdelkader. I am sure that I have missed a lot of names, so please be indulgent.

Finally, my innermost thanks go to all my family for their endless support and special help.

Toufik

# Contents

| Acknowledgement                            |

|--------------------------------------------|

| List of figures                            |

| List of tables                             |

| List of publications                       |

| INTRODUCTION                               |

| CHAPTER I: DEEP SUBMICRON MOSFETs5         |

| I.1 – Introduction                         |

| I.2 – Evolution of CMOS technology         |

| I.3 – MOSFET structure and operation8      |

| I.3.1. Presentation of the Structure       |

| I.3.2. Operation Modes9                    |

| I.4 – Small signal parameters12            |

| I.5 – Miniaturization effects14            |

| I.6 – Emergent solutions17                 |

| I.6.1. High-k and metal gate integration17 |

| I.6.2. Strain-enhanced mobility18          |

| I.6.3. Multi-gate devices19                |

| I.7 – Nanotechnologies21                   |

| <i>I.8 – Conclusion</i>                    |

| CHAPTER II: DEFECTS IN MOSFET DEVICES25    |

| II.1 – Introduction                        |

| II.2 – Defects classification              |

| II.2.1 Bulk defects                        |

| II.2.2 Hot carrier                         |

| II.3 – Device degradation models           |

| II.4 - C | <b>Conclusion</b> |  | 39 |

|----------|-------------------|--|----|

|----------|-------------------|--|----|

## CHAPTER III: MODELING OF GCGS DG MOSFET IN SUBTHRESHOLD

| III.1 – Introduction            |    |

|---------------------------------|----|

| III.2 – Model formulation       | 43 |

| III.2.1. Surface potential      |    |

| III.2.2.Threshold voltage       | 47 |

| III.2.3. Subthreshold current   |    |

| III.2.4. Subthreshold swing     |    |

| III.3 – Results and discussion. | 52 |

| III.4 – Conclusion              | 56 |

#

| IV.1 – Introduction                                   | 58 |

|-------------------------------------------------------|----|

| IV.2 – Description of the studied structure           | 58 |

| IV.3 – Proposed models formulation                    | 60 |

| IV.3.1. Piece-Wise Drain Current Models               | 63 |

| IV.3.2. Surface potential based drain current model   | 65 |

| IV.4 – Results and discussion                         | 69 |

| IV.4.1. Piece-Wise Drain Current Models               | 69 |

| IV.4.2. Surface potential based drain current model   | 74 |

| IV.5 – Impact of hot-carrier degradation on IC design | 76 |

| IV.6 – Conclusions                                    |    |

| CONCLUSION AND FUTURE WORK                            | 81 |

| REFERENCES                                            | 83 |

# LIST OF FIGURES

# Chapter I

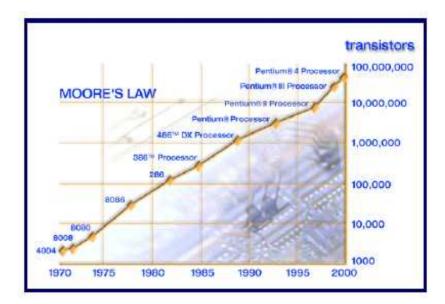

Fig. I.1. Moore's Law predictions for devices scaling.

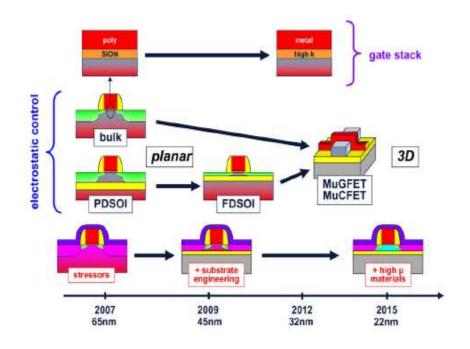

Fig. I.2. Simplified transistor roadmap (courtesy ENIAC).

Fig. I.3. MOS transistor structure showing three-dimensional view

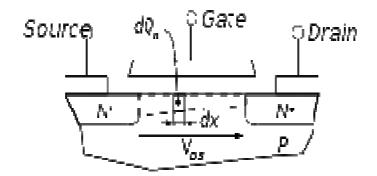

Fig. I.4. Cross section of a MOSFET operating in the linear (Ohmic) region; strong inversion region present even near drain

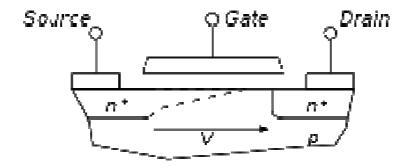

Fig. I.5. Cross section of a MOSFET operating in the saturation (active) region; channel exhibits pinch-off near drain

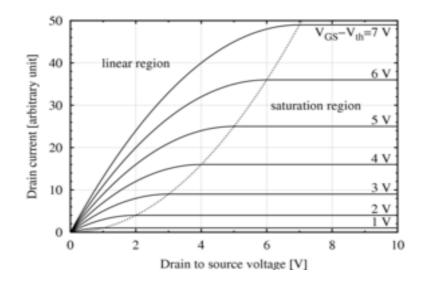

Fig. I.6. MOSFET drain current vs. drain-to-source voltage for several values of  $V_{GS} - V_{th}$ .

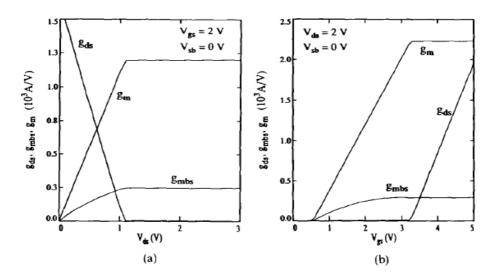

Fig. I.7. Small-signal parameters  $g_{m}$ ,  $g_{mbs}$  and  $g_{ds}$  as a function of (a)  $V_{ds}$ , and (b)  $V_{gs}$ ,

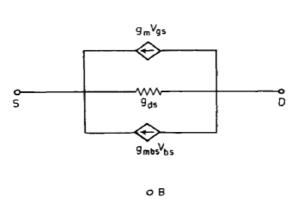

Fig. I.8. A low frequency, usually less than 1 KHz, small-signal model for a MOSFET.

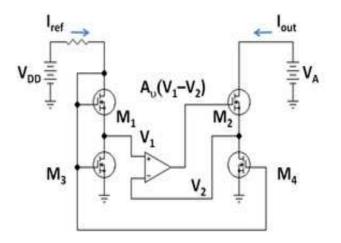

Fig. I.9. MOSFET version of gain-boosted current mirror;  $M_1$  and  $M_2$  are in active mode, while  $M_3$  and  $M_4$  are in Ohmic mode, and act like resistors.

Fig. I.10. Schematic diagram of MBCFET on SOI.

# **Chapter II**

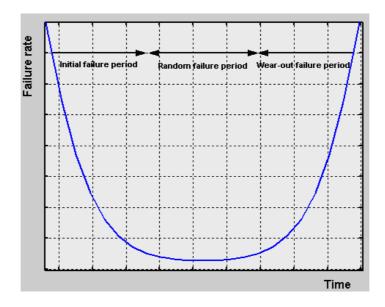

Fig. II.1. Failure rate curve (Bathtub Curve) of semiconductors devices.

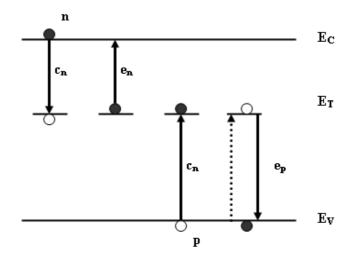

Fig. II.2. Electron energy band diagram for a semiconductor with deep-level impurities in addition to capture and emission process.

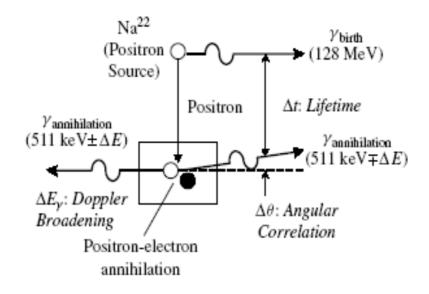

Fig. II.3. Schematic illustration of positron annihilation showing positron creation, positronelectron annihilation,  $\gamma$  emission and the main experimental techniques for PAS

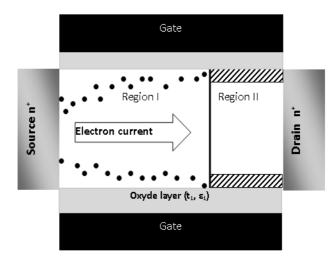

Fig. II.4. Creation of a damaged region in the DG MOSFET structure because of hot-carrier degradation process.

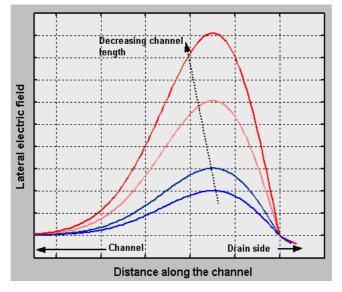

Fig. II.5. Maximum lateral electric field at the Si-SiO<sub>2</sub> interface along the channel in MOS transistors with decreasing channel lengths.

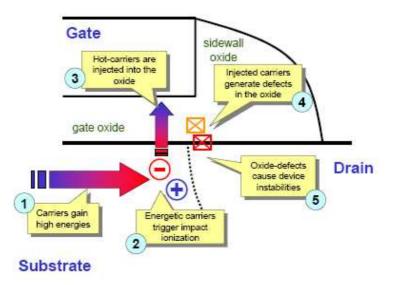

Fig. II.6. Sequence of physical mechanisms that contribute to HC-induced device degradation in MOS transistors.

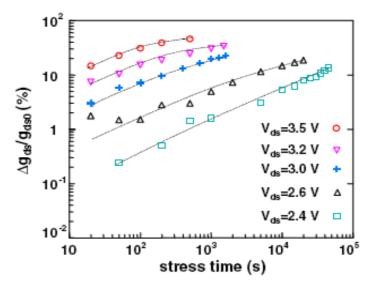

Fig. II.7. Normalized variation of the output conductance  $g_{ds}$  with stress time t.

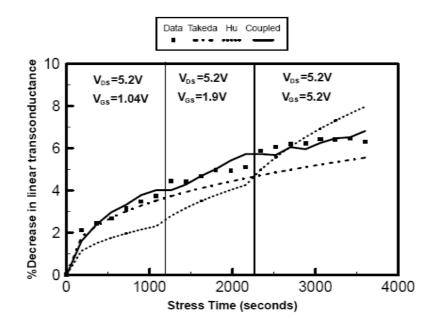

Fig. II.8. Device degradation for stressing under bias sequence 2.

# **Chapter III**

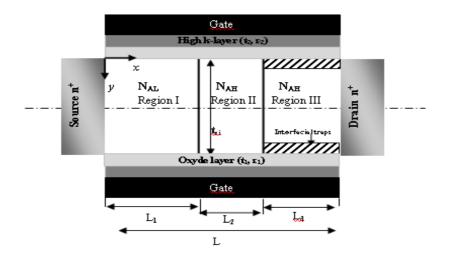

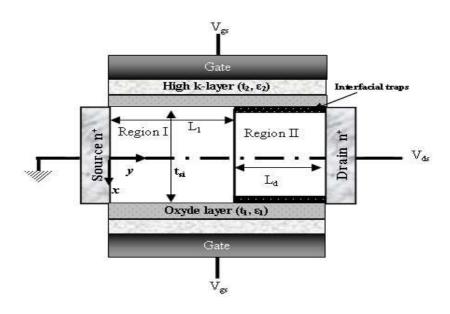

Fig. III.1. Cross-sectional view of the GC GS DG MOSFET proposed inner structure.

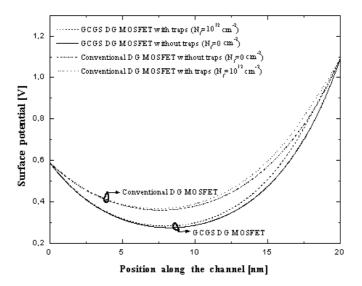

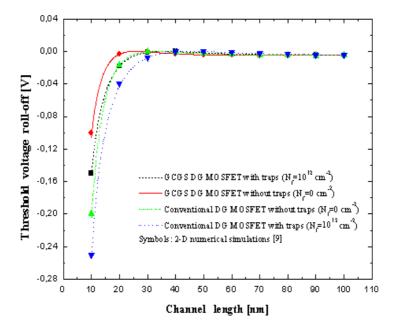

Fig. III.2. Surface potential for Conventional and GCGS DG MOSFET with and without traps Fig.III.3. Calculated threshold voltage roll-off for Conventional and GCGS DG MOSFET with and without traps

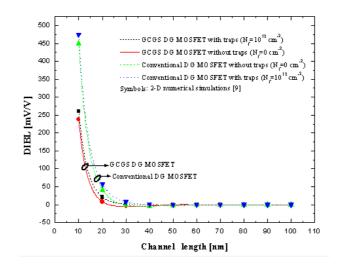

Fig.III.4. Variation of DIBL for Conventional and GCGS DG MOSFET with and without traps as function of channel length

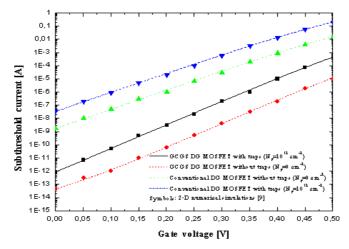

Fig.III.5. Calculated subthreshold current for Conventional and GCGS DG MOSFET with and without traps

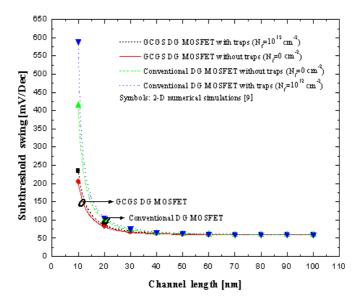

Fig.III.6. Calculated subthreshold swing for Conventional and GCGS DG MOSFET with and without traps as a function of channel length

# **Chapter IV**

Fig. IV.1. DG MOSFET investigated in this work, where region II is the region with hotcarrier induced interface charges.

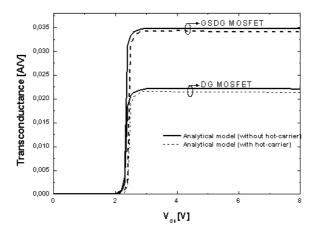

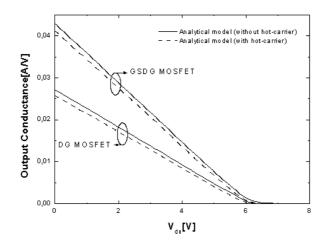

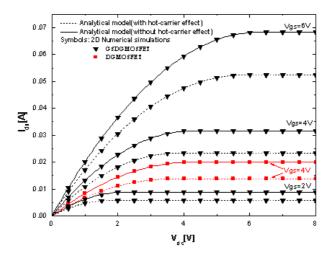

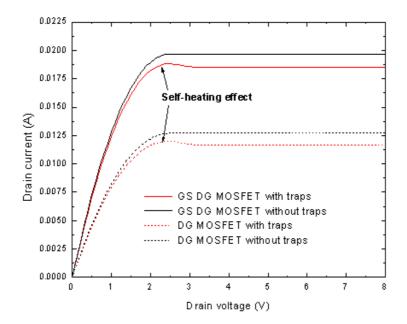

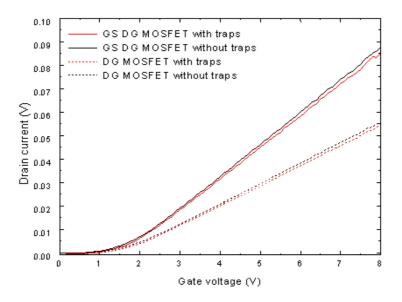

Fig. IV.2. Ids-Vds characteristics for DG and GSDG MOSFETs with and without traps.

Fig. IV.3. Transconductance variation for both DG and GSDG MOSFETs including hotcarrier effects.

Fig. IV.4. Output conductance versus drain voltage of DG and GSDG MOSFETs.

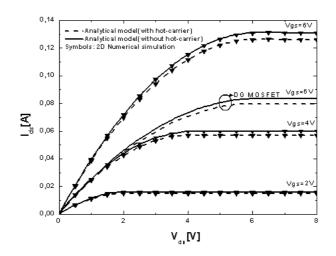

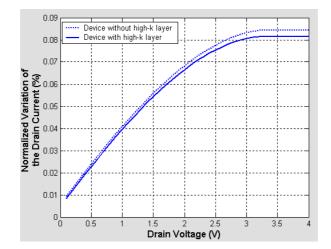

Fig. IV.5.  $I_{ds}$ - $V_{ds}$  characteristics of DG MOSFET before and after stress for both cases with and without high-k layer.

Fig. IV.6. Normalized variation of the drain current of DG MOSFET for both cases with and without high-k layer.

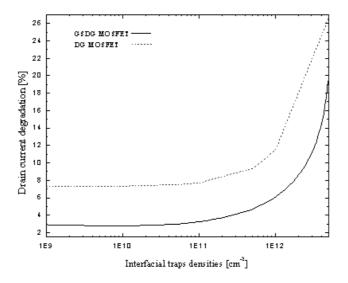

Fig. IV.7. Calculated drain current degradation as function of traps densities for DG MOSFET with high-k layer.

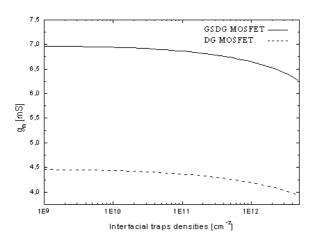

Fig. IV.8. Transconductance degradation as function of interfacial traps densities of DG MOSFET for both cases with and without high-k layer.

Fig. IV.9.  $I_{ds}$ - $V_{ds}$  characteristics of DG MOSFET before and after stress for both cases with and without high-k layer.

Fig. IV.10.  $I_{ds}$ - $V_{gs}$  characteristics of DG MOSFET before and after stress for both cases with and without high-k layer.

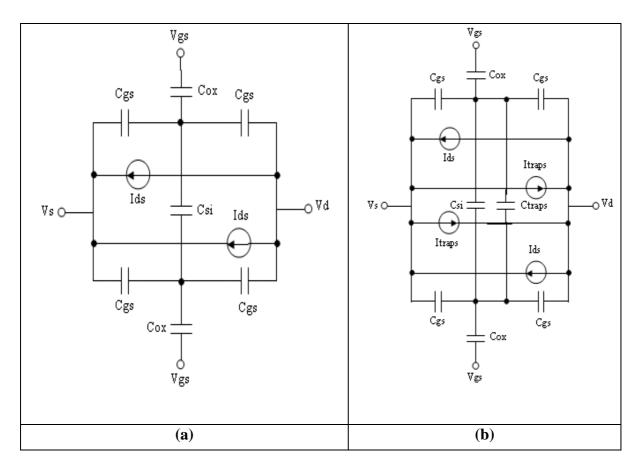

Fig. IV.11. Electric scheme of the GSDG MOSFET without parasitic resistances (a) before the implantation of our model, and (b) after the implantation of the interfacial hot-carrier degradation effects.

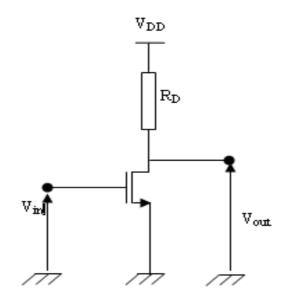

Fig. IV.12. Circuit diagram of a single GSDG MOSFET amplifier.

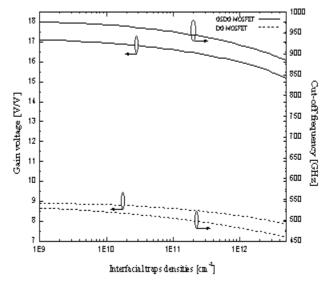

Fig. IV.13. Gain and cut-off frequency degradations of the GSDG MOSFET amplifier as function of interfacial traps densities

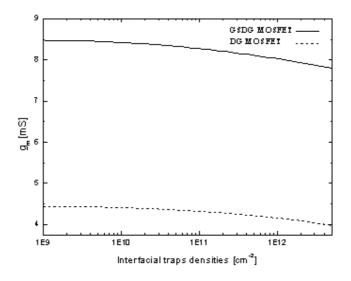

Fig. IV.14. Transconductance degradation as function of interfacial traps densities

# LIST OF TABLES

# Chapter II

TABLE. II.1. Summary of important changes in the single NMOSFET

# Chapter III

TABLE .III.3. Values of parameters used in the analysis.

# Chapter IV

TABLE .IV.1. Asymptotic values and dominance rules for different regions of operation.

TABLE .IV.2. Values of parameters used in the simulation based on the first model.

TABLE .IV.3. Values of parameters used in the simulation based on the second model.

TABLE .IV.4. Values of parameters used in the simulation based on the surface potential model.

# LIST OF PUBLICATIONS

### **Conference Papers**

**1.** T. Bentrcia, F. Djeffal & D. Arar, "An Analytical Two Dimensional Subthreshold Current Model for Nanoscale GCGS DG MOSFET Including Interfacial Traps Effects", 2<sup>nd</sup> International Conference on Electronic Systems CISE'2009, pp. 173-177. Batna, Algeria, October 25-26, 2009.

**2.** T. Bentrcia, F. Djeffal, M.A. Abdi, M. Chahdi & N. Boukhennoufa, "An Accurate Two Dimensional Threshold Voltage Model for Nanoscale GCGS DG MOSFET Including Traps Effects", 3<sup>rd</sup> International Conference on Signals, Circuits and Systems SCS'2009, (CD), pp. 273-277, Djerba, Tunisia, November 06-08, 2009 (Available also at IEEE Xplore).

**3.** F. Djeffal & T. Bentrcia, "An Analytical Drain Current Model for Undoped Double-Gate MOSFETs including Interfacial Hot-Carrier Effects", *European Materials Research Society Spring Meeting E-MRS*'2010, Strasbourg, France, June 07-11, 2010.

**4.** T. Bentrcia, F. Djeffal, M.A. Abdi & D. Arar, "A Compact Analytical Current Model including Traps Effects for GS DG MOSFETs", accepted in 2010 XIth IEEE International Workshop on Symbolic and Numerical Methods, Modeling and Applications to Circuit Design SM2ACD'2010, Gammarth, Tunisia, October 05-06, 2010.

## **Journal Papers**

**1.** F. Djeffal, T. Bentrcia & T. Bendib, "An Analytical Drain Current Model for Undoped GSDG MOSFETs Including Interfacial Hot-carrier Effects", accepted for publication in *Physica Status Solidi A*, pssc.201000158, 2010.

**2.** F. Djeffal, T. Bentrcia, M.A. Abdi & T. Bendib, "Drain Current Model for Undoped Gate Stack Double Gate (GSDG) MOSFETs Including the Hot-carrier Degradation Effects", accepted for publication in *Microelectronics Reliability*.

**3.** T. Bentrcia, F. Djeffal and M. Chahdi, "An Analytical Two Dimensional Subthreshold Behavior Model to study the Nanoscale GCGS DG MOSFET including Interfacial Traps Effects", submitted to *IEEE Transaction on Device and Materials Reliability*.

4. T. Bentrcia, F. Djeffal and A. Benhaya, "Continuous Analytic I-V Model for GS DG MOSFETs Including Hot-Carrier Degradation Effects", submitted to Electronics Letters.

#### **Book Chapter**

**1.** T. Bentrcia and F. Djeffal, "Compact Modeling of Multi-Gate MOSFET Including Hot-carrier Effects", Chapter 4, CMOS Technology, Series: Electrical Engineering Developments, Editor: Minjun Kwon, Nova Science Publishers, ISBN: 978-1-61761-325-8, NY, USA, 2010.

# **INTRODUCTION**

Advances in semiconductor manufacturing techniques and ever increasing demand for faster and more complex Integrated Circuits (ICs) have driven the associated Metal Oxide Semiconductor Field Effect Transistor (MOSFET) sizes close to their physical limits. On the other hand, it has not been possible to scale the supply voltage used to operate these ICs proportionately due to factors such as compatibility with previous generation circuits, noise margin, power and delay requirements, and non-scaling of threshold voltage, subthreshold slope, and parasitic capacitance [1]. While the consequent increase in internal electric fields in aggressively scaled MOSFETs comes with the additional benefit of increased carrier velocities, and hence increased switching speed, it also presents a major reliability problem for the long term operation of these devices. As devices are scaled the benefits of higher electric fields saturate while the associated reliability problems get worse.

The presence of mobile carriers in the oxides triggers various physical processes that can drastically change the device characteristics during normal operation over prolonged periods of time eventually causing the circuit to fail. Such degradation in device and circuit behavior due to injection of energetic carriers from the silicon substrate into the surrounding dielectrics is known as "hot-carrier degradation" [2].

It is clear that the presence of large electric fields has major influence on the long term operation of modern ICs. These Hot-Carrier (HC) related device instabilities have become a major reliability concern in modern Metal Oxide Semiconductor (MOS) transistors and are expected to get worse in future generation of devices. The study of the fundamental physical processes that result in device parameter variation due to HC injection is essential to provide guidelines for avoiding such problems in future ICs.

In the past, methods for the evaluation of HC reliability have been based on physical models for long-channel transistors. These approaches have been remarkably successful in predicting the time-dependence of HC degradation on factors such as channel length, channel doping, and supply voltage in long-channel devices. Even though the limitations in their application to deep sub-micron devices have long been recognized, as devices are scaled, the same techniques continue to be applied to short-channel devices. In short-channel devices,

<sup>1</sup>

however, several assumptions made in the conventional approaches break down and hence the parameters associated with most of these models lose their physical meaning. These model parameter are usually extracted by fitting the model to experimental data. Such empirical approaches, though useful for qualitative evaluation of existing technologies, provide little insight into the physical mechanisms responsible for the device degradation. Furthermore, the semi-physical model parameters extracted from a given set of experiments on a particular technology are not able to predict the device behavior under process modifications essential to meet circuit performance requirements as the devices are scaled. Hence such approaches cannot be used for predictive modeling and/or to aid the semiconductor industry in designing manufacturing processes to overcome the relevant reliability problems. The presence of novel physical mechanisms such as short-channel effects, non-local carrier heating, and quantum effects in aggressively scaled devices further complicates the modeling process and requires the use of more comprehensive modeling techniques for such structures [3].

This thesis is structured in four chapters divided into two parts: the state of the art and contributions. The state of the art part presents background on MOSFET structure particularly when scaled to deep submicron level, hence many unwanted phenomena altering the correct function of the device. The contribution part contains our proposals for modeling the performance of deep submicron MOSFET devices including the hot-carrier degradation effects when compared to the conventional bulk devices.

The thesis presents a study of the degradation of proposed MOSFET device parameters, which affect circuit operation, due to processes initiated by injection of high energy carriers into the gate oxide, the characterization techniques used to measure and attribute these parameter shifts to the underlying processes, and the use of empirical, semi-empirical, and physical models to predict the time dependence of the parameter degradation during circuit operation. The current understanding of the basic concepts related to MOSFET devices is presented in Chapter I. This chapter highlights the processes that need to be modeled in device simulation tools in order to be applicable to predictive simulation of HC phenomena in current and future generation MOSFETs.

Chapter II and onwards start our contributions. In Chapter II we describe the development of modeling tools along with the choices and assumptions that were made to model the physical mechanism described in Chapter III in a practical simulation application. The details of the numerical model developed as a result of this analysis in subthreshold region are presented. The results of the application of these simulation tools to HC degradation in GS DG MOSFET for both linear and saturation regimes are presented in Chapter IV.

Finally, we conclude this thesis and present our view on future research directions.

# Chapter I-

# **DEEP SUBMICRON MOSFETS**

*Abstract:* The compact modeling of MOS transistors for integrated circuit design has, for many years, been driven by the needs of digital circuit simulation. Conventional bulk CMOS technology is still prevalent in the microelectronics industry. According to the International Technology Roadmap for Semiconductors, bulk MOS transistors will still be used for the 45 nm technology node (gate length around 18 nm), which is expected to be running by 2010. The feasibility of 15 nm conventional MOS transistors in bulk CMOS technology has already been demonstrated.

The purpose of this chapter is to provide both an overview about the evolution of MOSFETs devices in addition to the basic physics theory required to build compact models required later for the deduction of some mandatory parameters and for the incorporation of new constraints in the function of the device.

## **I.1. INTRODUCTION**

Since the 60's the shrinking of electronic components has been driven by the fabrication of integrated circuits, which will continue for at least the next two decades. The critical feature size of the elementary devices (physical gate length of the transistors) will drop from 25 nm in 2007 (65 nm technology node) to 5 nm in 2020 (14 nm technology node). In the sub-10 nm range, beyond--CMOS (complementary MOS) devices will certainly play an important role and could be integrated on CMOS platforms in order to pursue integration down to nm structures. Si will remain the main semiconductor material in a foreseeable future, but the needed performance improvements for the end of the ITRS (international technology roadmap for semiconductors) will lead to a substantial enlargement of the number of materials, technologies and device architectures [4].

Therefore, new generations of nanoelectronic integrated circuits (ICs) present increasingly formidable multidisciplinary challenges at the most fundamental level (novel materials, new physical phenomena, ultimate technological processes, etc.) resulting in an urgent need of long term research based on a scientific approach, in order to understand the underlying physical mechanisms and hence remove the present technological limitations. The industry is indeed increasingly relying on new ideas in order to continue technological innovation [5].

This chapter addresses the basic concepts related to the MOSFET technology, with some advanced ideas for keeping CMOS on the road. Different regimes characterizing the function of a MOSFET device are also depicted, in addition to some challenging problems encountering the downscaling process and their associated solutions. This chapter can be considered as an introductory platform for further chapters.

## I.2. EVOLUTION OF CMOS TECHNOLOGY

As the density of integrated circuits continues to increase, a resulting shrinkage of the dimensions of the individual devices of which they are comprised has followed. Smaller circuit dimensions reduce the overall circuit area, thus allowing for more transistors on a single die without negatively impacting the cost of manufacturing. However, this reduction in device size is only one of three factors identified by Moore in the increased density of modern integrated circuits. Equally important are the two other factors of an increase of die size and an increase in circuit cleverness - the reduction in number of devices and chip area to implement a given circuit or function. All of these lead to the driving force for continued

integration complexity is the reduction in cost per function for the chip as indicated by figure Fig.I.1 [6].

Fig. I.1. Moore's Law predictions for devices scaling [6].

As semiconductor feature sizes shrink into the nanometer scale regime, device behavior becomes increasingly complicated as new physical phenomena at short dimensions occur, and limitations in material properties are reached. In addition to the problems related to the actual operation of ultra-small devices, the reduced feature sizes require more complicated and time-consuming manufacturing processes. This fact signifies that a pure trial-and-error approach to device optimization will become impossible since it is both too time consuming and too expensive. Nevertheless, it is important to consider these new physical effects which will occur in small devices, as these effects may well eventually dominate device performance.

The traditional scaling of classical planar CMOS devices leads to performance limitations, which have to be overcome by introduction of new device architectures. New so-called 'nonclassical' CMOS device concepts are being developed. A development roadmap of CMOS device architectures is shown in Fig. I.2 in comparison with standard bulk devices. Some of these advanced device structures will probably be introduced within the next 5–10 years. The ultimate CMOS device with the multi-gate FET structure will potentially carry the silicon technology down to below 10 nm feature sizes, but it is also challenged by process complexity and manufacturability; its key advantages are, lithography independent gate length control and higher drive currents [7].

Fig. I.2. Simplified transistor roadmap (courtesy ENIAC) [7].

## **I.3. MOSFET STRUCTURE AND OPERATION**

#### I.3.1. Presentation of the Structure

As the name metal-oxide-semiconductor (MOS) suggests, the MOS transistor consists of a semiconductor substrate (usually silicon) on which is grown a thin layer of insulating oxide (SiO) of thickness  $t_{ox}$  A conducting layer (a metal or heavily doped polysilicon) called the gate electrode is deposited on top of the oxide. Two heavily doped regions of depth  $X_j$ , called the source and the drain are formed in the substrate on either side of the gate. The source and the drain regions overlap slightly with the gate (see Fig. I.3.) [8].

Fig. I.3. MOS transistor structure showing three-dimensional view [8].

The source-to-drain electrodes are equivalent to two p-n junctions back to back. This region between the source and drain junctions is called the channel region. Thus a MOS transistor is essentially a MOS structure, called the MOS capacitor, with two p-n junctions on either side of the gate. The field oxide (FOX) shown in Figure I.3. is for isolating various devices on the same substrate. From the circuit model point of view, a MOS transistor is a four terminal device, the four terminals are designated as gate g, source s, drain d, and substrate or bulk b. Note that the structure is symmetrical. Because of this symmetry one cannot distinguish between the source and drain of an unbiased device; the roles of the source and the drain are defined only after the terminal voltages are applied.

Under normal operating conditions, a voltage *V*, applied to the gate terminal creates an electric field that controls the flow of the charge carriers in the channel region between the source and the drain. Since the device current is controlled by the electric field (vertical field due to the gate voltage and lateral field due to the source to drain voltage) the device is known as a MOS Field-Effect-Transistor (MOSFET). Because the gate is electrically isolated from the other electrodes, this device is also called an Insulated-Gate Field-Effect Transistor (IGFET). Another acronym sometime used is MOST for the MOS Transistor. The bulk of the semiconductor region, shown as substrate in Figure I.3, is normally inactive, since the current flow is confined to a thin channel at the surface of the semiconductor. It is for this reason the substrate region is also referred to as the body or bulk of the MOSFET.

MOSFETs may be either n-channel or p-channel depending upon the type of the carriers in the channel region. An n-channel MOS transistor (nMOST) has heavily doped n+ source and drain regions with a p-type substrate and has electrons as the carriers in the channel region.

#### I.3.2. Operation Modes

The operation of a MOSFET can be separated into three different modes, depending on the voltages at the terminals. In the following discussion, a simplified algebraic model is used that is accurate only for old technology. Modern MOSFET characteristics require computer models that have rather more complex behavior.

For an enhancement-mode, n-channel MOSFET, the three operational modes are [9]:

Subthreshold, or weak-inversion mode ( $V_{GS} < V_{th}$ ), where  $V_{th}$  is the threshold voltage of the device: According to the basic threshold model, the transistor is turned off, and there is no conduction between drain and source. In reality, the Boltzmann distribution of electron energies allows some of the more energetic electrons at the source to enter the channel and flow to the drain, resulting in a subthreshold current that is an exponential function of gate–source voltage. While the current between drain and source should ideally be zero when the

transistor is being used as a turned-off switch, there is a weak-inversion current, sometimes called subthreshold leakage.

In weak inversion the current varies exponentially with gate-to-source bias  $V_{GS}$  as given approximately by:

$$I_D \approx I_{D0} e^{\frac{V_{GS} - V_{th}}{nV_T}}$$

(I.1)

where  $I_{D0}$  is the current at  $V_{GS} = V_{th}$  and the slope factor *n* is given by  $n = 1 + C_D / C_{OX}$ , with  $C_D$  is the capacitance of the depletion layer and  $C_{OX}$  is the capacitance of the oxide layer. In a long-channel device, there is no drain voltage dependence of the current once  $V_{DS} >> V_T$ , but as channel length is reduced drain-induced barrier lowering introduces drain voltage dependence that depends in a complex way upon the device geometry (for example, the channel doping, the junction doping and so on). Frequently, threshold voltage  $V_{th}$  for this mode is defined as the gate voltage at which a selected value of current  $I_{D0}$  occurs, for example,  $I_{D0} = 1 \ \mu A$ , which may not be the same  $V_{th}$ -value used in the equations for the following modes.

Some micropower analog circuits are designed to take advantage of subthreshold conduction. By working in the weak-inversion region, the MOSFETs in these circuits deliver the highest possible transconductance-to-current ratio, namely:  $g_m / I_D = 1 / (nV_T)$ , almost that of a bipolar transistor.

The subthreshold *I–V curve* depends exponentially upon threshold voltage, introducing a strong dependence on any manufacturing variation that affects threshold voltage; for example: variations in oxide thickness, junction depth, or body doping that change the degree of drain-induced barrier lowering. The resulting sensitivity to fabricational variations complicates optimization for leakage and performance.

*Linear region* also known as the ohmic mode ( $V_{GS} > V_{th}$  and  $V_{DS} < (V_{GS} - V_{th})$ )

The transistor is turned on, and a channel has been created which allows current to flow between the drain and the source. The MOSFET operates like a resistor, controlled by the gate voltage relative to both the source and drain voltages as shown in figure Fig. I.4. The current from drain to source is modeled as:

$$I_{D} = \mu_{n} C_{ox} \frac{W}{L} \left( (V_{GS} - V_{th}) V_{DS} - \frac{V_{DS}^{2}}{2} \right)$$

(I.2)

where  $\mu_n$  is the charge-carrier effective mobility, *W* is the gate width, *L* is the gate length and  $C_{ox}$  is the gate oxide capacitance per unit area. The transition from the exponential subthreshold region to the triode region is not as sharp as the equations suggest.

Fig. I.4. Cross section of a MOSFET operating in the linear (Ohmic) region; strong inversion region present even near drain.

## Saturation or active mode ( $V_{GS} > V_{th} \text{ and } V_{DS} > (\ V_{GS} \text{ - } V_{th} \ ))$

The switch is turned on, and a channel has been created, which allows current to flow between the drain and source. Since the drain voltage is higher than the gate voltage, the electrons spread out, and conduction is not through a narrow channel but through a broader, two- or three-dimensional current distribution extending away from the interface and deeper in the substrate. The onset of this region is also known as pinch-off to indicate the lack of channel region near the drain (Fig.I.5). The drain current is now weakly dependent upon drain voltage and controlled primarily by the gate–source voltage, and modeled very approximately as:

$$I_{D} = \frac{\mu_{n} C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^{2} (1 + \lambda V_{DS})$$

(I.3)

Fig. I.5. Cross section of a MOSFET operating in the saturation (active) region; channel exhibits pinch-off near drain.

The boundary between linear (Ohmic) and saturation (active) modes is indicated by the upward curving parabola in figure Fig. I.6.

Fig. I.6. MOSFET drain current vs. drain-to-source voltage for several values of  $V_{GS} - V_{th}$ .

As the channel length becomes very short, these equations become quite inaccurate. New physical effects arise. For example, carrier transport in the active mode may become limited by velocity saturation. When velocity saturation dominates, the saturation drain current is more nearly linear than quadratic in  $V_{GS}$ . At even shorter lengths, carriers transport with near zero scattering, known as quasi-ballistic transport. In addition, the output current is affected by drain-induced barrier lowering of the threshold voltage.

#### **I.4. SMALL SIGNAL PARAMETERS**

These parameters are required for the small-signal analysis. In addition they are also required for linearizing nonlinear drain current models. The output conductance and transconductance, are important parameters in analog circuit design, these parameters can easily be derived from the device drain current model [10]. Under normal operation, a voltage applied to the gate, drain or substrate results in a change in the drain current. The ratio of change in the drain current  $I_{ds}$  to the change in the gate voltage  $V_{gs}$  while keeping drain voltage  $V_{ds}$  and substrate voltage  $V_{bs}$  constant is called transconductance expressed as:

$$g_m = \frac{\Delta I_{ds}}{\Delta V_{gs}} \bigg|_{V_{ds}, V_{bs}}$$

(I.4)

The transconductance is one of the important device parameters as it is a measure of device gain. Thus, the gain of a MOSFET can be increased by:

• Increasing  $C_{ox}$ , that is, using a MOSFET with a thinner gate oxide (lower  $t_{ox}$ ),

- Using devices with higher carrier mobility  $\mu$ . Since  $\mu$  of the electrons is higher than that of holes, an nMOST has higher gain compared to pMOST.

- Using devices with larger channel width *W* and shorter channel length *L*. While decreasing *L*, scaling considerations must be taken into account.

Since  $g_{m}$  is sensitive to the quality of the gate oxide (through  $\mu$  and  $V_{th}$  parameters), it is frequently used to monitor the effect of hot-carrier stress and accelerated aging on device reliability.

In addition to  $g_{m}$ , the MOSFET has two other conductances. The ratio of change in the drain current due to change in  $V_{bs}$  for a fixed  $V_{gs}$ , and  $V_{ds}$ , is called substrate transconductance  $g_{mbs}$  defined as:

$$g_{mbs} = \frac{\Delta I_{ds}}{\Delta V_{bs}} \bigg|_{V_{at}, V_{ds}}$$

(I.5)

Finally, the ratio of change in the drain current to the change in the drain voltage  $V_{ds}$  is called drain conductance or simply conductance gds given similarly by:

$$g_{ds} = \frac{\Delta I_{ds}}{\Delta V_{ds}}\Big|_{V_{gs}, V_{bs}}$$

(I.6)

Figure I.7 shows plot of  $g_m$ ,  $g_{mbs}$  and  $g_{ds}$  as a function of  $V_{gs}$  and  $V_{ds}$ , based on first order MOSFET model.

Fig. I.7. Small-signal parameters  $g_{m}$ ,  $g_{mbs}$  and  $g_{ds}$  as a function of (a)  $V_{ds}$ , and (b)  $V_{gs}$ . If all the voltages are changed simultaneously, then the corresponding total change in the drain current is:

$$\Delta I_{ds} = \frac{\partial I_{ds}}{\partial V_{gs}} \Delta V_{gs} + \frac{\partial I_{ds}}{\partial V_{ds}} \Delta V_{ds} + \frac{\partial I_{ds}}{\partial V_{bs}} \Delta V_{bs} = g_m \Delta V_{gs} + g_{ds} \Delta V_{ds} + g_{mbs} \Delta V_{bs}$$

(I.7)

If the change in the voltages is small, approaching zero, then these (trans)conductances are called small signal (trans)conductances. The small signal equivalent circuit of a MOSFET is shown in Figure I.8, where rhomic symbols represents controlled current sources.

οG

Fig. I.8. A low frequency, usually less than 1 KHz, small-signal model for a MOSFET.

### **I.5. MINIATURIZATION EFFECTS**

Producing MOSFETs with channel lengths much smaller than a micrometer is a challenge, and the difficulties of semiconductor device fabrication are always a limiting factor in advancing integrated circuit technology. In recent years, the small size of the MOSFET, below a few tens of nanometers, has created operational problems [11].

• Higher subthreshold conduction

As MOSFET geometries shrink, the voltage that can be applied to the gate must be reduced to maintain reliability. To maintain performance, the threshold voltage of the MOSFET has to be reduced as well. As threshold voltage is reduced, the transistor cannot be switched from complete turn-off to complete turn-on with the limited voltage swing available; the circuit design is a compromise between strong current in the "on" case and low current in the "off" case, and the application determines whether to favor one over the other. Subthreshold leakage (including subthreshold conduction, gate-oxide leakage and reverse-biased junction leakage), which was ignored in the past, now can consume upwards of half of the total power consumption of modern high-performance VLSI chips.

## • Increased gate-oxide leakage

The gate oxide, which serves as insulator between the gate and channel, should be made as thin as possible to increase the channel conductivity and performance when the transistor is on and to reduce subthreshold leakage when the transistor is off. However, with current gate oxides with a thickness of around 1.2 nm (which in silicon is ~5 atoms thick) the quantum mechanical phenomenon of electron tunneling occurs between the gate and channel, leading to increased power consumption.

Insulators (referred to as high-k dielectrics) that have a larger dielectric constant than silicon dioxide, such as group IVb metal silicates e.g. hafnium and zirconium silicates and oxides are being used to reduce the gate leakage from the 45 nanometer technology node onwards. Increasing the dielectric constant of the gate dielectric allows a thicker layer while maintaining a high capacitance (capacitance is proportional to dielectric constant and inversely proportional to dielectric thickness). All else equal, a higher dielectric thickness reduces the quantum tunneling current through the dielectric between the gate and the channel. On the other hand, the barrier height of the new gate insulator is an important consideration; the difference in conduction band energy between the semiconductor and the dielectric (and the corresponding difference in valence band energy) also affects leakage current level. For the traditional gate oxide, silicon dioxide, the former barrier is approximately 8 eV. For many alternative dielectrics the value is significantly lower, tending to increase the tunneling current, somewhat negating the advantage of higher dielectric constant.

### • Increased junction leakage

To make devices smaller, junction design has become more complex, leading to higher doping levels, shallower junctions, "halo" doping and so forth, all to decrease drain-induced barrier lowering. To keep these complex junctions in place, the annealing steps formerly used to remove damage and electrically active defects must be curtailed increasing junction leakage. Heavier doping is also associated with thinner depletion layers and more recombination centers that result in increased leakage current, even without lattice damage.

### • Lower output resistance

For analog operation, good gain requires a high MOSFET output impedance, which is to say, the MOSFET current should vary only slightly with the applied drain-to-source voltage. As devices are made smaller, the influence of the drain competes more successfully with that of the gate due to the growing proximity of these two electrodes, increasing the sensitivity of the MOSFET current to the drain voltage. To counteract the resulting decrease in output

resistance, circuits are made more complex, either by requiring more devices, for example the cascade and cascade amplifiers, or by feedback circuitry using operational amplifiers, for example a circuit like that in the adjacent figure Fig. I.9, where the operational amplifier provides feedback that maintains a high output resistance.

Fig. I.9. MOSFET version of gain-boosted current mirror;  $M_1$  and  $M_2$  are in active mode, while  $M_3$  and  $M_4$  are in Ohmic mode, and act like resistors.

#### • Lower transconductance

The transconductance of the MOSFET decides its gain and is proportional to hole or electron mobility (depending on device type), at least for low drain voltages. As MOSFET size is reduced, the fields in the channel increase and the dopant impurity levels increase. Both changes reduce the carrier mobility, and hence the transconductance. As channel lengths are reduced without proportional reduction in drain voltage, raising the electric field in the channel, the result is velocity saturation of the carriers, limiting the current and the transconductance.

#### • Interconnect capacitance

Traditionally, switching time was roughly proportional to the gate capacitance of gates. However, with transistors becoming smaller and more transistors being placed on the chip, interconnect capacitance (the capacitance of the wires connecting different parts of the chip) is becoming a large percentage of capacitance. Signals have to travel through the interconnect, which leads to increased delay and lower performance.

### • Heat production

The ever-increasing density of MOSFETs on an integrated circuit creates problems of substantial localized heat generation that can impair circuit operation. Circuits operate slower at high temperatures, and have reduced reliability and shorter lifetimes. Heat sinks and other cooling methods are now required for many integrated circuits including microprocessors.

Power MOSFETs are at risk of thermal runaway. As their on-state resistance rises with temperature, if the load is approximately a constant-current load then the power loss rises correspondingly, generating further heat. When the heat sink is not able to keep the temperature low enough, the junction temperature may rise quickly and uncontrollably, resulting in destruction of the device. In order to assist designers in the device selection process, a simulation tool can be used to simulate in-circuit performance.

### • Modeling challenges

Modern ICs are computer-simulated with the goal of obtaining working circuits from the very first manufactured lot. As devices are miniaturized, the complexity of the processing makes it difficult to predict exactly what the final devices look like, and modeling of physical processes becomes more challenging as well. In addition, microscopic variations in structure due simply to the probabilistic nature of atomic processes require statistical predictions. These factors combine to make adequate simulation and "right the first time" manufacture difficult.

## **I.6. EMERGENT SOLUTIONS**

Many solutions have been proposed in literature among them we have [12],

### I.6.1. High-k and metal gate integration

Low-power applications such as battery operated handheld devices require a reduced gate leakage current. To reduce the gate leakage, standard oxynitride gate insulators will be replaced by high-k dielectrics. Among the promising candidates for the 45 nm technology node are hafnium oxides (HfO<sub>2</sub>) and hafnium silicates HfSiON with a high-k value in the range 10–15, which should be compared to 3.9 for SiO<sub>2</sub> and 6–7 for the oxynitrides. This leads to significantly reduced gate leakage for the same equivalent oxide thickness. The main issues related to these types of dielectric materials, which still have to be addressed by researchers, are the high number of fixed/trapped charges and interface states. Both threshold voltage stability and low-field mobility are negatively affected by the high amount of charge present in the high-k oxides.

While the reduced mobility can be partially offset by strain enhancement techniques, the poor threshold voltage control and possible reliability problems cannot be accepted. An additional complication is the poor thermal stability of high-k materials. The dielectrics should be stable during high temperature processing steps (mainly source/drain activation anneals), since, e.g., recrystallization can increase the gate leakage current. For the ultimate scaling of CMOS, below 10 nm gate length, other high-k materials such as La<sub>2</sub>O<sub>3</sub>, with a larger k value might be of interest. The choice of suitable materials is limited by the additional constraint that the band gap offset should be large enough compared to silicon. In some cases the offset to either the conduction or valence band is too small. By considering the increased fringing field, due to the higher k value, the influence on short channel effects and switching speed can be analyzed to find an optimum k value close to 30.

High-k materials are often used in combination with different metal gate electrodes, e.g., TiN, TaN. Metal gates are important for several reasons, including the ability to control threshold voltage by tuning the work function of the gate electrode. For nitrided metal gates the tuning can be done either during the reactive sputter deposition or by subsequent nitrogen ion implantation. This allows reduced channel doping and hence higher mobility in both bulk and thin body SOI devices. Furthermore, metal gates do not suffer from depletion, compared to the case with a highly doped polysilicon gate electrode. For successful metal gate integration, selective etching processes, with high anisotropy, need to be developed for patterning of 10nm gate lengths. The use of fully nickel silicided (FUSI) polysilicon gates is more straightforward approach in this respect, since the patterning of polysilicon gates is more mature. In this case, the work function control can be achieved by dopant pile-up at the metal gate/oxide interface. The combinationof FUSI and high-k has generated a lot of attention recently.

#### I.6.2. Strain-enhanced mobility

For high-performance applications the challenge is mainly to maintain sufficiently high drive current for short-channel devices which suffer from short channel effects and high parasitic resistances. For higher drive current and increased switching speed the focus is on different methods of mobility enhancement, using strain. For CMOS applications both higher hole and electron mobility are desired. For PMOS the first attempts at increased channel mobility were done by selective SiGe epitaxy in the channel region. However, from the 90 nm technology node, selective SiGe growth in the source/drain has emerged as the preferred method to create compressive strain in the PMOS channel. Significantly increased electron mobility has also been demonstrated in NMOS devices, where a dielectric capping layer, commonly silicon

nitride, introduces a tensile strain in the channel region. In this approach the strain in both PMOS and NMOS channels becomes uniaxial, which is beneficial compared to biaxial strain. It is important to note that the NMOS and PMOS can be optimized independently of each other. Very high mobility can also be achieved for both electrons and holes using so called virtual substrates, with a thin Si-channel on top of a relaxed SiGe buffer layer. There are several issues with the virtual substrate technique, including a poor thermal conductivity and a high intentional concentration of defects (dislocations). Furthermore the mobility increase is smaller for holes, which is not advantageous for CMOS applications, where the PMOS has the most need for performance increase.

#### I.6.3. Multi-gate devices

Multi-gate MOSFETs realized on thin films are the most promising devices for the ultimate integration of MOS structures due to the volume inversion in the conductive layer, leading to an increase in the number and the mobility of electrons and holes. The on-current Ion of the MOSFET is limited to a maximum value *I*BL that is reached in the ballistic transport regime. For a given DIBL, an increased ballisticity is obtained for low doping double gate SOI devices. The transfer characteristics of several multiple-gate (1, 2, 3 and 4 gates) MOSFETs, calculated using the 3D SchrÄodinger{Poisson equation and the non equilibrium Green function (NGEF) formalism for the ballistic transport or MC simulations, have shown similar trends. The best performance (drain current, subthreshold swing) is outlined for the 4-gates (QG | quadruple gate or GAA | gate all around) structure. However, the propagation delay in triple gate (TG) and quadruple gate MOSFETs are degraded due to a strong rise of the gate capacitance. A properly designed double-gate (DG) structure appears to be the best compromise at given current (For a double gate device, the impact of a gate misalignment on the drain current is important. The impact of a gate misalignment is significant for Ion in 2G MOSFETs. A large back gate (BG) shift reduces the saturation current compared to the aligned case, whereas a slight BG shift towards the source increases Ion. This is due to a lower source access resistance. In terms of short channel effects, aligned transistors exhibit the best control while highly misaligned MOSFETs operate like single gate ones. The current is much more influenced by the misalignment than Ion due to a degradation of the electrostatic control. The oversized transistor shows attractive static performance and a larger tolerance to misalignment but the dynamic performance is rapidly degraded as the overlap length increases.

In decananometer MOSFETs, gate underlap is also a promising solution in order to reduce the DIBL effect. The on-current is almost not affected by the gate underlap whereas the leakage

currents are substantially reduced due to a decrease in DIBL and drain to gate tunneling current. A reduction of the effective gate capacitance *C*g for larger underlap values at *I*on has also been shown. This reduction of *C*g leads to a decrease in the propagation delay and power. In order to reach very high performance devices at the end of the roadmap, multi-bridge-channel MOSFETs (MBCFET) present very high driving currents larger than those of GAA devices and exceeding the ITRS requirements as given by figure Fig. I.10.

Fig. I.10. Schematic diagram of MBCFET on SOI [12].

The main advantage of multi-gate devices is their excellent electrostatic control of the channel, which reduces the short channel effects. On the other hand, since the conduction takes place in a volume instead of just one surface, these devices present higher mobility than conventional bulk MOSFETs because there is less scattering; their operation can even be near the ballistic limit for very short channel devices.

In multiple gate devices, the use of a very thin film allows to downscale the devices without the need of using high channel doping densities and gradients. In fact, undoped films can be used: the full depletion of the thin film prevents punch-through from happening. Besides, the absence of dopant atoms in the channel increases the mobility by suppressing impurity scattering. On the other hand, unwanted dispersion of the characteristics is avoided; this dispersion results from the random microscopic fluctuations in ultra-small devices.

Multiple gate nanoscale devices have many advantages in circuit performance. A very high packaging density is possible because of the small size of these devices, caused by the short channel and the thin film. Because of the higher mobility, transconductance can be higher, which gives more current gain and allows a higher operating frequency. Therefore, multiple gate nanoscale devices have a big potential for RF and microwave applications. The analog

performance is also very good. Voltage gain is much higher than in conventional bulk MOSFETs, and especially in moderate inversion: the reduction of short channel effects leads to a higher Early voltage, and on the other hand the  $g_m/I_{ds}$  characteristics have higher values than in conventional MOSFETs [13]. Regarding digital applications, the small subthreshold swing of multiple gate devices keeps a high ratio between on current and off current even for devices with channel lengths of the order of nm.

### **I.7. NANOTECHNOLOGIES**

The nanoelectronics platforms, bear a striking resemblance to the good old-fashioned silicon microelectronics, in that exploit the electrical and magnetic properties if fairly simple materials. All of the approaches discussed to date have also reached a point in their commercialization, where we can be reasonably certain that something will come of them [14]. Molectronics (sometimes called "moletronics") is different, because it has a lot further to go commercially. In fact, it isn't even all that well-defined. Indeed, molectronics is basically a catchall term for electronics that uses complex (often biological) molecules as the main materials platform. There is a considerable amount of interesting R&D in this field that is being performed in both academic and industrial laboratories that involves quantum computing or chemical computing, although this kind of molectronics is so far off in terms of commercialization, that we can so no real business opportunities emerging from this work in this decade. Instead, this kind of thing will remain in university labs or in the labs of the very largest electronics and semiconductor firms for many years to come. There is another aspect to molectronics, though, one that is closer to commercialization, and which researchers believe will present some genuine opportunities in the next five to ten years. This approach is one in which switching is based upon the change in state of individual molecules. The change can be based on conductivity as a result of an applied field (much like a classical FET), a conformational change resulting in a change of conductivity (including a complete contact break) or optical properties. In practice, devices may contain many such molecules in an individual switching unit. Although some approaches to this kind of molectronics involve radical changes in circuit design, others are more in line with conventional architectures.

All this diversity—no settled materials, designs, or architectures—is symptomatic of the early stage of development at which molectronics currently exists. Probably the closest product to commercialization that might be classified as molectronics is a memory chip from a firm called Zettacore, which uses complex molecules as material platform, but otherwise doesn't

diverge too much from standard chip designs. However, when looking further into the future, when processors and logic may be built using molectronics, molectronics will probably require significant changes in approach to design largely as a result of having to build in a fairly high level of fault tolerance [15].

Now it may be the turn of nanophotonics to add its contribution. A number of start-ups have opened their doors in this space and the European Union has just launched a large R&D program focused on exactly this area. The impact of nanophotonics is fairly diverse. NanOpto makes a range of nanoengineered polarizers, splitters, and "waveplates," using a nanoimprint lithography. Toshiba has claimed a breakthrough when it recently announced quantum dot light sources that could transmit single photons and this type of device would most probably be used in quantum encryption. It seems more likely that the first big business for nanoengineered lasers will come from chip interconnection. Until recently, the speed bottleneck in computing and telecom was the speed of the processors. In the last few years, however, the processor speed has reached a point at which it is the interconnections that are now the limiting factor. In response, semiconductor manufacturers have moved from aluminium interconnects to copper interconnects and are now experimenting with optical interconnection as well as exotic lower-k materials and carbon nanotubes. Optical interconnection could supply more than enough bandwidth to suck up and supply data to even the fastest processors. The requirements for lasers to support such an application would very demanding in terms of size and cost, but the market size is potentially huge. For on-chip applications, the lasers would have to be embedded and their value would be subsumed by that of the entire chip. But an examination of the on-board market suggests that addressable markets for nano-engineered interconnects could be huge. Consider a board with 10 devices on it. If these devices were fully interconnected, 90 lasers would be required [16].

## **I.8. CONCLUSION**

The multi-gate devices that control the channel from multiple sides and very thin body devices are new to circuit and system designers. These devices need to be modeled to understand and predict the functionality of the circuits. Compact device models are used in circuit design. New compact models that accurately model these novel devices, and are computationally efficient, are in development. There are new physical effects that now need to be incorporated into these device models.

The use of multiple gate devices in circuit design is critically dependent on the availability of accurate models for these devices. Using appropriate models, circuit simulation allows to

design circuits with devices of adequate dimensions. Circuit simulation requires accurate models of the current and the terminal charges of the devices in addition to the modeling of additional constraints.

# Chapter II –

# **DEFECTS IN MOSFET DEVICES**

*Abstract:* The hot-carrier effect is a reliability problem which occurs when hot (energetic) carriers cause Si-SiO, interface damage and/or oxide trapping. This leads to the degradation of the current drive capability of the transistor, thus eventually causing circuit failure. The origin of this degradation is the high electric field near the drain end. One of the most effective ways to control the hot-carrier effect is to include a field reducing region in the transistor structure. These regions, called the LDD (lightly doped drain) or MDD (moderately doped drain), reduce the amount of damage a device suffers, and consequently increase its operational lifetime.

This chapter is dedicated to the description of the main defects occurring in MOSFETs structure due to intrinsic anomalies or stress conditions, the hot-carrier degradation shift on the main parameters is also studied and the basic models used for the modelling of such phenomenon are presented.

## **II.1. INTRODUCTION**

A global view of today's world permits to notify that many hardware and software based systems, are characterized by complex behavior and often have special features and structures requiring high complexity approaches for modeling [17]. In such situation, this may result in many unwanted phenomena disturbing the correct function particularly when taking into account the VLSI constraints. In order to avoid the heavy costs associated with maintenance and diagnostic operations, a deep understanding of the degradation process should be established so that the reliability of such systems can be enhanced significantly. Despite that the recent progress in different fields has made resulted products more powerful than ever, the increasing level of complexity implied that reliability problems not only will continue to exist, but also are likely to require ever more innovative solutions [18].

The demand for high-performance devices has been experiencing a steady rise in the sophistication degree of semiconductor manufacturing techniques, which in turn have driven the associated MOSFET size close to their physical limits. Theoretical analyses make it clear that we should be able to rearrange atoms and molecules one by one to get more efficient tools at a tiny scale. Therefore, the initial stage consists in the seek of new design approaches for devices miniaturization scheme, the adopted approach based on keeping the internal electric fields constant had to be abandoned due to several practical reasons including [19]:

- Loss of compatibility with previous generation circuits,

- Decrease in noise margins because of the non-scaling of the threshold voltage and the subthreshold slope,

- Decrease in operating speeds in sub-micron devices due to the non-scaling of parasitic capacitances.

In this chapter, our aim is to present different types of defects that can exist in MOSFET devices, these defects are a major concern in reliability field. Therefore, their inclusion in compact models can bring deep understanding towards the resolution of many problems for integrated circuit design. The shift caused by the phenomenon in some basic parameters is also studied and the basic models used for the modeling of the hot-carrier degradation effects are presented.

# **II.2. DEFECTS CLASSIFICATION**

In spite of the effort paid up to now by the scientific community concerning Silicon and silicon based devices widely used in many fields of physics, there still remain a lot of aspects not clarified, related to the behavior of impurities, and a global understanding of their local structure and properties became increasingly important due to the reduction in chip sizes and to the increase of the operation speed [20].

Since the reliability concepts are the most popular framework allowing the good description of the system life cycle based on failures occurrence; which is mainly caused by the original existence or generation of defects in the device, it would be of great utility to analyze different evolution stages. The reliability of semiconductor devices is represented by the failure rate curve known as the "bathtub curve", depicted in figure II.1. The curve can be divided into three regions [21]:

- Initial failures are considered to occur when a latent defect is formed, then becomes manifest under the stress of operation. Generally, the period of initial failures is defined as the first six months to one year of a product cycle, the failure rate tends to decrease with time because only devices having latent defects will fail, and these devices are gradually removed.

- Random failures in which the failure rate is constant, such mode covers soft errors, electrical noise, electrostatic discharge, and other problems. All of these problems will occur at random under the stress of external factors.

- Wear-out failures occur due to the ageing of devices from wear and fatigue. This period indicates the life of different failure modes of semiconductors such as Hot carriers, electromigration and time dependant dielectric breakdown.

Fig. II.1. Failure rate curve (Bathtub Curve) of semiconductors devices.

In the screening process, if we assume a certain length of time  $(t_0)$  before device shipment, the lifetime can be forecasted by the probability density function. With the Weibull distribution density function [22], the rate of accumulated failures (t:  $t_0$ ) available after screening becomes:

$$F(t_0:t) = 1 - \exp\left(-\frac{(t_0+t)^m - t_0^m}{\eta^m}\right)$$

(II.1)

where *m* and  $\eta$  are scale and shape parameters of the Weibull distribution.

Therefore, it's possible to estimate the device lifetime basing on probabilistic exploitation of such distribution density function. The reliability based analysis highlights the necessity to improve the device lifetime through the enlargement of the random failures interval, where the failure rate is approximately constant. Hence, it's a mandatory requirement to assimilate existing defects in both extreme regions, so that abusive effects could be eliminated or at least reduced [23].

#### **II.2.1. Bulk defects**

This type of defects is closely related to the bulk structure of a semiconductor, in the sense that the trap defects are distributed over the whole volume. The resulted effect on the behavior of future produced devices has been studied intensively in literature. However, with the advance of MOSFETs technology at nanoscale level, the gap becomes more apparent and additional efforts then before should be focused on the subject.

#### Origin of the problem

The availability of semiconductor materials and their use as a basis of nanodevices have bring to the front many disadvantages related from a part to the inherit structure and from another part to production process constraints. In single crystal semiconductors, deep level used impurities have usually a metallic nature, but they can be crystal imperfections (dislocations, precipitates, vacancies, and interstitials) [24]. Such defects are in general avoidable, but occasionally they are intentionally introduced to affect a device characteristic (switching time, resistivity). For amorphous semiconductors, defects are mainly due to structural imperfections. Manufacturing environment conditions are also a key medium altering the concentration of existing impurities in the semiconductor; methods used for crystal growth such as epitaxy can give rise to deep level traps. Another recognized cause concerns several properties of employed resources; the higher static charge levels in a semiconductor fab than in a conventional room. In fact, it is not uncommon for a fab with no safeguards against static charge to achieve levels of tens of kilovolts on a variety of critical surfaces.

The existence of foreign atoms or crystal defects perturbs the periodicity of the single crystal, hence resulting in discrete energy levels into the band gap, as illustrated in figure II.2. They can be considered as recombination centers when there are excess carriers, and as generation centers when the carrier density is below its equilibrium value.

Fig. II.2. Electron energy band diagram for a semiconductor with deep-level impurities in addition to capture and emission process.

The thermodynamics of defects plays an important role in the deduction of some specific aspects, the thermodynamic parameters including band gaps, energies of defect formation and migration, are not the Eigenvalues of a Schrödinger equation describing the crystal. Such

parameters are defined statistically in terms of reactions occurring among ensembles of all possible configurations of the system.

The governing law of the equilibrium concentration of point defects introduced into a perfect semiconductor crystal is given for a neutral point defect  $X^0$  by the expression [25]:

$$\frac{\left[X^{0}\right]}{\left[S\right]} = \theta_{X^{0}} \exp\left[\frac{-G_{X^{0}}^{f}}{kT}\right]$$

(II.2)

where [S] is the concentration of available lattice sites in the crystal,  $\theta_{x^0}$  is the number of degrees of internal freedom of the defect on a lattice site, and  $G_{x^0}^f$  is the standard Gibbs free energy. The parameters k and T respectively represent Boltzmann's constant and temperature. In order to get an accurate model of the real defects equilibrium inside the bulk semiconductor, the enthalpy of formation need not refer only to elementary point defects such as interstitial, but also supports more complicated defect cluster formation encompassing a wide variety of defects including the divacancy, diinterstitial and vacancy-dopant pair, where we find in literature numerous methods for calculating the formation enthalpy of a defect pair and more progress still take place [26].

### **Characterization methods**

In order to study defect properties, several experimental techniques have been used. Some of these approaches can be extended to deal with new materials and organic semiconductors. There is no universal approach suited to all situations, so continual improvement consists a major concern. However, two basic methods have been used abundantly in experimental applications [27], the first on is deep level transient spectroscopy (DLTS) developed by Lang in 1974, it exhibits its highest performances under ideal circumstances where it can reach defect concentrations as low as 10–6 times the carrier concentration of the semiconductor. By mean of this technique, it's also possible to identify radiation induced defects.

The key feature of DLTS consists in the limitation of emission rate so that only values of the capacitance transient within this range are extracted by the measurement apparatus. With the temperature variation, a peak in the instrument response is observed at the temperature associated with the trap emission rate. The sensitivity of DLTS when used in the capacitive mode decreases linearly with the distance towards the junction. Small uncertainties in the determination of the position of a DLTS peak can cause significant errors in the evaluation of the parameters of electronic states deep within the band gap; it is difficult to distinguish defects that are very close in energy.

Although DLTS is spectroscopic in nature giving trap energies, it has some undesirable properties: namely the large effort required in sample preparation and the limitation to samples of certain doping concentrations.

The second more versatile technique known as positron annihilation spectroscopy (PAS), is the spectroscopy of gamma ( $\gamma$ ) rays emerging from the annihilation of positrons and electrons. The method is based on using the energy and momentum conservation during the annihilation process to study solids taking the advantage of parameters sensitivity to lattice imperfections (see Figure. II.3). When a positron is trapped in an open-volume defect, such as vacancies and dislocations, the annihilation parameters are modified in a characteristic way. Its lifetime increases due to the lower electron density. Momentum conservation leads to a small angular spread of the collinear  $\gamma$  –quanta or a Doppler shift of the annihilation energy [28]. Most positron lifetimes for the important semiconductors and lifetimes for various vacancy-type defects have been experimentally determined. Neutral and negative vacancy-type defects, as well as negative ions, are the dominant positron traps in semiconductors. Temperaturedependent lifetime measurements may distinguish between both defect types.

Fig. II.3. Schematic illustration of positron annihilation showing positron creation, positronelectron annihilation,  $\gamma$  emission and the main experimental techniques for PAS.

The intricate challenge facing the practical implementation of the method is the high costs of equipment not readily available to most researchers.

## II.2.2. Hot carrier

In the last years, numerous studies have been revised and enhanced to get more adequate models regarding the hot carrier induced device degradation. In fact, the phenomenon has been observed or implemented under special forms in some types of Random Access Memory cells [29]. With the recent trends in nanodevices manufacturing, condensed efforts are invested to gain higher immunity performances without altering the optimal function of the device.

# II.2.2.1. Origin of the problem

Under the bias conditions of a MOSFET structure, large electric fields are created along the device channel, as a result, carriers gain sufficiently high energies that allow their injection into the surrounding dielectric films such as the gate and sidewall oxides. The accumulation of mobile carriers at interfaces over long periods of operation can dramatically trigger many harmful physical processes causing the circuit in the worst case to fail. The hot carrier degradation process in a DG MOSFET device generates a second region having distinct properties influencing the behavior of the device as shown in figure II.4.

Fig. II.4. Creation of a damaged region in the DG MOSFET structure because of hot-carrier degradation process.

A more vigilant analysis indicates that the process takes initially place near the drain side where a drain substrate junction is created due to the formation of a pinch-off region. The lateral electric field exhibits a sharp peak in this region increasing with the shrink of channel length, as stated by figure II.5. The tunneling effect caused by the application of high drain biases, results in carriers penetration through the considered region and exhibition of nonequilibrium energy distributions. As a consequence, the concentration of energetic carriers available for injection into the oxide requires the accurate calculation of electric field distribution in silicon because of the strict dependency between both quantities.

Fig. II.5. Maximum lateral electric field at the Si-SiO<sub>2</sub> interface along the channel in MOS transistors with decreasing channel lengths.

In both n and p-channel MOSFETs, vulnerabilities towards the injection of hot carriers have been detected, electrically active defects are generated in the oxide and at the  $Si-SiO_2$ interface [30]. At advanced stages of the process, the energy gained by the carriers in the high field region of the silicon substrate induces the break of bonds associated with extrinsic or intrinsic defects in the oxide, and such rearrangement in its atomic structure is the generator factor of the device instabilities observed during the hot-carrier injection. The different mechanisms leading to MOSFET degradation are summarized on figure. II.6.

Fig. II.6. Sequence of physical mechanisms that contribute to HC-induced device degradation in MOS transistors.

#### II.2.2. 2. Device Parameter Shift

The presence of trapped charge and interface traps in the device due to HC injection directly affects the device operation. The amount of damage caused by hot-carriers is typically measured in terms of the shift in certain device-level parameters such as the threshold voltage, subthreshold slope, transconductance, and drain current obtained by performing device characterization measurements before and after HC injection. Similar techniques are also used to characterize the oxide damage resulting from other stress conditions such as high oxide fields, Fowler-Nordheim injection, and radiation exposure. However, the HC-induced device degradation differs from most of these stress conditions in the fact that the damage caused during HC injection is highly localized. On the other hand, damage caused by exposure to ionizing radiation, for example, occurs relatively uniformly throughout the oxide. The localized nature of damage caused by HC injection implies that the interpretation of shift in device parameters under such stress conditions is significantly different from cases when the damage is uniform. For example, a change in the subthreshold slope of the device is typically associated with a change in the density of interface traps if the damage is uniform. However, similar shifts in subthreshold slope can also be observed through a localized increase in trapped charge density in the oxide near the drain region. Even though advanced characterization techniques such as charge pumping measurements provide better understanding of the nature of HC induced device degradation, it is often essential to utilize device simulation tools along with the characterization experiments to gain better insight into the physical processes responsible for hot-carrier induced parameter shifts. In order to aid this process, device simulation tools must be able to model the influence of hot-carrier induced trapped charge and interface traps on the device characteristics.

The increase of interface trap charge density leads to an increase of the threshold voltage, it is observed that the variation of the threshold voltage with stressing time t follows a power law given by [31]:

$$\frac{\Delta V_{th}}{V_{th0}} = k_1 t^{n1}$$

(II.3)

It was also observed that another effect of the damage due to hot carriers consists in the drop of mobility of electrons in the inversion layer after stress. This is because with the increase of interface traps density with stress, the charge trapped at the interface traps also increases and affects the mobility of the channel carriers through Coulomb scattering. A drop in mobility and an increase of threshold voltage lead to a lower drain current in the device, the normalized variation of drain current with stress time are similar to the threshold voltage, the normalized variation of the drain current with stress time follows a power law.

As a result of the drop in the biasing current of the transistor and the channel carrier mobility, the transconductance  $g_m$  also decreases. It is possible that the degradation of mobility due to stress is the dominant factor in the decrease of both the drain current and the transconductance, which also could be the reason why coefficients of the degradation laws are close, as the dominant degradation mechanism of both is the same. The slope of the  $I_{ds}-V_{ds}$  graphs in the saturation region is known as the output conductance  $g_{ds}$  of the transistor and gds can have an important effect on the operation of CMOS analog integrated circuits. From empirical results (Figure. II.7.), it was found that this slope changes with hot carrier stress. In contrast to threshold voltage and transconductance, the variations of  $g_{ds}$  with stress time when plotted in a log–log scale shows some saturation, especially at higher stress conditions [32].

Fig. II.7. Normalized variation of the output conductance  $g_{ds}$  with stress time t.

In Table. II.1. a summary of important changes caused by hot-carrier stress is presented.

TABLE. II.1. Summary of important changes in the single NMOSFET

| Parameter                         | Direction of change |

|-----------------------------------|---------------------|

| Threshold voltage V <sub>th</sub> | Increases           |

| Drain current $I_{ds}$            | Decreases           |

| Transconductance $g_m$            | Decreases           |

| Output conductance $g_{ds}$       | Increases           |

## **II.3. DEVICE DEGRADATION MODELS**

In order to predict the device degradation due to hot-carrier injection under circuit operation, several empirical and semi-empirical models have been suggested in the past literature. This section provides an overview of some of the most popular models that are presently being used to model parameter shifts and device lifetimes.

### • Takeda and Suzuki Model

Takeda and Suzuki [33] suggested a simple time dependent model for parameter shifts based on the experiments performed under the  $I_{B;max}$  condition. In their experiments, they observed that  $\Delta V_T$  or % $\Delta$ Gm could be modeled empirically using expressions such as:

$$\% \Delta G_m = A t^n \tag{II.4}$$

where, A and n are empirical parameters extracted separately for each technology. The parameter n has a strong dependence on the gate bias used during the stressing experiments but little dependence on the drain bias. Similarly, the parameter A shows a strong dependence on the drain bias while its independent of the gate bias. In order to allow extrapolation from the drain bias used under stressing conditions to real-life drain biases, the dependence of A on the drain bias can be modeled as:

$$A\alpha \exp\left(-\frac{1}{V_{DS}}\right) \tag{II.5}$$

The simplicity of this model allows quick and easy extrapolation of device lifetimes under stressing conditions to the real-life biases. This approach has been used extensively for fast first-order benchmarking of different technologies. In the past, a duty-cycle based extension of this model has been applied to evaluate device lifetime under AC operation [34]. However, this model finds little application in predicting the dynamic degradation of present generation MOSFETs.

#### • Hu Model