# REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE MINISTERE DE L'ENSEINEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE UNIVERSITE DE BATNA

## FACULTE DES SCIENCES DE L'INGENIEUR MEMOIRE

Présenté au

#### DEPARTEMENT D'ELECTRONIQUE

Pour l'obtention du diplôme de

#### MAGISTER EN MICROELECTRONIQUE

**Option: IC Design**

Par

Samir BARRA

Ingénieur, institut d'Electronique-Université de Batna

Intitulé

# Conception et layout d'une machine d'états à base de latch $C^2MOS$ à technologie $CMOS\ 0.35\mu m$

| Dr. HOBAR Farida           | Prof. U. Constantine | Président   |

|----------------------------|----------------------|-------------|

| Dr. BOUGUECHAL Nour-Eddine | Prof. U. Batna       | Rapporteur  |

| Dr. DIBI Zohir             | M.C. U. Batna        | Examinateur |

| Dr. HAFDI Zoubeida         | M.C. U. Batna        | Examinateur |

M.C. U. Batna

Examinateur

Devant le jury constitué de :

Dr. BENHAYA Abdelhamid

## Dédicace

A mes chers parents A mes frères A mes sæurs A l'esprit de mon frère Farid A mes Amis Je dédie ce mémoire

## Remerciements

Bien que cette thèse porte mon nom, elle est véritablement le fruit de la coopération de plusieurs personnes, qui m'ont encadré, supporté, guidé tout au long de ces mois. Ce sont ces personnes que je tiens ici à remercier.

Mon directeur de thèse le professeur Nour-Eddine BOUGUECHAL le doyen de la faculté des sciences de l'ingénieur à l'université de Batna qui est été mon principal guide au cours de cette aventure. Je retiens du professeur BOUGUECHAL ses grandes qualités d'encadrement et plus généralement ses qualités humaines. Il a été une personne essentielle pour mon initiation et mon introduction au monde de la microélectronique.

Je tiens particulièrement à remercier **Mr. Otto Manck**, directeur général de la société MAZ, et professeur à l'université technique de Berlin en Allemagne, où nous avons effectué une grande partie de ce travaille, pour la confiance qu'il m'a témoignée en m'accueillant dans son équipe à Berlin et pour ce captivant sujet de recherche proposé.

Mes vifs remerciements à **Mme. Farida HOBAR**, professeur à l'université de Constantine, pour avoir accepté de présider le jury et à bien voulu prendre le temps de s'intéresser au sujet du présent mémoire.

De même à **Mr. Zohir DIBI**, docteur et chef du département d'électronique de l'université de Batna, pour sont aide, ces conseils ont été d'une grande valeur, aussi m'a til honoré de faire partie du jury.

Je tiens à remercier vivement **Mme**. **Zoubida HAFDHI**, docteur et chargé de cours à l'institut d'électronique à l'université de Batna, pour m'avoir honoré par sa présence au jury.

Je remercie également **Mr Benhaya ABDELHAMID**, chargé de cours à l'institut d'électronique, pour son aide, pour l'honneur qu'il me fait en figurant dans la composition du jury.

Je remercie également **Mr Boris**, **Radouane Jeghade**r, et **Hafiane Lamine** pour leurs conseils et leurs aides pendant le stage. Sans oublier les échanges très nombreux et très importants que j'ai eus avec mes collèges, **Souhil**, **A-Ghani**, **Hakim**. Nous avons commencé ensemble, travaillé ensemble et terminé « presque » ensemble.

Enfin, je dois une dette certaine à ma famille et à mes parents, qui ont été mes plus fidèles supporteurs et qui m'ont aidé à traverser cette période.

## Résumé

Les portes logiques dynamiques sont utilisés pour réduire la taille du layout, réduire la dissipation de puissance, augmenter la vitesse, et pour diminuer la complexité. L'idée fondamentale derrière la logique dynamique est d'utiliser l'entrée capacitive du transistor MOSFET pour stocker une charge et pour se rappeler ainsi un niveau logique pour un usage ultérieur. Le C²MOS est une famille logique combine la conception de la logique statique avec la synchronisation réalisée en employant des signaux d'horloge. Une machine d'états finis comporte une logique combinatoire et des registres. Le registre C²MOS est employé pour la conception d'une machine d'états dans la technologie 0.35µm, le registre C²MOS est un registre ingénieux basé sur le concept maître esclave, composé de deux latches C²MOS. Nous avons exploité l'outil Cadence Virtuoso pour concevoir le circuit de la machine d'états et pour dessiner leur layout .

### Abstract

Dynamic logic gates are used to reduce layout size and power dissipation, to decrease complexity, and to increase speed. The basic idea behind dynamic logic is to use the capacitive input of the MOSFET to store a charge and thus remember a logic level for use later. Clocked CMOS is a logic family that combines static logic design with the synchronization achieved by using clock signals. Finite State Machine (FSM) consists of combinational logic and registers, the C<sup>2</sup>MOS register is an ingenious based on concept master-slave register, composed by two clocked dynamic latchs, insensitive to clock overlap.

The  $C^2MOS$  register, are used to design an FSM in  $0.35\mu m$  CMOS technology, we exploit Cadence Virtuoso tools to design the state machine circuit, and to draw their full custom layout

## **SOMMAIRE**

## Introduction générale

| Organisation de la thèse                                    | 3  |  |

|-------------------------------------------------------------|----|--|

| Chapitre I : Le transistor MOS                              |    |  |

| I.1. Introduction                                           | 5  |  |

| I.2. La structure du transistor MOSFET                      |    |  |

| I.3. Le fonctionnement du transistor MOSFET                 | 7  |  |

| I.3.1. L'analyse qualitative                                | 7  |  |

| I.3.1.1. La création de la zone de la déplétion             | 7  |  |

| I.3.1.2. La formation du canal                              | 8  |  |

| I.3.1.3. Le transistor MOSFET comme une résistance variable |    |  |

| I.3.1.4. Le pincement du canal                              |    |  |

| I.4. La dérivation des caractéristiques d'I/V               |    |  |

| 1.4.1. La densité de la charge du canal :                   |    |  |

| 1.4.2. Le courant du drain                                  |    |  |

| 1.4.3. Les régions de triode et de saturation               |    |  |

| 1.4.4. La modulation de la longueur du Canal                |    |  |

| 1.4.5. L'effet du Body                                      |    |  |

| 1.5. Le transistor PMOS                                     |    |  |

| 1-6. La technologie CMOS                                    |    |  |

| 1.7.Conclusion                                              | 19 |  |

| Chapitre II : Les circuits logiques CMOS                    |    |  |

| II.1. Introduction                                          | 21 |  |

| II.2. Les portes logiques statiques                         | 21 |  |

| II.2.1. L'inverseur CMOS                                    |    |  |

| II.2.1.1. Les caractéristiques de transfert.                |    |  |

| II.2.1.2. Le point de commutation                           |    |  |

| II.2.2. Les portes complémentaires CMOS                     |    |  |

| II.2.2.2. La porte NAND à deux entrées                      |    |  |

| II.2.2.3. La porte NOR à deux entrées                       |    |  |

| II.2.2.4. Le synthèse des portes complexes CMOS             |    |  |

| II.2.3. La porte de transmission TG                         |    |  |

| II.3. Les portes logiques dynamiques                        |    |  |

| II.3.1. Le concept des circuits logiques dynamiques         |    |  |

| II.3.2. Le principe fondamental de la logique dynamique     |    |  |

| II.3.3. Les familles des circuits logiques dynamiques       | 28 |  |

| II.3.3.1. La logique C <sup>2</sup> MOS                     |    |  |

| II.3.3.2. La logique PE                                     |    |  |

| II.3.3.3. La logique Domino                                 |    |  |

| II.3.3.4. La logique NP                                     |    |  |

| II.4. Les circuits logiques séquentiels                     |    |  |

| II.4.1. Les bascules                                        |    |  |

| 11.4.1.1. La dascule KS                                     | 31 |  |

| II.4.1.2. Les bascules synchronisées                                             | 32 |

|----------------------------------------------------------------------------------|----|

| 1. La bascule JK                                                                 |    |

| 2. La bascule D                                                                  | 33 |

| 3. La bascule JK maître esclave                                                  | 34 |

| II.4.2. Latches contre registres                                                 | 35 |

| II.4.2.1 Les registres dynamiques                                                | 36 |

| 1. Le registre dynamique de porte de transmission                                |    |

| 2. Le registre dynamique C <sup>2</sup> MOS                                      |    |

| II.5. La machine d'états finies                                                  |    |

| II.5.1. Les modèles de la machine d'états finis (FSM):                           | 39 |

| II.5.2. L'Analyse des circuits séquentiels                                       |    |

| II.5.3. Le synthèse des circuits séquentiels                                     | 44 |

| II.6. Conclusion                                                                 |    |

| Chapitre III : Conception assistée par ordinateur des circuit III.1.Introduction | _  |

| III.2. Les outils CAO de la microélectronique                                    |    |

| III.2.1. Le language VHDL                                                        |    |

| III.2.2. PSpice                                                                  |    |

| III.2.3. Cadence.                                                                |    |

| III.2.4. Les simulateurs numériques                                              |    |

| III.2.5. Le simulateur ModelSim                                                  |    |

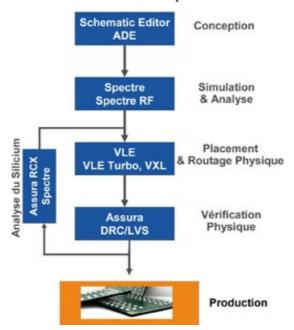

| III.3. Le flot de conception générique des circuits intégrés                     |    |

| III.3.1. Idée de conception generique des erreurs integres                       |    |

| III.3.2. Description comportementale et simulation                               |    |

| III.3.2.1. Description comportementale                                           |    |

| III.3.2.2. Description structurale                                               |    |

| III.3.2.3. Description schématique.                                              |    |

| III.3.2.4. Simulation.                                                           |    |

| III.3.3. Description Layout                                                      |    |

| III.3.3.1. Les cellules standards                                                |    |

| III.3.3.2. Le compactage                                                         |    |

| III.3.4. LVS.                                                                    |    |

| III.3.4. DRC                                                                     |    |

| III.3.6. Les fichiers CIF, GDS II                                                |    |

| III.4. Les ASIC et les circuits logiques programmables                           |    |

| III.4.1. Les ASIC                                                                |    |

| 1. A la demande                                                                  | 56 |

| 2. Prédiffusés                                                                   | 56 |

| 3. Pré-caractérisés                                                              | 57 |

| 4. A réseau structuré                                                            | 57 |

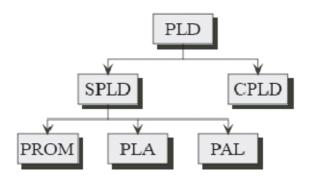

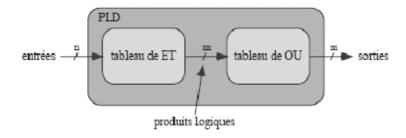

| III.4.2. Les circuits logiques programmables                                     | 58 |

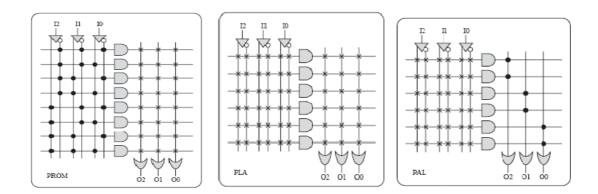

| 1. SPLD                                                                          |    |

| a. PROM                                                                          | 59 |

| b. PLA                                                                           | 59 |

| c. PAL                                                                           | 59 |

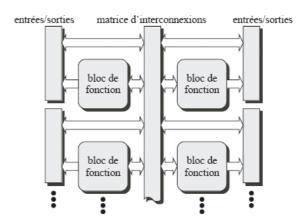

| 2. CPLD                                                                          |    |

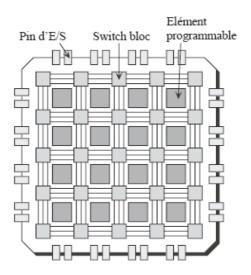

| 2.1. FPGAs                                                                       | 60 |

| III.5 Conclusion                                                                 | 61 |

## Chapitre IV : Conception d'une machine d'états à base de latches $C^2MOS$

| IV.1. Introduction                                                      |    |

|-------------------------------------------------------------------------|----|

| IV.2. La plateforme Cadence Virtuoso                                    | 63 |

| IV.2.1. Virtuoso Schematic Editor                                       | 64 |

| IV.2.2. Virtuoso Spectre Circuit Simulator                              | 64 |

| IV.2.3. Virtuoso Layout Editor                                          |    |

| IV.3. La conception du circuit de machine d'états                       | 64 |

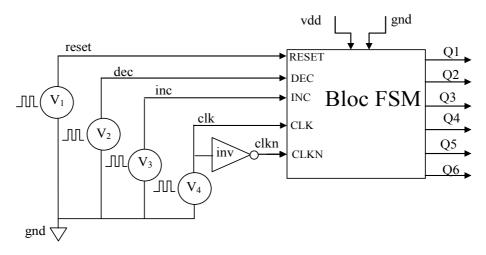

| IV.3.1. La spécification                                                |    |

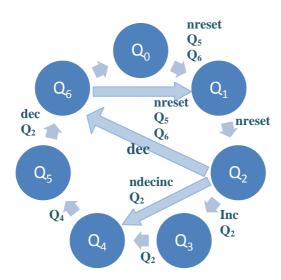

| IV.3.2. Le diagramme des états.                                         | 65 |

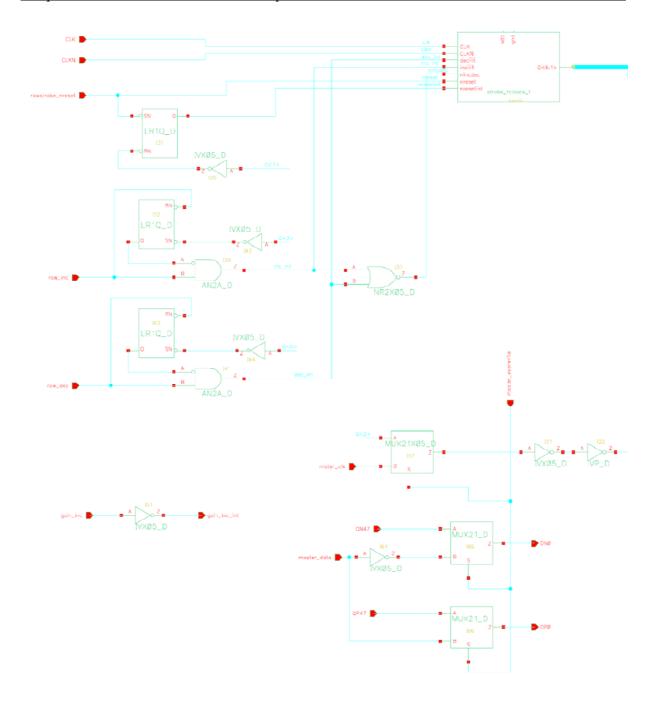

| IV.3.3. La structure de la machine d'état                               |    |

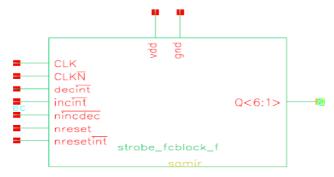

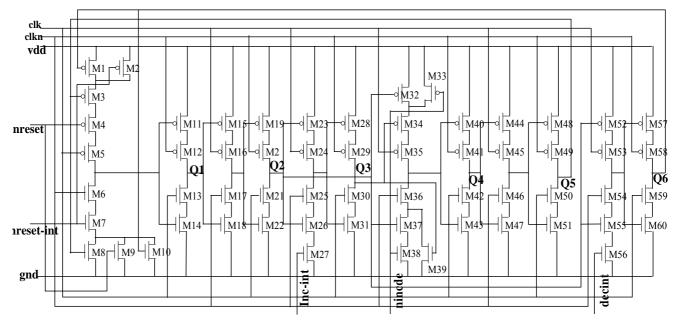

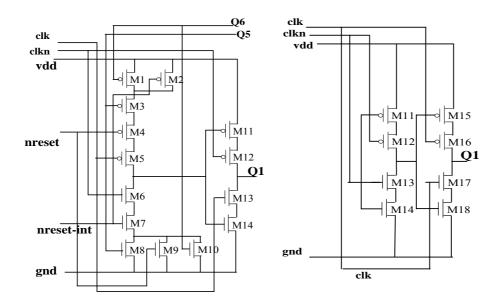

| IV.3.3.1. Le bloc de la machine d'état                                  |    |

| IV.3.3.2. La machine d'état                                             | 68 |

| IV.3.4. Le fonctionnement du circuit de la machine d'états              | 69 |

| IV.3.4 1. Le latche C <sup>2</sup> MOS                                  |    |

| IV.3.4.2 La porte logique complexe C <sup>2</sup> MOS                   | 69 |

| IV.3.4.3. Le registre C <sup>2</sup> MOS                                |    |

| IV.4. La simulation                                                     |    |

| IV.4.1. Le circuit de test bench                                        |    |

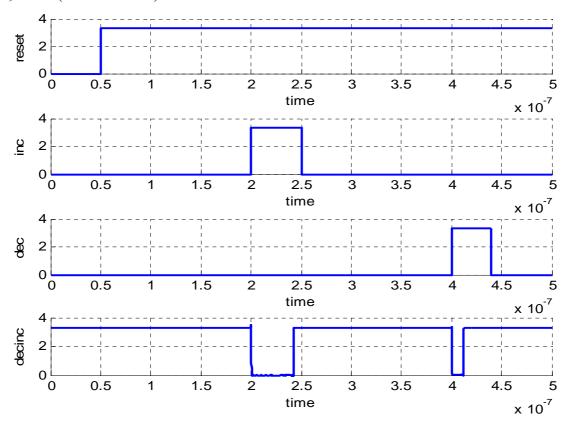

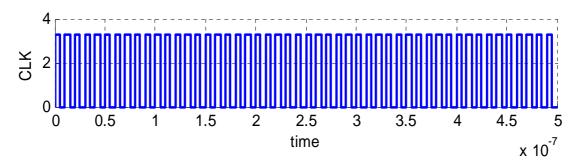

| V.4.2. Les résultats de la simulation des signaux de transition         |    |

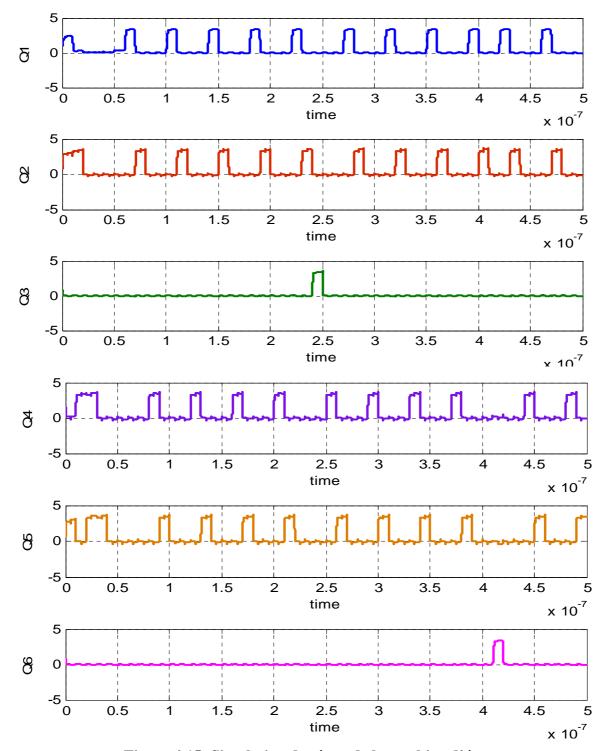

| IV.4.3. Les résultats de la simulation des états de la machines d'états |    |

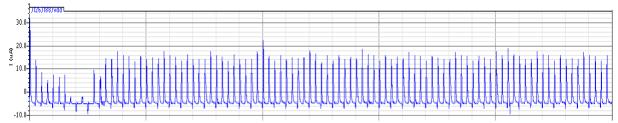

| IV.4.4. Les résultats de la simulation du courant de fuite              | 75 |

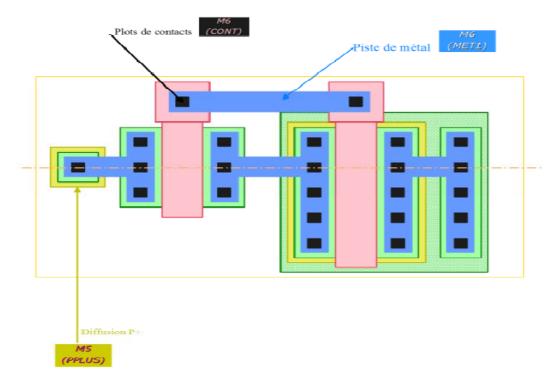

| IV.5. Le layout                                                         |    |

| IV.5.1. La conception physique des masques layout                       |    |

| IV.5.2. Le layout compact et les cellules standards                     |    |

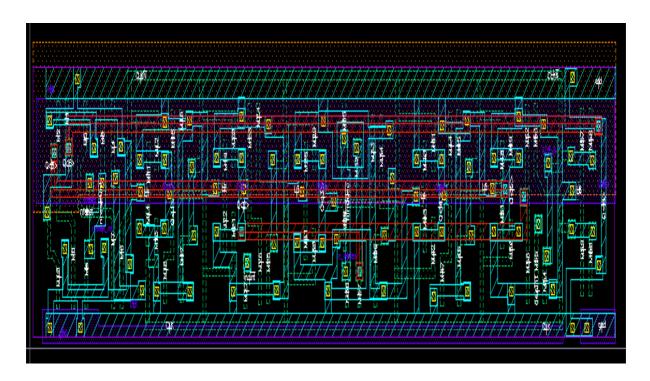

| IV.5.3.Le dessin du layout Full-Custom utilisantVirtuoso-XL             |    |

| IV.5.4. Design Rule Check (DRC)                                         |    |

| IV.5.5. Layout Versus Schematic (LVS)                                   |    |

| IV.6.Conclusion.                                                        |    |

|                                                                         |    |

| Conclusion générale                                                     |    |

| Annexe A                                                                | 83 |

| Bibliographie                                                           | 88 |

Introduction générale

#### Introduction générale

La technologie utilisée pour la production d'une puce VLSI moderne est en évolution depuis plus de quarante ans, et à bien des égards, elle évolue à un rythme exponentiel. Inventé en 1947, le transistor est à l'origine de la majorité des appareils électroniques, depuis la radio jusqu'à l'ordinateur. Aujourd'hui, il fait partie de presque toutes les technologies utilisées dans l'industrie, la médecine et l'information. Le transistor est un composant électronique formé par la jonction de cristaux de germanium, de silicium ou d'autres matériaux semblables (semi-conducteurs). Seul, le transistor peut amplifier l'énergie électrique et interrompre rapidement le passage du courant électrique à haute vitesse, tout en consommant lui-même une quantité moindre d'énergie.

L'interconnexion de plusieurs transistors, tous construits sur la même surface cristalline, permet de fabriquer de puissants circuits intégrés pouvant traiter de l'information codée électriquement. Ce sont ces circuits intégrés qui donnent leur puissance aux ordinateurs modernes, qu'il s'agisse d'un ordinateur personnel, d'un appareil électroménager ou d'un réseau de communication. À l'heure actuelle, il nous est possible d'intégrer plusieurs millions de transistors sur un seul morceau de cristal de silicium. Bien que le processus de fabrication d'un tel circuit VLSI soit remarquable en soi, les tâches liées à la conception du circuit et à la mise à l'essai de la puce manufacturée pour détecter les éventuels défauts. Il est donc essentiel, pour mieux connaître le monde de la microélectronique, de bien comprendre les concepts fondamentaux de la conception, de la mise en application et des essais des circuits VLSI.

Concevoir un circuit intégré ASIC, avec ses millions de transistors et ses interconnexions encore plus nombreuses, n'est pas une mince tâche. Aucune erreur ne peut être tolérée. Pour obtenir les résultats désirés, il est essentiel d'avoir accès à de puissants ordinateurs, appelés postes de travail, ainsi qu'à une panoplie de programmes d'automatisation de conception de circuits électroniques (CAO) fonctionnant sur ces postes de travail. Ces gros programmes peuvent générer automatiquement des circuits à partir de descriptions fonctionnelles axées sur le langage, simuler le comportement du circuit, fixer l'emplacement des transistors et le routage des éléments interconnectés à proximité de la puce et veiller à ce que tous les défauts possibles puissent être détectés durant les essais. L'utilisation de ces outils CAO se fait selon un processus de conception qu'on applique de façon rigoureuse afin de ne pas brûler les étapes. Pendant la conception, on peut consacrer de

nombreux mois à la simulation afin de déceler les erreurs, pour ensuite appliquer des mesures correctives et reprendre la simulation, mais cela augmente les chances de fabriquer dès le départ une puce qui fonctionnera correctement.

Les niveaux d'abstraction typiquement utilisés dans la conception des circuits ASIC, selon l'ordre de l'augmentation d'abstraction sont, le dispositif, le circuit, la porte, module fonctionnel (par exemple, additionneur) et le niveau du système (par exemple, processeur). Un dispositif de semi-conducteur est une entité avec a comportement très complexe. Aucun concepteur de circuit ne considérera toujours sérieusement les équations de physique de semi-conducteurs régissant le comportement du dispositif en concevant une porte numérique. Au lieu de cela il emploiera un modèle simplifié qui décrit en juste proportion le comportement d'entrée-sortie du transistor. Cette philosophie de conception a été favorisée par l'apparition de la conception assistée par ordinateur (CAO) des circuits intégrés numériques; sans elle complexité de la conception courante n'était pas réalisable. Les outils de conception incluent la simulation aux divers niveaux de complexité, vérification de conception, génération de layout, et synthèse de conception.

Afin de simplifier la conception d'un circuit AISC (une sonde ultrasonique), des méthodes de conception sont utilisées, telles que la division de la puce en plusieurs sous-circuits plus petits, la réutilisation de sous-circuits éprouvés et la reprise d'éléments de circuit pour former un sous-circuit plus complexe. L'un des sous circuits de ce circuit ASIC, est une machine d'états. La conception du circuit de la machine d'états se base sur le concept du latche C<sup>2</sup>MOS. Les circuits synchrones C<sup>2</sup>MOS fonctionnent dans ce qui s'appelle le domaine de temps. Le temps dans un circuit synchrone est quantifié et discret. L'information est gênée pour couler librement par l'état tenant des éléments ce qui ont laissé l'information propager à travers seulement aux frontières d'un intervalle discret de temps.

Cette thèse a deux objectifs principaux. Le premier est de présenter au lecteur les principes de la conception des circuits numériques ASIC. Le deuxième est d'implémenter une méthodologie de CAO des circuits logiques CMOS pour concevoir une machine d'états, exploitant la plate forme Cadence Virtuoso.

#### Organisation de la thèse

Dans le chapitre I, on s'intéressera à l'état de l'art de transistor MOS. Ensuite, une étude de sa structure et son fonctionnement permet de comprendre les paramètres de base du transistor MOS qui sont indispensables dans la conception des circuits logiques CMOS. Le concept de base de la technologie CMOS est discuté à la fin de ce chapitre.

Le chapitre II, est consacré à la conception des portes logiques statiques et dynamiques. On présentera la conception des circuits séquentiels et en particulier le concept des circuits C<sup>2</sup>MOS, divers aspects de conception des bascules, latches et registres seront discutés. Enfin on conclura ce chapitre par une étude théorique des la machines d'états.

Le chapitre III décrira quelques CAO utilisés dans la conception des circuits logiques ASIC, ainsi il présentera le flot de conception générique du circuit numérique.

Enfin le dernier chapitre, illustra la structure de la machine d'états, son principe de fonctionnement, et les étapes de sa conception tel que la spécification, la simulation, le dessin des masques 'Layout'.

#### I.1. Introduction

Aujourd'hui le domaine de la microélectronique est dominé par un type de dispositif appelé transistor MOSFET. Conçu dans les années 30 mais réalisé dans les années 60, les transistors MOSFET (également appelés les dispositifs MOS) offrent les seules propriétés qui ont menés à la révolution de l'industrie de semi-conducteur. Cette révolution a abouti aux microprocesseurs ayant 100 millions de transistors, des puces de mémoire contenant des milliards de transistors, et des circuits de communication sophistiquées fournir une capacité énorme de traitement de signal. Dans ce chapitre nous présenterons l'état de l'art du transistor MOSFET, et nous analyserons la structure et le fonctionnement des MOSFETs.

#### I.2. La structure du transistor MOSFET

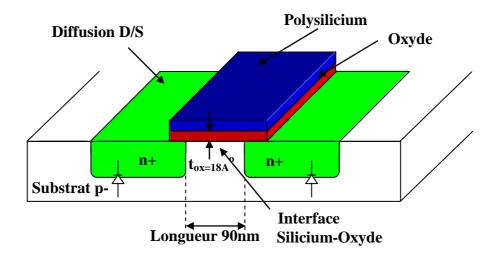

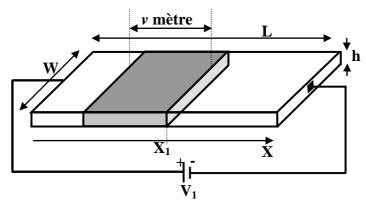

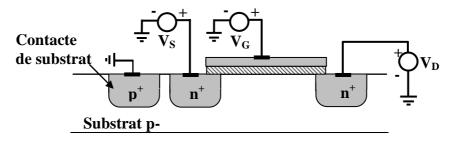

La structure du transistor MOSFET es montrée dans la figure 1.1(a) .La plaque conductrice supérieure appelée la "grille" (G) réside sur une couche diélectrique mince (isolateur), qu'elle-même est déposée sur une autre couche sous jacente de silicium type p "substrat".

Pour permettre au courant de traverser le matériel de silicium, deux contacts sont attachés au substrat à travers deux régions n fortement dopés, parce que la connexion directe du métal au substrat ne produirait pas un bon contact "ohmique". Ces deux bornes s'appellent la "source" (S) et le "drain" (D) pour indiquer que le premier peut fournir des porteurs de charge et le dernier les absorbent.

La figure 1.1 (a) indique que le dispositif est symétrique par rapport S et D ; c.-à-d, dépendant aux tensions appliquées au dispositif, l'une ou l'autre de ces deux bornes peut drainer les porteurs de charge de l'autre. Comme sera expliqué dans la section 1.3, avec la source, le drain type n et le substrat type p, ce transistor fonctionne avec des électrons plutôt que des trous et s'appelle donc un dispositif MOS type n (NMOS).

Le type p (PMOS) contrepartie est étudié dans la section 1.5. Pour la simplicité nous dessinons le dispositif comme montré dans la figure. 1.1 (b). Le schéma 1.1 (c) représente le symbole de circuit pour un transistor NMOS, où la flèche signifie la borne source [1].

<u>Chapitre I</u>

<u>Le transistor MOS</u>

Figure 1.1: La structure de transistor MOSFET(a), Une vue de côté (b), Le symbole de circuit (c)

Avant d'étudier le fonctionnement du transistor MOSFET, nous examinons le type des matières employés dans le dispositif. La grille doit servir de bon conducteur et a été réalisé par le métal (aluminium) dans les premières générations de la technologie MOS. Cependant, on l'à découvert que le silicium non cristallin "polysilicium" ou simplement "poly" avec un fort dopage (pour une faible résistivité) expose une meilleure fabrication et des excellentes propriétés physiques. Les transistors MOSFETs d'aujourd'hui utilisent des grilles de polysilicium. La couche diélectrique serrée entre la grille et le substrat joue un rôle critique dans le fonctionnement des transistors et elle est créée en accroissant le bioxyde de silicium (où simplement "oxyde") au dessus de la surface de silicium.

Les régions n<sup>+</sup> s'appellent parfois source et/ou drain de "diffusion," se rapportant à une méthode de fabrication employée aux jours tôt de la microélectronique. Nous devrions également remarquer que ces régions forment ont faite des diodes avec le substrat de type p (figure. 1.2). Comme le fonctionnement approprié du transistor sera expliqué plus tard, il exige que ces jonctions demeurent polarisées en inverse. Ainsi, seulement la capacité de région de déplétion liée aux deux diodes doit être prise en considération. La figure 2.2 montre certaines dimensions de dispositif dans l'état de l'art d'aujourd'hui de la technologie MOS. L'épaisseur de l'oxyde est dénotée par t<sub>ox</sub>.

Figure 1.2: La dimension typique des transistors MOSFET d'aujourd'hui

#### I.3. Le fonctionnement du transistor MOSFET

Cette section traite une multitude de concepts liés aux transistors MOSFET.

#### I.3.1. L'analyse qualitative

Notre étude des structures simples montrées dans les figures.1.1 suggère que le transistor MOSFET puisse conduire le courant entre la source et le drain si un canal des électrons est créé par l'application d'une tension de grille suffisamment positive. De plus, nous comptons que la magnitude du courant peut être commandée par la tension de la grille. Notre analyse confirmera en effet ces conjectures tout en indiquant d'autres effets subtils dans le dispositif. Noter que la borne grille ne passe aucun courant (de basse fréquence) comme elle est isolée du canal par l'oxyde [1].

#### I.3.1.1. La création de la zone de la déplétion

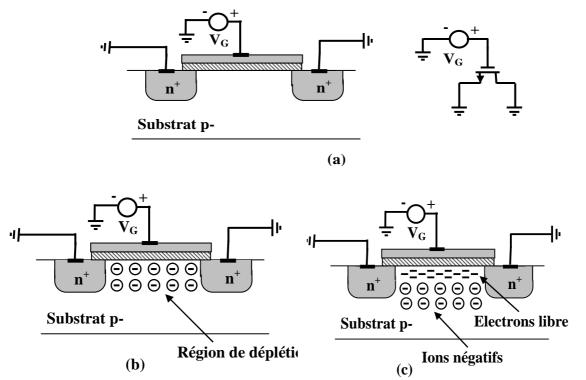

D'abord considérons l'arrangement montré dans figure. 1.3 (a), où la source et le drain sont à la masse et la tension de la grille est changée. Ce circuit ne semble pas particulièrement utile mais il nous donne beaucoup de perspicacité.

Comme  $V_G$  s'augmente, la charge positive sur la grille doit être reflétée par la charge négative dans le substrat. Tandis que les électrons sont attirés à une interface, en réalité, un autre phénomène précède la formation du canal. À mesure que  $V_G$  augmente de zéro, la charge positive sur la grille repousse les trous dans le substrat, ainsi exposant les ions négatifs et créant de ce fait une région déplétion figure. 1.3(b).

Noter que le dispositif agit toujours en tant qu'une charge condensateur charge positive sur la grille est reflétée par la charge négative dans le substrat mais aucun canal de charge mobile est créé encore. Ainsi, aucun courant ne peut découler de la source vers le drain. Nous disons que le transistor MOSFET est bloqué.

#### I.3.1.2. La formation du canal

Qu'est ce qui ce passe quant  $V_G$  augmente? Pour refléter la charge sur la grille, beaucoup des ions négatifs sont exposés et la région de déplétion sous l'oxyde devient plus profonde. Est ce que ça veut dire que le transistor ne fonctionnera jamais ?! Heureusement, si  $V_G$  devient suffisamment positif, des électrons libres sont attirés à l'interface d'oxyde de silicium, formant un canal conducteur figure. 1.3(c).

Nous disons que le transistor MOSFET est fonctionné. Le potentiel de la grille auquel le canal commence à apparaître s'appelle la "tension de seuil," V<sub>TH</sub>, et tomber dans la gamme de 300 mV à 500 mV. Noter que les électrons sont aisément fournis par les régions n<sup>+</sup> de la source et de drain, et ils n'ont pas besoin d'être fourni par le substrat.

Il est intéressant de reconnaître, que la borne grille du transistor MOSFET ne passe aucun courant (de basse fréquence). La grille reposant sur l'oxyde, reste isolée des autres bornes et simplement fonctionne comme un condensateur plat.

Figure 1.3 : Le transistor MOSFET avec la tension de la grille (a), La formation de la région de déplétion (b), La formation du canal (c).

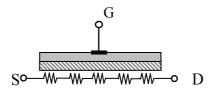

#### I.3.1.3. Le transistor MOSFET comme une résistance variable

Le canal conducteur entre S et D peut être vue comme résistance. En outre, puisque la densité des électrons dans le canal doit augmenter pendant que V<sub>G</sub> devient plus positif, la valeur de cette résistance change avec la tension de la grille .Conceptuellement illustré dans la figure. 1.4, tellement cette résistance dépendante de la tension, ce qui preuve son utilisation extrêmement dans les circuits analogiques et numériques.

Figure 1.4 : Le transistor MOSFET vu comme résistance dépendante de la tension

#### I.3.1.4. Le pincement du canal

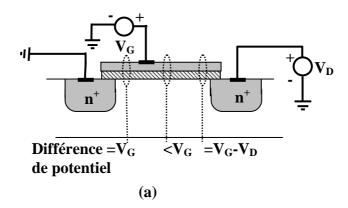

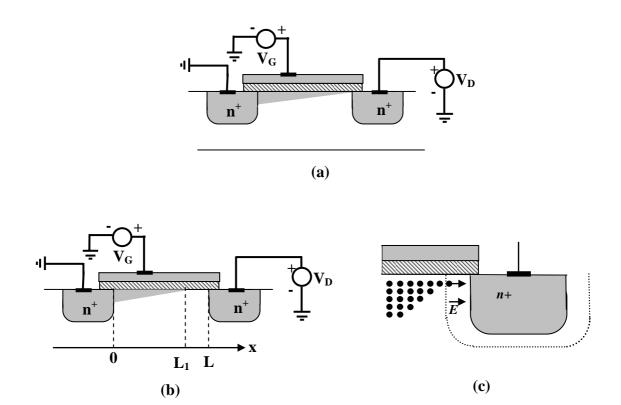

Notre étude qualitative du transistor MOSFET implique jusqu'ici que le dispositif agit en tant que résistance dépendante de la tension si la tension de grille excède  $V_{TH}$ . Cependant, en réalité le transistor fonctionne comme source de courante si la tension de drain est suffisamment positive. Pour comprendre cet effet, nous faisons deux observations :

- (1) pour former un canal, la différence de potentielle entre la grille et l'interface d'oxyde de silicium doit excéder  $V_{\rm TH}$

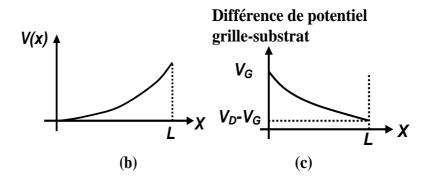

- (2) si la tension de drain reste plus élevée que la tension de source, puis la tension à chaque point le long du canal par rapport a la masse augmente quand nous allons de la source vers le drain. Illustré dans la figure. 1.5 (a), cet effet résulte de la chute graduelle de la tension le long de la résistance du canal. Puisque la tension de la grille est constante (parce que la grille est conductrice mais aucun courant ne passe dans n'importe quelle direction), et puisque le potentiel à l'interface d'oxyde du silicium monte de la source au drain, la différence de potentielle entre la grille et l'interface d'oxyde de silicium diminue le long de l'axe des abscisses figure. 1.5 (b).La densité des électrons dans le canal suit la même tendance, diminuant à un minimum à x = L.

Figure 1.5 : La variation de potentielle du canal (a), La différence de tension de grillesubstrat le long du canal (b)

De ces observations, nous concluons cela, si la tension de drain doit être assez haute pour produire $V_G - V_D \le V_{TH}$ , alors le canal cesse d'exister près du drain. Nous disons que la différence du potentielle de grille - substrat n'est pas suffisante à x = L pour attirer des électrons et le canal "est pincé " figure 1.6 (a).

Qu'est ce qui se produit si  $V_D$  s'augmente encore plus haut que  $V_G$ - $V_{TH}$ ?

Puisque V(x) va maintenant de 0 en x=0 à  $V_D>V_G-V_{TH}$  en x=L, la différence de tension entre la grille et le substrat chute à  $V_{TH}$  à un certain point L1 < L figure. 1.6 (b). Le dispositif ne contient donc aucun canal entre L1 et L.

Et est ce que ça veut dire que le transistor ne peut pas conduire le courant ?

Non, le dispositif encore conduit, Comme illustré dans figure 1.6 (c), une fois que les électrons atteignent l'extrémité du canal, ils éprouvent le champ électrique élevé dans la région de déplétion, entourant la jonction de drain et ils sont rapidement balayés à la borne de drain. Néanmoins, comme sera montré dans la prochaine section, la tension de drain n'affecte plus le courant d'une manière significative, et le transistor MOSFET agit en tant que source de courant constant semblable à un transistor bipolaire dans la région active [2].

Figure 1.6 : Le pincement (a), La variation de longueur avec la tension de drain(b), Le fonctionnement détaillé près du drain (c)

#### I.4. La dérivation des caractéristiques d'I/V

Avec l'étude qualitative antérieure, nous pouvons maintenant formuler le comportement des transistors MOSFET en termes de leurs tensions des bornes.

#### 1.4.1. La densité de la charge du canal :

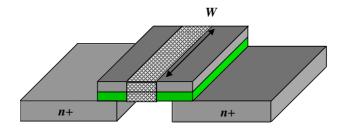

Nos dérivations exigent une expression pour la charge de canal (c.-à-d, les électrons libres) par unité de longueur, également appelée " la densité de charge " Q=C.V, nous notons que si C est la capacité de la grille par unité de longueur et V la différence de tension entre la grille et le canal, alors Q est la densité de la charge désirée. On dénote la capacité de la grille par unité de superficie  $C_{ox}$  (exprimé en F/m² ou fF/m²), nous écrivons  $C=W.C_{ox}$  pour considérer la largeur du transistor figure. 1.7. De plus nous avons  $V=V_{GS}-V_{TH}$  parce qu'aucune charge mobile n'existe pour  $V_{GS}<V_{TH}$ , (Ci-après, nous dénotons les deux tensions de la grille et du drain par rapport à la tension de la source), elle suit cela :

$$Q = W. Cox(V_{GS} - V_{TH})$$

(1.1)

Figure 1.7 : Illustration de la capacité par unité de longueur.

La tension du canal se varie le long du transistor, et la densité de charge diminue allant de la source vers le drain. Ainsi, l'Eq. (1.1) est valide seulement près de la borne de source, où le potentiel de canal demeure de près de zéro. Comme il est montré dans fig. 1.8, nous dénotons le potentiel du canal à x par V(x) et nous écrivons :

$$Q(x) = W.C_{ox}[V_{GS} - V(x) - V_{TH}]$$

(1.2)

Notons que V(x) va de zéro à V<sub>D</sub> si le canal n'est pas pincé.

Figure 1.8 : Le dispositif qui illustre le calcul de courant de drain

#### 1.4.2. Le courant du drain

Quelle est la relation entre la densité de charge mobile et le courant ?

Considérer une barre du semi-conducteur ayant un égal uniforme de densité de charge (par unité de longueur) égal à Q et portant un courant I figure. 1.9.

Figure 1.9 : La relation entre la densité de charge et le courant

Noter que:

1 - I est donné par toute la charge qui traverse une section de la barre dans une seconde.

2 - et si les porteurs se déplacent avec une vitesse de v m/s, alors la charge incluse dans v mètres le long de la barre, et traverse le secteur dans une second. Puisque la charge incluse dans v mètres est égal à  $\mathbf{Q}.v$ , nous avons :

$$I = Q.v \tag{1.3}$$

Et on a

$$V = -\mu n E; (1.4)$$

$$V = +\mu n \frac{dV}{dx} \tag{1.5}$$

Où dV/dx dénote la dérivée de la tension à un point donné. Nous combinaisons (1.2), (1.3), et (1.5), nous obtenons

$$I_{D} = WC_{ox}[(V_{GS} - V(x) - V_{TH}]\mu_{n} \frac{dV(x)}{dx}$$

(1.6)

Puisque  $I_D$  doit demeurer constant le long du canal, V(x) et dV(x)/dx doit varier tels que le produit  $\mathbf{V}_{GS}$ - $\mathbf{V}(\mathbf{x})$ - $\mathbf{V}_{TH}$  et  $d\mathbf{V}/d\mathbf{x}$  est indépendant de x. Tandis qu'il est possible de résoudre l'équation ci-dessus pour obtenir V(x) en fonction de  $I_D$ , notre besoin immédiat doit trouver une expression pour  $I_D$  en fonction des tensions des bornes .À cet effet, nous écrivons .

$$\int_{x=0}^{x=L} I_D dx = \int_{V(x)=0}^{V(x)=V_{DS}} \mu_n C_{ox} W[V_{GS} - V(x) - V_{TH}] dV$$

(1.7)

C'est

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} \left[ 2(V_{GS} - V_{TH}) V_{DS} - V_{DS}^2 \right]$$

(1.8)

Nous examinons maintenant cette équation importante de différentes perspectives pour gagner plus de perspicacité. D'abord, la dépendance linéaire de  $I_D$  sur le  $\mu$ n, le  $C_{ox}$ , et le W/L doit être prévue : une mobilité plus élevée rapporte a un plus grand courant pour une tension donnée de drain -source ; une capacité plus élevée Grille Oxyde mène à un plus grand densité d'électron dans le canal pour une tension donnée de grille -source ; et un plus grand W/L (appelé le dispositif à aspect de rapport) est équivalent à placer plus de transistors en parallèle.

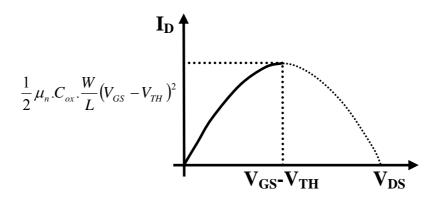

En second lieu, pour un  $V_{GS}$  constant,  $I_D$  se varie paraboliquement avec  $V_{DS}$  figure. 1.10, et atteignant un maximum de :

$$I_{D,max} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2$$

(1.9)

Figure 1.10 : Caractéristique parabolique de I<sub>D</sub>-V<sub>DS</sub>.

À  $V_{DS}=V_{GS}-V_{TH}$ . Il est commun à l'écriture W/L comme le rapport des deux valeurs par exemple,  $5\mu m$  /  $0.18\mu m$  (plutôt que 27.8) pour insister l'importance de choix de W et de L. Tandis que seulement le rapport apparaît dans beaucoup d'équations de MOS, la valeur individuelle de W et L devient également critique dans la plupart des cas. Par exemple, si les deux valeurs de W et le L sont doublées, le rapport demeure sans changement mais les augmentations de capacité de grille.

La relation non linéaire entre  $I_D$  et le  $V_{DS}$  indique que le transistor ne peut pas généralement être modelé comme résistance linéaire simple.

Cependant, si  $V_{DS} << 2(V_{GS} - V_{TH})$ , l'Eq. (1.8) est réduite à :

$$I_{D} \approx \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{TH}) V_{DS}$$

(1.10)

$I_D\text{-}V_{DS}$  s'expose un comportement linéaire pour un  $V_{GS}$  donné. En effet, la résistance équivalente est donnée par  $V_{DS}/I_D$ :

$$R_{on} = \frac{1}{\frac{1}{2}\mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}$$

(1.11)

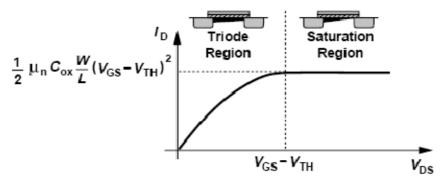

#### 1.4.3. Les régions de triode et de saturation

L'équation (1.8) exprime le courant de drain en fonction des tensions des bornes de dispositif, impliquant que le courant commence à chuter pour  $V_{DS} > V_{GS} - V_{TH}$ . Nous disons que le dispositif fonctionne dans "la région de triode" si  $V_{DS} < V_{GS} - V_{TH}$  (la section qui augmente de la parabole). Nous employons également le terme "région de triode profonde" pour le  $V_{DS} < < 2(V_{GS} - V_{TH})$ , où le transistor fonctionne comme une résistance [2].

En réalité, le courant de drain atteint, "la saturation " c'est-à-dire, devient constant pour  $V_{DS}>V_{GS}-V_{TH}$  figure. 1.11.

Figure 1.11 : Caractéristique globale du MOS.

Pour comprendre pourquoi, rappeler de figure 1.6 que le canal éprouve le pincement si  $V_{DS}=V_{GS}-V_{TH}$ . Ainsi, de plus un accroissement de  $V_{DS}$  décale simplement le point de pincement légèrement vers le drain. En outre, rappeler que les Eqs. (1.6) et (1.7) sont valides seulement où la charge du canal s'existe.

Elle confirme que l'intégration dans (1.7) doit entourer seulement le canal, c.-à-d., de x=0 à x=L1 dans la figure 2.6 (b), et soit modifiée selon

$$\int_{x=0}^{x=L_1} I_D dx = \int_{V(x)=0}^{V(x)=V_{GS}-V_{TH}} \mu_n C_{ox} W[V_{GS}-V(x)-V_{TH}] dV$$

(1.12)

Noter que les limites supérieures correspondent au point de pincement du canal . En particulier, l'intégrale du côté droit est évaluée jusqu'à  $V_{GS}$  -  $V_{TH}$  plutôt qu'à  $V_{DS}$ .

En conséquence,

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2$$

(1.13)

Un résultat indépendant de  $V_{DS}$  et identique à  $I_{D, max}$  dans (1.9) si nous assumons  $L_1 \approx L$ . la quantité  $V_{GS}$ – $V_{TH}$  appelé la "tension de overdrive, "joue un rôle principal dans les circuits MOS. Des transistors MOSFET s'appellent parfois les dispositifs "loi carrée" pour souligner le rapport entre  $I_D$  et l'overdrive. Pour la brièveté, nous dénotons ci-après L1 avec L.

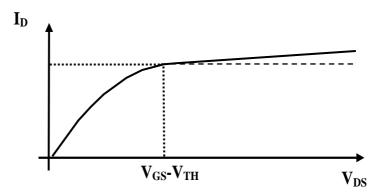

#### 1.4.4. La modulation de la longueur du Canal

Dans notre étude de l'effet de pincement, nous avons observé que le point auquel le canal disparaît quand on fait des mouvements vers la source à mesure que la tension de drain augmente. En d'autres termes, la valeur de L1 dans la figure. 1.6 (b) change avec  $V_{DS}$  dans une certaine mesure. Ce phénomène appelée la "modulation de la longueur du canal" est illustré dans fig. 1.12, il rapporte un plus grand courant de drain à mesure que  $V_{DS}$  augmente parce que  $I_D$   $\alpha$  1/L1 dans Eq. (1.13). Semblable a l'effet Early dans les éléments bipolaires, la modulation de la longueur de canal a comme conséquence est une impédance finie de sortie donnée par l'inverse de la pente  $I_D$ - $V_{DS}$  dans fig. 1.12.

Figure 1.12 : La variation d'I<sub>D</sub> dans la région de saturation.

Pour expliquer la modulation de la longueur du canal, nous supposons que L est constant, mais multiplier le membre droite de l'eq. (1.13) par une limite corrective:

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 + \lambda V_{DS})$$

(1.14)

Où  $\lambda$  s'appelle "coefficient de modulation de longueur de canal" c'est seulement une approximation, cette dépendance linéaire de  $I_D$  sur  $V_{DS}$  fournit toujours beaucoup de perspicacité sur l'implication de la modulation de longueur de canal dans la conception des circuits [1].

#### 1.4.5. L'effet du body

Dans notre étude des transistors MOSFET, nous avons supposé que la source et le substrat (également appelé le "bulk" ou le "body") sont attachés à la masse .Cependant, cette condition n'a pas besoin de la tenir dans tous les circuits. Par exemple, si la borne de source est montée à une tension positive tandis que le substrat est toujours à zéro, donc la jonction de source substrat reste polarisée en inverse, et le dispositif encore fonctionne correctement [1].

Le schéma 1.13 illustre ce cas. La borne de source est attachée à un potentiel  $V_S$  par rapport à la masse tandis que le substrat est mettre à la masse, par un contact  $p^+$ . La ligne tirée supplémentaire, ou le symbole de transistor indique la borne de substrat. Nous dénotons la différence de tension entre la source et le substrat (bulk) par  $V_{SB}$ .

Figure 1.13 : L'effet de body

Un phénomène intéressant se produit pendant que la différence de potentielle de source substrat part de zéro : la tension de seuil du dispositif change .En particulier, comme la source

devient plus positive par rapport au substrat,  $V_{TH}$  augmente. Ce phénomène appelé "L'effet du corps," est formulé comme suite :

$$V_{TH} = V_{TH0} + \gamma \left( \sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|} \right)$$

I.15

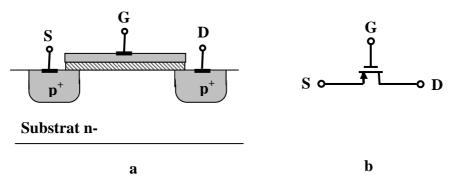

#### 1.5. Le transistor PMOS

Comme dans les transistors bipolaires, il y a le NPN et le PNP, on peut se demander si un type p contre parti existe pour les transistors MOSFET. En effet, comme illustré dans la figure. 1.14 (a), le changement des polarités de dopage du substrat et des régions S/D avoir un résultat, d'un dispositif "PMOS".Le canal maintenant se compose des trous et est formé si la tension de la grille est au-dessous du potentiel de la source par une tension de seuil. C'est-à-dire, pour que le dispositif conduit,  $V_{GS} < V_{TH}$ , où  $V_{TH}$  lui-même est négatif. Nous dessinons le dispositif de PMOS comme dans figure. 1.14 (b), avec la borne de la source identifiée par la flèche et placé au dessus pour souligner son potentiel plus élevé. Le transistor fonctionne dans la région de triode si la tension de drain est près du potentielle de la source, il s'approche de la saturation quand  $V_D$  chute à  $V_G - V_{TH} = V_G - |V_{TH}|$

Figure 1.14: (a) La structure de dispositif PMOS, (b) Le symbole de circuit

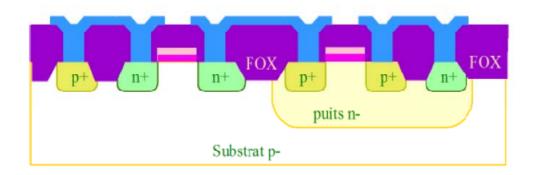

#### 1-6. La technologie CMOS

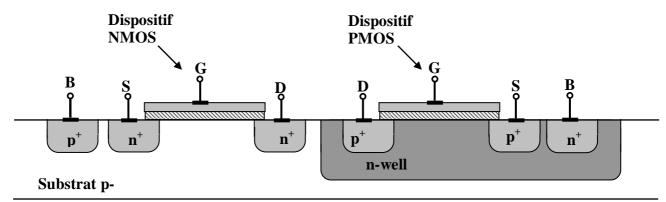

La technologie CMOS est une technologie planaire destinée au développement des systèmes à très haute échelle d'intégration (VLSI). Grâce aux propriétés des transistors MOS complémentaires (notées CMOS pour Complementary Metal Oxyde Silicon), cette technologie permet de réaliser des circuits à faible coût et à basse consommation. Cet avantage à lui permis d'être reconnue comme la technologie de pointe la plus avancée et la plus maîtrisée dans le domaine de la micro-électronique.

Est-il possible d'établir des dispositifs NMOS et PMOS sur le même dispositif?

Les figures 1.1 (a) et 1.14 (a) indiquent que les deux dispositifs exigent des différents types de substrat. Heureusement, un substrat local type n peut être créé dans un substrat type p, de ce fait adoptant des transistors PMOS, comme il est illustré dans la figure. 1.15, un "n well" enferme un dispositif PMOS tandis que le transistor NMOS réside dans le substrat p.

Figure 1.15: technologie CMOS

La structure ci-dessus appelée La technologie" CMOS " (complementary MOS), exige plus traitement complexe que les dispositifs simples NMOS ou PMOS. En effet, les premières générations du la technologie MOS a contenu seulement des transistors NMOS, et le coût plus élevé de processus CMOS a semblé prohibitif. Cependant, beaucoup d'avantages significatifs des dispositifs complémentaires par la suite rendre la technologie CMOS dominante et la technologie NMOS dépassé.

#### I.7. Conclusion

Une source du courant dépendante de la tension peut former un amplificateur avec une résistance de charge.

Les transistors MOSFETs sont des dispositifs électroniques qui peuvent fonctionner en tant que des sources du courant dépendantes de la tension.

Le transistor MOSFET se compose d'une plaque conductrice (la "grille ") placé sur un substrat semi-conducteur, et de deux jonctions ("source" et "drain") placés dans le substrat. La grille contrôle le flux du courant de la source au drain. La grille passe un courant presque zéro parce qu'une couche d'isolation la sépare du substrat.

Au delà d'une certaine tension de grille-source (la "tension de seuil"), des porteurs mobiles sont attirés à l'interface d'oxyde-silicium et à un canal est formé.

Si la tension de drain-source est petite, le dispositif fonctionne comme une résistance dépendante d'une tension.

Quand la tension de drain monte, la densité de charge près du drain chute. Si la tension de drain atteint un seuil supérieur à la tension de grille, le canal cesse d'exister près du drain, menant au "pincement ".

Le transistor MOSFET fonctionne dans la région "triode" si la tension de drain est supérieure à un seuil de la tension de grille. Dans cette région, le courant de drain est une fonction de  $V_{GS}$  et  $V_{DS}$ . le courant est également proportionnel au rapport hauteur/largeur de dispositif, W/L.

Le transistor MOSFET entre la "région de saturation" si le pincement du canal se produit, c.-à-d., la tension du drain est inferieur à un seuil du voltage de grille. Dans cette région, le courant de drain est proportionnel à  $(V_{GS} - V_{TH})^2$ .

Les transistors MOSFET fonctionnant dans la région de saturation se comportent comme des sources de courant et trouvent une large application dans les circuits microélectroniques.

Quand la tension de drain excède  $V_{GS}$  - $V_{TH}$  et le pincement se produit, l'extrémité de drain du canal commence à se déplacer vers la source, réduisant la longueur utile du dispositif. Appelé la "modulation de longueur du canal" cet effet mène à la variation du courant de drain dans la région de saturation. C'est-à-dire, le dispositif n'est pas une source de courant idéale.

Les transistors NMOS et PMOS sont fabriqués sur le même substrat pour créer la technologie CMOS.

## Chapitre II: Les circuits logiques CMOS

#### II.1. Introduction

Il est pratiquement impossible de trouver des dispositifs électroniques dans nos vies quotidiennes qui ne contiennent pas des circuits numériques. Des montres et des appareils photo aux ordinateurs et aux téléphones cellulaires, les circuits numériques représentent plus de 80% du marchée de semi-conducteur. Les exemples incluent des microprocesseurs, mémoires, et CI de traitement de signal numérique.

Ce chapitre sert d'introduction à l'analyse et à la conception des circuits numériques CMOS. L'objectif est de fournir une compréhension détaillée du niveau transistor des portes logiques, afin de préparer sur la conception des circuits numériques.

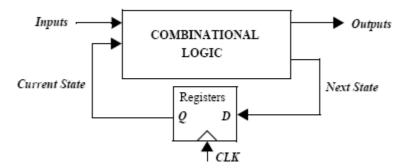

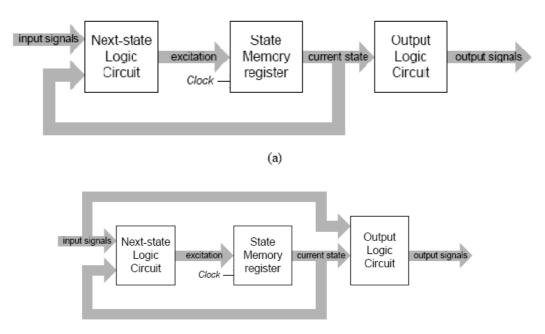

La conception logique de base des systèmes numériques utilise des modules tels que des portes, latches, et des bascules. Les portes logiques peuvent former un circuit "combinatoire" qui fonctionne comme un décodeur binaire Gray, de même, les portes et les bascules et peuvent comporter un circuit "séquentiel" qui sert comme compteur ou "machine d'état fini." Dans ce chapitre, nous étudions la conception interne de certains de ces modules et analyser leurs limitations.

#### II.2. Les portes logiques statiques

Le style logique le plus largement utilisé est le style statique complémentaire CMOS; il est vraiment une extension de l'inverseur statique CMOS à des entrées multiples.

Le style des circuits MOS complémentaire tombe sous une large classe des circuits logiques appelés circuits statiques dont les quels à chaque point à temps (excepté pendant la commutation transitoire), chaque sortie de porte est relié à  $V_{DD}$  ou à  $V_{SS}$  par l'intermédiaire d'un chemin à faible résistance. En outre, les sorties des portes assument à tout moment la valeur de la fonction booléenne implémentée par le circuit (ignorant, de nouveau, les effets transitoire pendant des périodes de commutation). C'est contrairement à la classe des circuits dynamiques, qui comptent sur la mémoire temporaire des valeurs du signal mémorisé dans la capacité des nœuds à grande impédance du circuit. La dernière approche a l'avantage que la porte résultante est plus simple et plus rapide. Mais leur conception et fonctionnement sont cependant plus impliqués et enclins à l'échec a cause une sensibilité accrue du bruit.

#### II.2.1. L'inverseur CMOS

L'inverseur est vraiment le noyau de toutes les conceptions numériques. Une fois que leur opération et leurs propriétés sont clairement comprises, on peut concevoir des structures plus complexes telles que des portes NAND et, des additionneurs, des multiplicateurs etc. L'analyse des inverseurs peut être prolongée pour expliquer le comportement des portes plus complexes telles que le NAND, et le NOR, ou les XOR, qui forment à leurs tours des modules qui construisent d'autres modules comme des multiplicateurs et des processeurs.

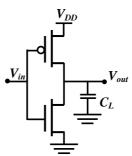

Considérer le circuit représenté sur la figure 2.1, la tension d'entrée  $V_{IN}$  commande les modes de conduction des deux transistors. Quand  $V_{IN}$ =0 le PMOS conduit la tension  $V_{DD}$  à la sortie. Quand  $V_{IN}$ = $V_{DD}$  le NMOS est passant, et transmet la masse GND (0V) a la sortie [3].

Figure 2.1: L'inverseur CMOS

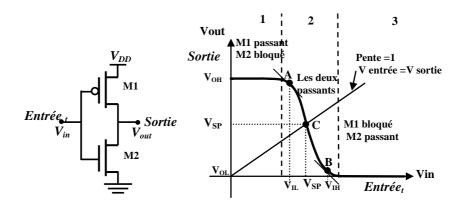

#### II.2.1.1. Les caractéristiques de transfert de l'inverseur en D.C.

Considérer l'inverseur montré dans figure 2.2 et la courbe caractéristique de transfert associée. Dans la région 1 des caractéristiques de transfert, la tension d'entrée est suffisamment basse (typiquement moins que la tension de seuil de M1), de sorte que M1 soit bloquer et M2 est fermé (V<sub>GS</sub>>>V<sub>TH</sub>). À mesure que V<sub>in</sub> est augmenté, M2 et M1 sont passant (région 2). Vin croissant cause plus loin le M2 d'être passant et M1 à entièrement est bloqué, comme montré dans la région 3.

Figure 2.2 : Les caractéristiques de transfert de l'inverseur CMOS

La tension de sortie "élevée" maximum est marquée par  $V_{0H}$ , et la tension de sortie "basse" minimum,  $V_{0L}$ . Les points A et B sur cette courbe sont définis par la pente des courbes de transfert égalant -1. Les tensions d'entrée inférieures ou égalent à la tension  $V_{IL}$ , sont définies par le point A, sont considérés comme un niveau logique bas sur l'entrée de l'inverseur. Des tensions d'entrée supérieures ou égalent à la tension  $V_{IH}$ , définies par le point B, sont considérées comme un niveau logique haut sur l'entrée de l'inverseur. Les tensions d'entrée entre  $V_{IL}$  et  $V_{IH}$ , ne définissent pas une tension de niveau logique valide. Dans le meilleur des cas, la différence entre  $V_{IL}$  et  $V_{IH}$ , est zéro; cependant, ce n'est jamais le cas dans les circuits logiques réels.

#### II.2.1.2. Le point de commutation de l'inverseur

Considérer les caractéristiques de transfert de l'inverseur de base montré dans la figure. 2.2. Le point C correspond au point sur la courbe, où la tension d'entrée est égale à la tension de sortie. En ce moment, la tension d'entrée (ou de sortie) s'appelle la tension de point de commutation d'inverseur,  $V_{sp}$ , et les deux transistors MOSFET dans l'inverseur sont dans la région de saturation. Puisque le courant de drain dans chaque transistor MOSFET doit être égal [3] :

$$\frac{B_n}{2}(V_{SP} - V_{THN})^2 = \frac{B_p}{2}(V_{DD} - V_{SP} - V_{THP})^2$$

(2.1)

La solution pour le V<sub>SP</sub> donne

$$V_{SP} = \frac{\sqrt{\frac{B_n}{B_p}} - V_{THN} + (V_{DD} - V_{THP})}{1 + \sqrt{\frac{B_n}{B_p}}}$$

(2.2)

#### II.2.2. Les portes complémentaires CMOS

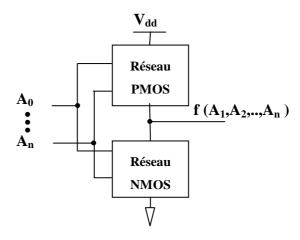

#### II.2.2.1. Le concept

une porte statique CMOS est une combinaison des deux réseaux, Le réseau de dessus est construit à l'aide des transistors NMOS, alors que des transistors PMOS sont utilisés dans le réseau de dessous, La raison primaire de ce choix est que les transistors NMOS produisent "les zéros forts," et les transistors PMOS produisent "les uns forts". La figure 2.3 montre une porte logique générique de N entrées où toutes les entrées sont distribuées aux deux réseaux PMOS et NMOS. La fonction du réseau PMOS est fournir une connexion entre la sortie et le V<sub>DD</sub> n'importe quand la sortie de la porte logique est censée pour être 1 (basé sur les entrées).De même, la fonction du réseau NMOS est relier la sortie au V<sub>SS</sub> quand la sortie de la porte logique est censé pour être 0. Les deux réseau PMOS et NMOS sont construits d'une

mode mutuellement exclusif tels qu'une et seulement un des deux réseaux conduit dans l'état d'équilibre .De cette façon, une fois que les coupures ont arrangé, un chemin existe toujours entre  $V_{DD}$  et la sortie F, réalisant une sortie au niveau haut élevé ("un"), ou, alternativement, entre le  $V_{SS}$  et le F pour une sortie au niveau bas ("zéro").C'est équivalent à énoncé que le nœud de sortie est toujours un nœud de basse impédance dans l'état d'équilibre.

Figure 2.3 : La structure d'une porte complémentaire MOS

Un transistor peut être considéré comme un commutateur commandé par son signal de la grille. Le commutateur NMOS est fermé quand le signal de commande est haut et est ouvert quand le signal de commande est bas. Un transistor PMOS agit en tant que commutateur inversé, qui est fermé quand le signal de commande est bas et ouvert quand le signal de commande est haut.

Un ensemble des règles de construction peut être dérivé pour construire des fonctions logiques (le schéma 2.3). Les dispositifs NMOS reliés en série correspond à la fonction AND . Avec tout les entrées au niveau haut, la combinaison série conduites et la valeur à une extrémité de la chaîne est transféré à l'autre extrémité. De même, les transistors NMOS se sont reliés en parallèle représentent une fonction OR. Un chemin de conduite existe entre la sortie et la borne d'entrée si au moins une des entrées est au niveau haut. Employer les arguments semblables, les règles de construction pour les réseaux PMOS peuvent être formulés. Une connexion des PMOS en série conduite si les deux entrées sont au niveau bas, représentant une fonction NOR  $(\bar{A}.\bar{B}=\overline{A+B})$ , tandis que les transistors PMOS sont montés en parallèle pour implémenter une fonction NAND  $(\bar{A}+\bar{B}=\overline{A.B})$ .

Utilisant les théorèmes de Morgan  $(\overline{(A+B)} = \overline{A}.\overline{B}$  et  $\overline{A.B} = \overline{A}+\overline{B}$ ), on peut montrer que le réseau des PMOS et le réseau des NMOS déroulants d'une structure complémentaire CMOS ; se sont des réseaux duelles .Ceci signifie qu'une connexion parallèle des transistors dans le réseau PMOS correspond à une connexion série des dispositifs NMOS.

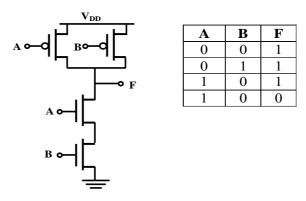

#### II.2.2.2. La porte NAND à deux entrées

Le schéma 2.4 (a) montre une porte NAND à deux entrée ( $F = \overline{A.B}$ ). Le réseau de dessous se compose de deux transistors NMOS en série qui conduisent quand A et B sont hauts. Le réseau duel de dessous, et se compose de deux transistors PMOS en parallèles. Ceci signifie que F est 1 si au moins une des entrées est basse A = 0 ou B = 0, ce qu'est équivalent à  $F = \overline{A.B}$  La table de vérité pour la porte NAND à deux simples entrées est donnée dans le tableau 2.4 (b).on peut vérifier que la sortie F est toujours mise à  $V_{DD}$  ou à GND, mais jamais à touts les deux en même temps [4].

Figure 2.4: La porte NAND

#### II.2.2.3. La porte NOR à deux entrées

L'implémentation CMOS de porte NOR ( $F = \overline{A + B}$ ) est montré sur le schéma 2.5(a). Le réseau de dessus se compose de deux transistors NMOS en parallèles et le réseau duel de dessous, et se compose de deux transistors PMOS en série. La sortie est haut, si et seulement si les entrées A et B sont bas. Par contre la sortie F est bas quand seulement A ou B est haut, ce qu'est équivalent à  $F = \overline{A + B}$ . La table de vérité pour la porte NAND à deux simples entrées est donnée dans le tableau 2.5(b)

Figure 2.5 : La porte NOR

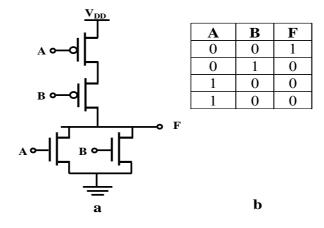

#### II.2.2.4. Le synthèse des portes complexes CMOS

On utilisant la logique complémentaire MOS, considérer la synthèse d'une porte complexe CMOS dont la fonction  $\operatorname{est} F = \overline{D} + A \cdot (B + C)$ . La première étape dans la synthèse de la porte logique est de dériver un réseau de dessous comme représenté sur la figure 2.6. (a) en utilisant les transistors NMOS en série, pour implémenter la fonction AND et les transistors PMOS en parallèle pour implémenter la fonction OR. La prochaine étape est d'utiliser la dualité pour dériver le réseau dessous dans un mode hiérarchique. Le réseau NMOS est coupé en des plus petits sous réseau (sous-ensemble du réseau qui simplifient la dérivation du réseau [4]. Dans la figure 2.6 (b), les sous réseau (SN) pour le réseau dessous sont identifiés au plus haut niveau, SN1 et SN2 sont en parallèle ainsi dans le réseau complémentaire, ils seront en série. puisque SN1 se compose d'un transistor simple, il est tracé directement dans le réseau dessus. D'autre part, on a besoin d'appliquer de façon récursive la règle de dualité à SN2. A l'intérieur de SN2, nous avons SN3 et SN4 en série ainsi dans le réseau de dessous ils apparaîtront en parallèle. En conclusion, à l'intérieur de SN3, les dispositifs sont en parallèle ainsi ils apparaissent en série dans le réseau dessus .La porte complète est montrée dans la figure 2.6 (c).

Figure 2.6: Les portes complexes

#### II.2.3. La porte de transmission TG

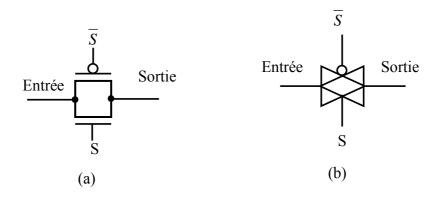

La porte de transmission (TG) est utilisée dans la conception des circuits numériques CMOS pour passer ou ne pas passer un signal. Le schéma et le symbole logique de la porte de transmission (TG) sont montrés dans la figue.2.7. La porte se compose de la connexion en parallèle d'un transistor PMOS et d'un transistor NMOS. En référence à la figure 2.7, quand S

(pour sélectionner) est haut nous observons que la porte de transmission passe le signal d'entrée a la sortie. La résistance entre l'entrée et la sortie peut il a estimé comme Rn//Rp [3].

Figure 2.7 : la porte de transmission

Puisque le transistor NMOS passe le niveau logique bas bien et le transistor PMOS passe le niveau logique haut, mettant deux transistors MOSFET complémentaires en parallèle, comme a été montré dans fig. 2.7 il résulte que la porte TG passe les deux niveaux logiques bien. La porte TG CMOS exige deux signaux de commande, S et  $\overline{S}$ .

#### II.3. Les portes logiques dynamiques

Les portes logiques dynamiques ou synchronisées sont utilisées pour diminuer la complexité, augmenter la vitesse, et pour une dissipation de puissance inférieure. L'idée fondamentale derrière la logique dynamique est d'utiliser l'entrée capacitive du transistor MOSFET pour mémoriser une charge et pour se rappeler ainsi un niveau logique pour un usage ultérieur.

#### II.3.1. Le concept des circuits logiques dynamiques

Dans les circuits logiques statique discutés jusqu'à ce point, la sortie est valide du moment que les entrées soient bien définies. Un circuit logique dynamique, d'autre part, donne un résultat a la sortie qui est seulement valable pour une période courte. Si le résultat n'est pas employé immédiatement, la tension peut changer à temps et donner une valeur de sortie incorrecte. Un circuit logique dynamique emploie des nœuds capacitifs pour mémoriser la charge électrique.

#### II.3.2. Le principe fondamental de la logique dynamique

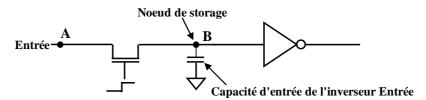

Considérant le transistor de passage NMOS montré dans fig. 2.7, conduisant un inverseur, si nous synchronisons la grille du transistor de passage par un niveau logique haut,

le niveau logique sur l'entrée, point A, sera passé à l'entrée de l'inverseur, point B. si ce niveau logique est un 0. L'entrée de l'inverseur sera forcée à la masse tandis que, un 1 logique forcera l'entrée de l'inverseur à  $V_{DD}$ - $V_{THN}$ . Quand le signal d'horloge passe à 0, le transistor de passage est bloqué et l'entrée de l'inverseur se rappelle le niveau logique. En d'autres termes, quand le transistor est passant, la capacité d'entrée de l'inverseur est chargée à  $V_{DD}$  -  $V_{THN}$  ou à la masse, à travers le transistor de passage. Aussi longtemps que cette charge est présente, la valeur logique est mémorisé, ce qui nous intéresse a ce point est le mécanisme de fuite qui peut fuir la charge stockée du nœud. Un nœud, tel que celui marqué B dans figure 2.8, s'appelle un nœud dynamique ou un nœud de stockage. Noter que ce nœud est un nœud à grande impédance et est facilement susceptible du bruit [3]

Figure 2.8 : Exemple d'un circuit dynamique et d'une capacité associée de stockage

#### II.3.3. Les familles des circuits logiques dynamiques :

Dans la porte logique dynamique la sortie est seulement valide pour une quantité de temps courte après que le résultat soit produit. Bien que ceci semble tout à fait restrictif, les réseaux dynamiques CMOS sont utiles pour la conception de système à grande vitesse .nous analyserons plusieurs familles logiques dynamiques CMOS.

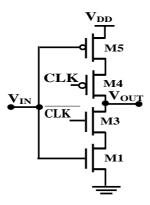

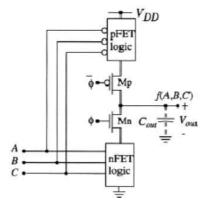

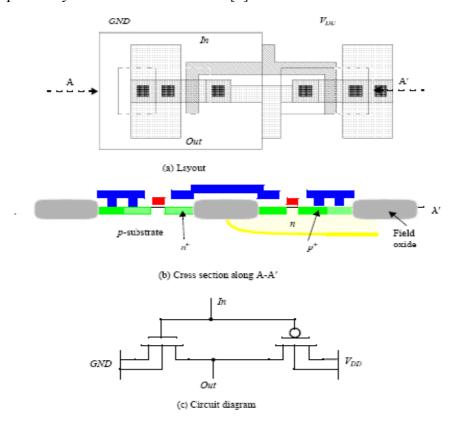

#### II.3.3.1. La logique C2MOS

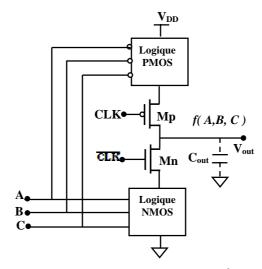

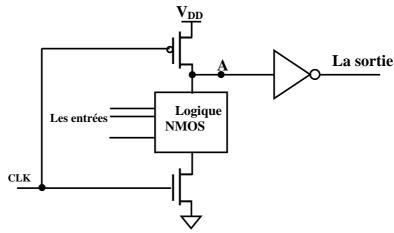

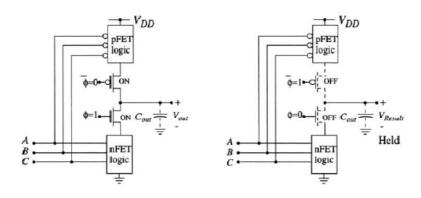

La logique Clocked CMOS (C<sup>2</sup>MOS), est une famille logique qui combine la conception logique statique avec la synchronisation réalisée en employant des signaux d'horloge. Le schéma 2.8 montre la structure générale d'une porte logique C<sup>2</sup>MOS. Les d'entrée A, B, et C sont connectées aux paires complémentaires de NMOS/PMOS comme dans la conception statique ordinaire où elles agissent comme les commutateurs ouverts ou fermés. La seule modification est la mise en place de deux FETS synchronisés entre les réseaux logique et la sortie. Le PMOS est contrôlé par signal  $\overline{\text{CLK}}$  et sépare le bloc logique PMOS et le C<sub>out</sub>, alors que Mn est contrôlée par le CLK et il remplit la même fonction pour le bloc logique NMOS.

Figure 2.9 : La porte logique C<sup>2</sup>MOS

La logique C<sup>2</sup>MOS est employé pour réduire la dissipation de puissance et la taille de layout et pour augmenter la vitesse. La porte statique standard CMOS exige 2N transistors MOSFET pour une porte de n entrées. En général, une porte de n entrée C<sup>2</sup>MOS exige N+2 transistors MOSFET où deux transistors MOSFET sont utilisés dans le système de synchronisation. Des transistors MOSFET additionnels peuvent être utilisés pour le buffering ou pour aider la porte à apparaître dans son fonctionnement plus statique [3].

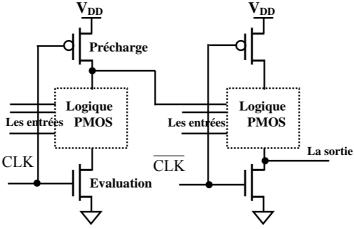

#### II.3.3.2. La logique PE

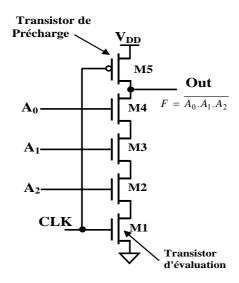

Cette section discute la logique PE où precharge evaluate logic. Considérer la porte NAND à trois entrées montrées dans la figue 2.9.Le fonctionnement de cette porte se fonde sur une entrée d'horloge simple. Quand CLK est bas, la capacité de nœud de sortie est chargée à V<sub>DD</sub> par M5. Pendant la phase CLK d'évaluation, est haute, M1 est passant, et si A0, A 1, et A2 sont hauts, la sortie est tirée au niveau bas. La sortie logique est disponible seulement quand CLK est haut. La sortie est une logique 1 quand CLK est bas. Un inconvénient de la logique PE est que la sortie logique de la porte est une partie disponible du temps et pas de tout le temps comme dans les portes statiques.

Plusieurs caractéristiques importantes de la porte PE devraient être précisées. La capacité d'entrée de la porte PE est inférieure à cela de la porte statique. Chaque entrée est reliée à un seul transistor MOSFET où les entrées de porte statiques sont attachées à deux transistors MOSFET. Potentiellement la porte PE est alors plus rapide et dissipe moins de puissance [3].

Figure 2.10 : La porte PE NAND a trois entrées

# II.3.3.3. La logique Domino

La porte PE avec l'addition d'un inverseur s'appelle la logique domino (fig.2.11). Le nom domino vient du fait, qu'une porte logique dans une série des portes logiques dominos ne peut pas changer ses états de sortie jusqu'à ce que la porte précédente change ses états. Le changement de la sortie des portes se produit semblable à une série des pièces de domino en chute. L'inverseur utilisé dans la porte domino à l'avantage supplémentaire qu'il peut être dimensionné pour conduire de grandes charges capacitives [5].

Figure 2.11 : La porte de logique domino

# II.3.3.4. La logique NP

L'idée derrière l'implémentation d'une fonction logique utilisant la logique NP est montrée dans la figure 2.12.on arrange des étages de NMOS et de PMOS élimine le besoin de retard associé à l'inverseur utilisé dans la logique domino, rendant le fonctionnement possible à une vitesse plus élevée [5].

Figure 2.12: La logique PN

# II.4. Les circuits logiques séquentiels

Les circuits logiques combinatoires, décrits plus tôt, ont la propriété que la sortie d'un bloc logique est une fonction seulement des valeurs courantes de l'entrée. Pourtant pratiquement tous les systèmes utiles exigent le stockage d'information d'état, mener à une autre classe des circuits appelés les circuits logiques séquentiels. Dans ces circuits, la sortie dépend non seulement des valeurs courantes des entrées, mais également aux valeurs précédentes de l'entrée. En d'autres termes, un circuit séquentiel se mémorise rappelle une partie de l'histoire passée du système qu'il a dans sa mémoire.

#### II.4.1. Les bascules

Les latches et les bascules sont les éléments de base pour mémoriser l'information. Ils sont les modules fondamentaux pour tous les circuits séquentiels. Un verrou ou une bascule peut mémoriser un bit de donnée. La différence principale entre les latches et les bascules c'est que pour les latches, leurs sorties sont constamment affectées par leur entrée aussi longtemps que le signal de d'activation est affirmé. En d'autres termes, quand elles sont actives, leur contenu change immédiatement quand leur entrée change. D'autre part les bascules, avoir leur contenu change seulement au front montant ou descendant du signal d'activation. Après le front montant ou le front descendant du signal d'activation et pendant le moment où le signal est à un 1 ou à un 0 constant, le contenu de la bascule reste constant même si l'entrée change. Ce signal d'activation est habituellement le signal d'horloge.

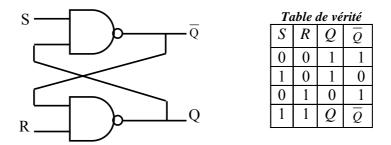

#### II.4.1.1. La bascule RS

La bascule set reset (SR) montrée dans figure 2.13, est composée de deux portes NAND. Le symbole logique et la table de vérité sont également montrés dans cette figure.

Considérant le cas ou S est haut et R est bas. Forçant R au niveau bas cause Q de passer au niveau haut .Puisque S est haut et Q est haut, la sortie  $\overline{\mathbf{Q}}$  est bas. Considérer maintenant le cas ou S et R sont bas. Dans ces circonstances, les sorties de bascule sont les deux au niveau haut. Cette bascule peut facilement être conçu et présenté avec les techniques des portes statiques logiques [3].

Figure 2.13 : La bascule set reset conçue à l'aide des portes NAND.

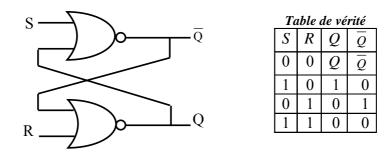

Une implémentation alternative de la bascule SR est montrée dans la figure 2.13 utilisant des portes NOR. Considérons le cas ou S est haut et R est bas. Pour la porte NOR, une entrée au niveau haut force la sortie de la porte au niveau bas. Par conséquent, la sortie  $\overline{Q}$  est au niveau bas toutes les fois que l'entrée S au niveau haut. De même, toutes les fois que l'entrée R à niveau haut, la sortie Q doit être au niveau bas. Le cas ou les deux entrées étant au niveau haut cause Q et  $\overline{Q}$  à passer à 0, ou en d'autres termes les sorties de la bascule ne sont plus des compléments. La figure 2.14 montre le symbole logique de la bascule de SR.

Figure 2.14 : La bascule set reset conçue à l'aide des portes NOR

#### II.4.1.2. Les bascules synchronisées

Des bascules synchronisées peuvent être divisées en trois catégories. La première catégorie se compose de ceux dans lesquels la largeur d'impulsion du signal d'horloge doit être courte comparée à la propagation du retard à travers la bascule. En d'autres termes, l'entrée d'horloge devrait être au niveau haut, et puis passer au niveau bas avant que la sortie de la bascule change l'état. La deuxième catégorie de bascule synchronisée se compose de ceux dans lesquels la sortie change, tandis que le signal d'horloge est au niveau haut. Ce type

de bascule s'appelle parfois une bascule à niveau sensible; La catégorie finale des bascules est le type déclenché par front d'impulsion. La sortie de la bascule change l'état sur le front montant ou descendant d'horloge.

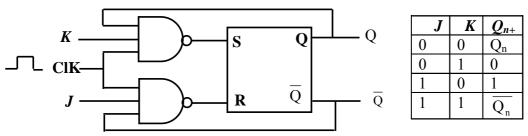

# 1. La bascule JK (Impulsion d'horloge de largeur courte)

La bascule JK synchronisé est montrée dans figure. 2.15. La bascule JK est construite à l'aide de la bascule SR NAND et de deux portes NAND. Cependant, la différence de la bascule SR, J et K peuvent être au niveau haut en même temps sans les sorties devenant égales. Le fonctionnement de la bascule JK dépend de l'état précédent de la bascule. Avec le signal d'horloge a tenu le niveau bas, les entrées et les sorties de la bascule SR ne changent pas. Tenir le signal d'horloge à niveau haut fait osciller la sortie de la bascule entre une logique 0 et 1.Avec l'application d'une impulsion d'horloge courte et J =K=0, les sorties du bascule ne changent pas. Si K=1 et J=0, la sortie, Q est à 0 après l'application de l'impulsion d'horloge, tandis que si, J=1 et K=0, la sortie est au niveau haut. Si J et K sont au niveau haut, la sortie devient le complément de l'état précédent.

Figure 2.15 : L a bascule JK synchronisé

Une bascule T peut être construit en utilisant la bascule JK par le réglage J=K=1, ou simplement en remplaçant les portes NAND à trois entrées de la figure 2.15 avec des portes de NAND a deux d'entrée. L'entrée d'horloge du bascule JK est employée comme entrée T de la bascule T .l'application d'une impulsion courte à l'entrée T de la bascule T cause le basculement des états de la sortie Q .Si la sortie est a niveau haut et l'entrée de T passe à 1, la sortie change au niveau bas. Le basculement de l'entrée T au niveau haut provoque encore la sortie de changer de nouveau à un niveau haut. La bascule T peut il a employé pour diviser un signal d'horloge en demi, (en utilisant la bascule de fig.2.15).

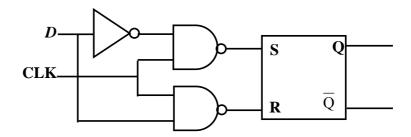

# 2. La bascule D (sensibles de niveau)

Les bascules qui sont synchronisées avec un signal qui permet à la sortie de changer avec l'entrée, n'ont aucune condition spécifique de largeur d'impulsion pour l'horloge. Pour illustrer une bascule de niveau sensible considérer la bascule donnée ou D montré dans

fig.2.16 avec le symbole logique associé. Quand le signal d'horloge est haut, l'entrée de D peut passer directement à la bascule SR, si D est un 1 tandis que CLK est au niveau haut, la sortie, Q est un 1, alors que si D est au niveau bas la sortie est au niveau bas. Si D change à tout moment tandis que l'entrée de CLK est haute, la sortie suivra. Quand le signal CLK passe à 0, le niveau logique courant de D est verrouillé dans la bascule SR note que cette bascule n'est pas une bascule front sensible, parce que la sortie change indépendamment du temps de front de transition.

Figure 2.16 : Bascule D Sensible de niveau

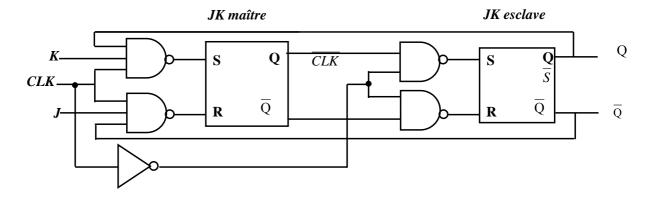

#### 3. La bascule JK maître esclave (déclenché par front d'impulsion)

La bascule JK maître- esclave, montré dans la figure 2.17 est un exemple d'une bascule déclenché par front d'impulsion. Quand le signal de CLK passe à 1, la bascule JK maître est activé .Puisque la bascule esclave ne peut pas changer des états quand CLK est haut, la largeur d'impulsion d'horloge ne doit pas être moins que le retard de propagation de la bascule. Quand CLK passe à 0, les données principales sont transférées à l'esclave. Si J et K sont au niveau bas, la sortie du maître demeure sans changement, et donc ainsi fait la sortie de l'esclave. Si J = 1 et K = 0, quand l'impulsion CLK passe à 0, la sortie principale, Q passe à 1. Quand CLK passe à 0, la sortie à niveau haut du maître est transférée à l'esclave. La bascule JK maître esclave se comporte juste comme la bascule JK de la section précédente excepté le fait que les données ne sont pas disponibles jusqu'à ce que CLK passe à 0, et il n'y a aucune restriction à la largeur d'impulsion de l'horloge (c.-à-d., la bascule est déclenché par front descendant), l'addition des possibilités reset ou set à la bascule peuvent être accomplies en ajoutant des portes logique entre NAND et la bascule SR.

Figure 2.17: La bascule JK maître esclave déclenchées par front

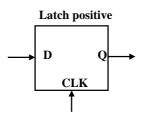

# II.4.2. Les latches et les registres

Un latche est un composant essentiel dans la construction d'un registre déclenché par front d'impulsion. C'est un circuit à niveau sensible qui passe l'entrée D à la sortie Q quand le signal d'horloge est haut. Ce latche serait en mode transparent. Quand l'horloge est au niveau bas, les données d'entrée prélevées sur le front descendant de l'horloge est maintenir stable a la sortie pour la phase entière, et le verrou est en mode de prise. Les entrées doivent être stables pendant une période courte autour du front descendant de l'horloge pour rencontrer les conditions setup et hold. Un latche fonctionnant dans les conditions ci-dessus est un verrou positif. De même, un verrou négatif passe l'entrée D a la sortie Q quand le signal d'horloge est bas [4].

Figure 2.18: Symbole du latche D

Contrairement aux latches a niveau sensibles, les registres déclenchés par front d'impulsion prélèvent seulement l'entrée pendant une transition d'horloge de 0 à 1 pour un registre déclenché par front d'impulsion positif, et de 1 à 0 pour un négatif registre déclenché par front d'impulsion .Ils sont typiquement construits en utilisant les primitifs de latche du schéma 2.18. Une configuration se reproduisant le plus souvent est la structure maître-esclave qui cascade un latche positif et un latche négatif.

#### II.4.2.1 Les registres dynamiques

Ceci a comme conséquence; une classe des circuits basés sur la mémoire temporaire de la charge des condensateurs parasites. Le principe est exactement identique à celui utilisé dans la logique dynamique la charge stockée sur un condensateur peut être employée pour représenter un signal logique. L'absence de la charge dénote un 0, alors que sa présence représente un 1 stocké. Aucun condensateur n'est idéal, malheureusement, et une certaine fuite de charge est toujours présente. Une valeur stockée peut par conséquent seulement être gardée pour une quantité de temps limitée, typiquement dans la gamme des millisecondes. Si on veut préserver l'intégrité de signal, une régénération périodique de sa valeur est nécessaire. Par conséquent nommé le stockage dynamique .La lecture de la valeur du signal stocké d'un condensateur sans perturber la charge exige la disponibilité d'un dispositif avec une impédance d'entrée élevée.

## 1. Le registre dynamique de porte de transmission

Un registre déclenché par front d'impulsion positif entièrement dynamique basé sur le concept maître esclave est montré sur le figure 2.19.Quand CLK = 0, la donnée d'entrée est prélevé sur le nœud 1 de stockage, qui a une capacité équivalente de C1 comprenant la capacité de la grille de I1, la capacité de jonction du T1, et la capacité de chevauchement de la grille du T1.Pendant cette période, l'étage esclave est en mode de prise, avec le nœud 2 dans un état (flottant) à grande impédance. Sur le front montant de l'horloge, le T2 de la porte de transmission s'active, et la valeur prélevée sur la droite du nœud 1 avant que le front montant propage à la sortie Q (à noter que le nœud 1 est stable pendant la phase élevée de l'horloge puisque la première porte de transmission est bloquée). Le nœud 2 stocke maintenant la version inversée du nœud 1. Cette implémentation d'un registre déclenché par front d'impulsion est très efficace car elle exige seulement 8 transistors. Les commutateurs de prélèvement peuvent être implémentés en utilisant seulement des transistors du passage NMOS, ayant pour résultat une implémentation quant même simple de 6 transistors. Le compte réduit de transistor est attrayant pour les systèmes à une performance élevée et de basse puissance [4].

Figure 2.19: Registre dynamique de TG

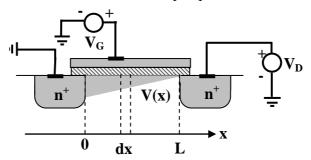

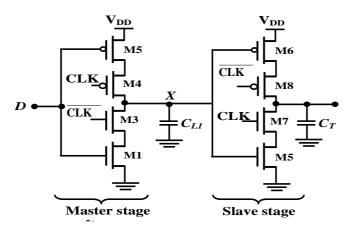

# 2. Le registre dynamique C<sup>2</sup>MOS

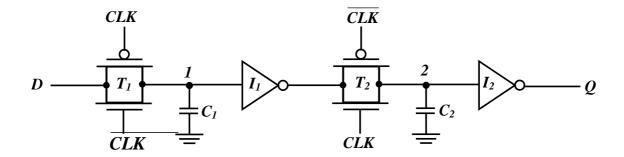

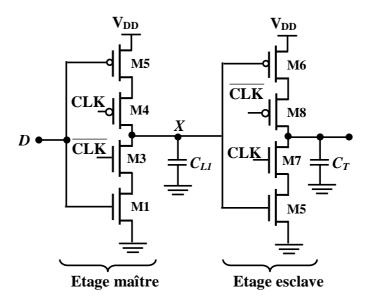

Le schéma montre un registre dynamique ingénieux, basé sur le concept maître esclave peu sensible au chevauchement d'horloge. Ce circuit s'appelle le registre C<sup>2</sup>MOS (CMOS synchronisé) [4], et fonctionne en deux étapes [4].

1-Quand CLK=0 ( $\overline{CLK}=1$ ): Le premier pilote à trois états est fonctionne, et l'étage principal s'active comme un inverseur prélevant la version inversée de D sur le nœud interne X. l'étage est en mode d'évaluation. En attendant, la section esclave est dans un mode haut impédance, ou dans un mode de maintien. Les deux transistors M7 et M8 sont bloqués, découplant la sortie de l'entrée. La sortie Q maintient sa valeur précédente mémorisée sur le condensateur de sortie CL2.

2-Les rôles sont inversés quand CLK=1: la section de l'étage principale est en mode de maintien (M3-M4 bloqués), alors que la deuxième section évalue (M7-M8 passants). La valeur stockée sur CL1 propage au nœud de sortie par l'étage esclave, qui agit en tant qu'un inverseur.

Le circuit global fonctionne comme registre maître esclave déclenché par front d'impulsion positif très semblable au registre à base de porte de transmission présentée plus tôt. Cependant, il y a une différence importante :

Un registre  $C^2MOS$  avec CLK,  $\overline{CLK}$  synchronisés est peu sensible au chevauchement, aussi longtemps que les temps de front montant et front descendant d'horloge sont suffisamment petits.

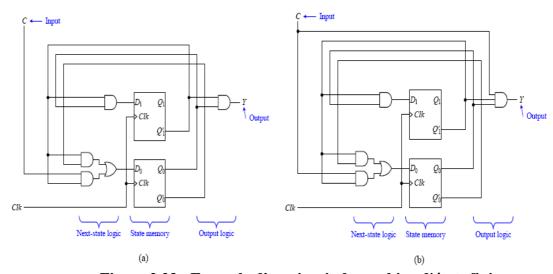

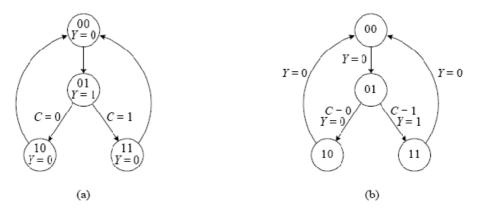

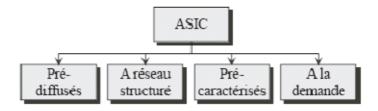

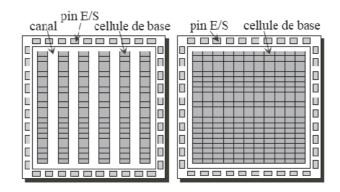

Figure 2.20: Registre dynamique C<sup>2</sup>MOS