République Algérienne Démocratique et Populaire Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

## **THÈSE**

## Présentée pour l'obtention du diplôme de DOCTORAT en SCIENCES en Électronique

#### **OPTION**

Microélectronique

Par

## **Fateh MOULAHCENE**

## Thème

# Contribution à la Conception Des circuits CMOS pour application médicale

| Soutenue le 14/01/2016     | devant le jury composé de : |                           |             |

|----------------------------|-----------------------------|---------------------------|-------------|

| Dr. Farida HOBAR           | Prof.                       | Université de Constantine | Président   |

| Dr. Nour-eddine BOUGUECHAL | Prof.                       | Université de Batna.      | Rapporteur  |

| Dr. Saida LATRECHE         | Prof.                       | Université de Constantine | Examinateur |

| Dr. Abdelhamid BENHAYA     | Prof.                       | Université de Batna       | Examinateur |

| Dr. Abdelhamid OUNISSI     | Prof.                       | Université de Batna       | Examinateur |

| Dr. Saida REBAI            | Prof.                       | Université de Constantine | Examinateur |

## بِسْمِ اللَّهِ الرَّحْمَٰنِ الرَّحِيمِ

## Dédicace

Je dédie ce modeste travail fruit de plusieurs années de patience :

A ma chère mère symbole de tendresse, et à mon cher père symbole

de sacrifice

A ma femme A mes frères et à ma sœur Ahelam A tous mes Amis

A mes enseignants, lumières de mon chemin

#### 800g

## Remerciements

Bien que cette thèse porte mon nom, elle est véritablement le fruit de la coopération de plusieurs personnes, qui m'ont encadré, supporté, guidé tout au long de ces années. Ce sont ces personnes que je tiens ici à remercier.

Je souhaite remercier avant tout mon directeur de thèse Mr. Nour-Eddine BOUGUECHAL professeur à l'université de Batna et responsable du laboratoire de l'électronique avancée (LEA). Je retiens du professeur BOUGUECHAL ses grandes qualités d'encadrement, n'a eu de cesse de m'encourager et de me soutenir durant ces dernières années. J'en profite pour lui exprimer ici ma plus profonde gratitude.

Mes vifs remerciements à **Mme. Farida HOBAR**, professeur à l'université de Constantine, pour avoir accepté de présider le jury et à bien voulu prendre le temps de s'intéresser au sujet de la présente thèse.

Je tiens à remercier vivement Mme. Saida LATRECHE, professeur à l'université de Constantine, Mr. Abdelhamid BENHAYA professeur à l'université de Batna, Mr. Abdelhamid OUNISSI, professeur à l'université de Batna et Mme. Saida REBAI, Maitre de conférence à l'université de Constantine d'avoir fait partie du jury en qualité d'examinateurs et pour m'avoir honoré par leurs présences au jury.

Je remercie également mes amis, Yousef, Samir, Soufiane, Salah, Imad, mekki, et tous mes amis; pour tout ce qu'ils m'ont permis d'apprendre et bien plus encore. Je remercie également mes amis proches pour avoir toujours été là. Je remercie aussi les gens que j'ai pu côtoyer durant mes années de thèse qui ont contribué de près ou de loin le long de mes études et recherches scientifiques.

Enfin, je souhaite remercier chaleureusement ma famille; à mes parents, et mes amis qui ont été un soutien constant tout au long de mes études et méritent donc tous de se voir dédicacer ce manuscrit.

Mon dernier remerciement va directement à la personne qui a partagé au plus près cette aventure avec moi, celui qui a été ma motivation permanente, celui qui a œuvré dans l'ombre, ma femme **nadia** merci pour son amour, sa patience, sa compréhension et son soutien sans égal au cours de ces années.

Cette thèse n'aurait eu aucun sens sans la présence de mon ange, mon fils Anes abdelhak, qui colorie ma vie.

## Sommaire

| Introduction Générale                                             | 11. |

|-------------------------------------------------------------------|-----|

| Chapitre 1 : Circuits et Signaux Médicaux                         |     |

| I.1. Introduction                                                 | 19. |

| I.2. Signaux médicaux                                             | 19. |

| I.3. Circuits médical                                             | 21  |

| <b>I.3.1.</b> Implant Cochléaire et prothèse auditive             | 21. |

| I.3.2. Implant urinaire.                                          | 23  |

| <b>I.3.3</b> . Implant Intra-corticale prothèse visuelle          | 24. |

| I.3.4. Implant du Cerveau                                         | 25  |

| I.3.5. Implant Pacemaker.                                         | 27. |

| <b>I.4.</b> Conclusion.                                           | 28. |

| Chapitre 2 :Le signal ECG et les Interférences                    |     |

| II.1 Introduction.                                                | 30. |

| II.2 Système cardio-vasculaire.                                   | 31. |

| <b>II.2.1</b> Cœur                                                | 31. |

| II.2.2 Circulation sanguine.                                      | 32  |

| II.3 L'électrophysiologie cardiaque.                              | 32  |

| II.3.1. Propriétés électro-physiologiques des cellules cardiaques | 32  |

| II.3.2. Fonctionnement électrique du cœur.                        | 34. |

| II.4. L'électrocardiographie.                                     | 34. |

| II.4.1. Système de Dérivations électrocardiographiques            | 35. |

| II.4.1.1 Dérivations périphériques.                               | 36. |

| II.4.1.1. Dérivations périphériques bipolaires                    | 36. |

| II.4.1.1.2. Dérivations périphériques unipolaires                 | 36. |

| II.4.1.2. Dérivations précordiales.                               | 37. |

| II.4.1.2.1. Position des électrodes précordiales                  | 37. |

| II.4.2. Signal électrocardiogramme.                               | 38  |

| II.4.2.1. Ondes enregistrées sur un ECG normal                    | 39  |

| II.4.2.2. Segments et intervalles qui caractérisent un ECG normal | 40. |

| <b>II.4.</b> 3 Le rythme cardiaque.                               | 41  |

| II.5 Interférence                                                                      | 42.  |

|----------------------------------------------------------------------------------------|------|

| II.5.1. Interférences dues à l'alimentation (60 ou 50 Hz)                              | 42.  |

| II.5.2. Interférences dues à l'activité électrique musculaire                          | 42.  |

| II.5.3. Dérive de la ligne de base.                                                    | .42. |

| II.5.4 Interférences dues au mauvais contact électrode-peau                            | 43.  |

| II.5.5 Interférences d'instrumentation                                                 | .43. |

| II.6 Conclusion.                                                                       | .44. |

| Chapitre 3 : Cellules analogiques                                                      |      |

| III.1 Introduction                                                                     | 46.  |

| III.2 Techniques de conception basse tension en technologie CMOS                       | 46.  |

| III.2.1 Transistor composite                                                           | 47.  |

| III.2.2LatéralBJT                                                                      | 48.  |

| III.2.3 Polarisation direct Bulk-Source.                                               | 49.  |

| III.2.4 Bulk-DrivenMOSFET                                                              | 50.  |

| III.3 Limitationsdecircuits eninversion forte travaillé avec alimentationbasse tension | 52.  |

| III.4 Technologie CMOS 90nm GPDK.                                                      | 53.  |

| III.5 Régimes de transistor MOSFET.                                                    | .53. |

| III.5.1 Courant de drain en régime ohmique                                             | 53.  |

| III.5.2.Courant de drain en régime de saturation                                       | 53.  |

| III.6 Bruit électrique Basse Fréquence dans le transistor MOSFET                       | 54.  |

| III.6.1 Bruit thermique                                                                | 54.  |

| III.6.2.Bruit en 1/f                                                                   | 55.  |

| III.7 Circuit portative pour le signal ECG.                                            | 55.  |

| III.7.1 Amplificateur opérationnel d'instrumentation                                   | 56.  |

| III.7.1.1 Trois amplificateur opérationnel                                             | 56.  |

| III.7.1.2 Chopper stabilisé Amplificateur opérationnel                                 | 59.  |

| III.7.1.3 Réaction de courant (current feedback) Amplificateur opérationnel            | .60. |

| III.7.1.4 Capacité commuté Amplificateur opérationnel                                  | 62.  |

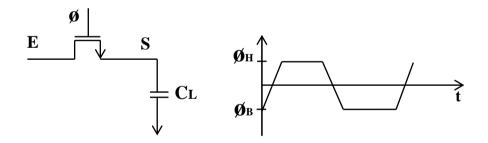

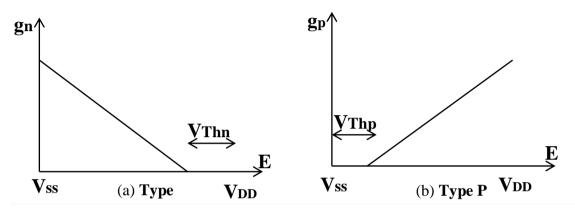

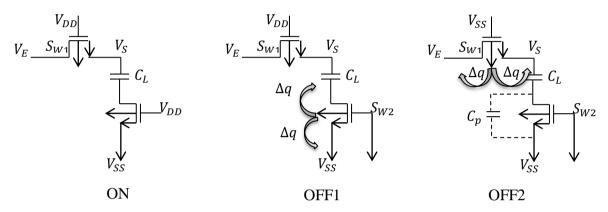

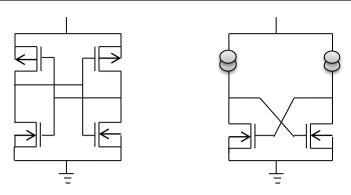

| III.7.2. Commutateurs analogique                                                       | 63.  |

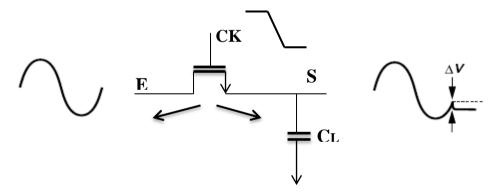

| III.7.2.1 Phénomène d'injection de charges et de clockfeedthrough                      | 65.  |

| III.7.2.2. Techniques d'amélioration des performances du commutateur analogique.       | 67.  |

| III.7.2.2.1. Porte de Transmission                                                     | .67. |

| III.7.2.2.2 Technique du Bootstrapping.                                                | 68.  |

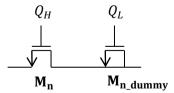

| III.7.2.2.3. Technique d'utilisation du transistor fantôme (dummy structure)  | 69. |

|-------------------------------------------------------------------------------|-----|

| III.7.2.2.4 Technique du « bottom plate sampling » (BPS)                      | 70. |

| III.8. Conclusion.                                                            | 70. |

| Chapitre 4 : Convertisseur analogique Numérique (CAN)                         |     |

| IV.1 Introduction                                                             | 72. |

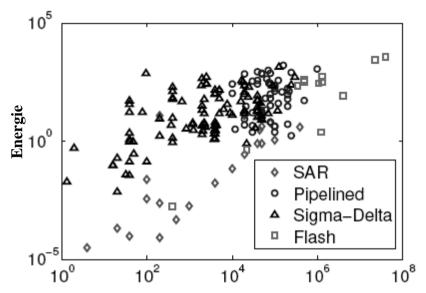

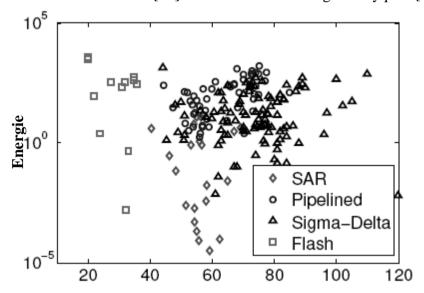

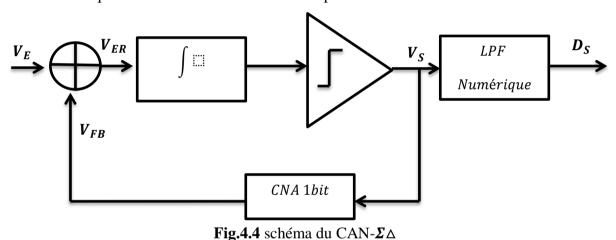

| IV.2.Review desArchitectures de CANefficace en énergie                        | 72. |

| IV.3.CANfondamentauxet métriques de performance                               | 75  |

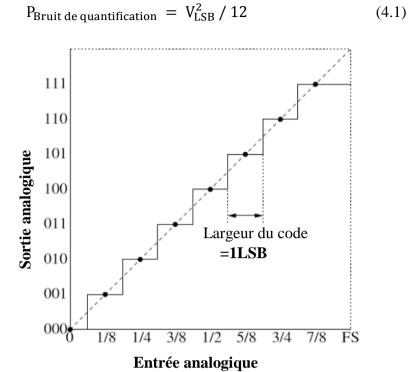

| IV.3.1 Résolution.                                                            | 75. |

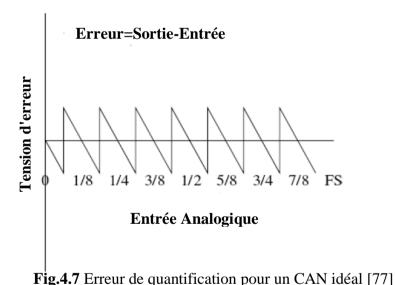

| IV.3.2.Erreur de quantification                                               | 75  |

| IV.3.3. Critères pour l'évaluation des performances d'un convertisseur        | 76. |

| IV.3.3.1 Paramètres dynamiques                                                | 77. |

| IV.3.3.1.1 Rapport Signal-sur-Bruit (SNR)                                     | 77  |

| IV.3.3.1.2. Rapport Signal-sur-Bruit avec Distorsion (SNDR)                   | 78. |

| IV.3.3.1.3 Gamme dynamique utilisable (SFDR)                                  | 78. |

| IV.3.3.1.4 Nombre effectif de bits (ENOB)                                     | 78. |

| IV.3.3.1.5Distorsion harmonique totale (THD)                                  | 78. |

| IV.3.3.2 Paramètres statiques                                                 | 79. |

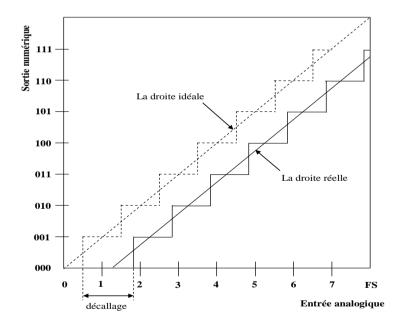

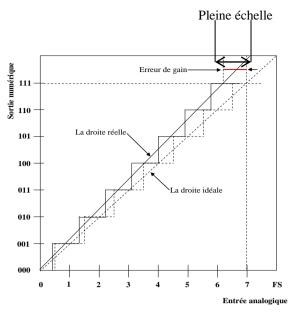

| IV.3.3.2.1 Erreur de décalage (Offset) et Erreur à pleine échelle             | 79. |

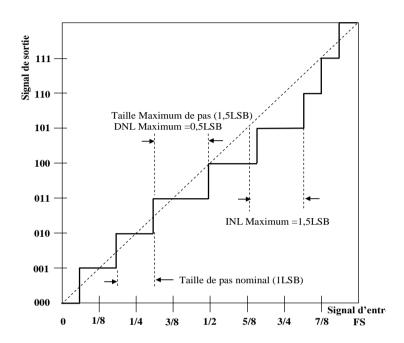

| IV.3.3.2.2 Erreur de linéarité différentielle (DNL)                           | 80. |

| IV.3.3.2.3 Erreur de linéarité intégrale (INL)                                | 81  |

| IV.3.3.2.4 Monotonie                                                          | 81. |

| IV.3.3.2.5 Codes manquants.                                                   | 81  |

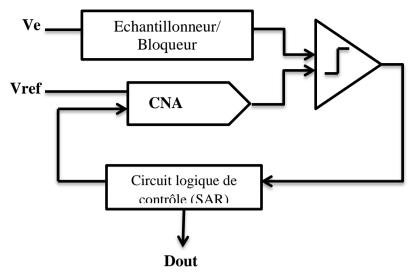

| IV.4 Convertisseur analogique numérique à approximations successives SAR      | 82  |

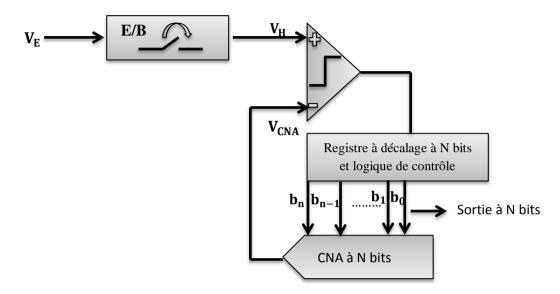

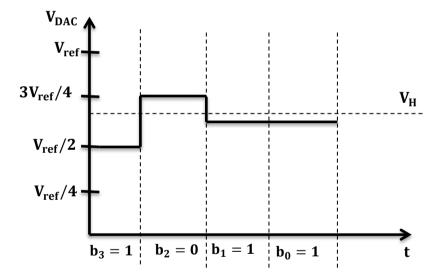

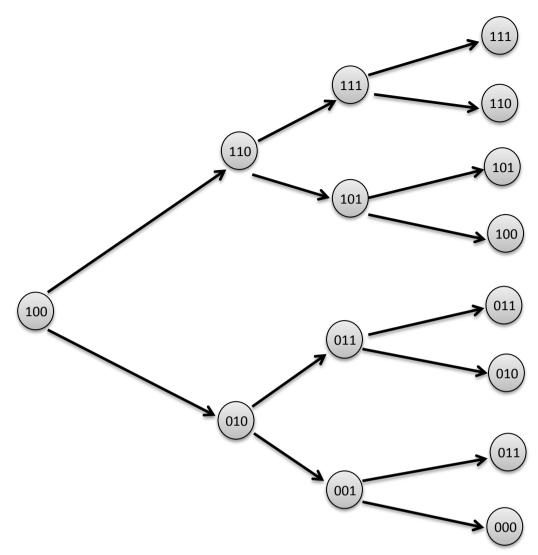

| IV.4.1.Principe de fonctionnement de convertisseur à approximation successive | 82. |

| IV.4.1.1. Convertisseur Numérique Analogique à réseaux capacitifs             | 84. |

| IV.4.1.1.1CNA à capacité pondérées.                                           | 86. |

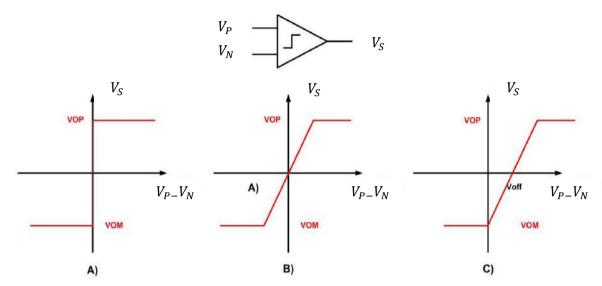

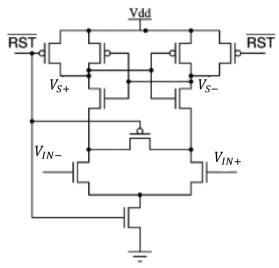

| IV.4.1.2 .Comparateur.                                                        | 87. |

| IV.4.1.2.1. Performance Métriquesdes Comparateurs                             | 88. |

| IV.4.1.2.1.1. Résolution.                                                     | 88. |

| IV.4.1.2.1.2.Gain.                                                            | 89. |

| IV.4.1.2.1.3Délai de propagation.                                             | 89. |

| IV.4.1.2.1.4 Tension d'Offset.                                                | 89. |

| IV.4.1.2.2. Architectures du Comparateur.                                     | 90. |

|                                                                               |     |

| IV.4.1.2.2.1.Comparateur en boucle ouvert                                  | 90.  |

|----------------------------------------------------------------------------|------|

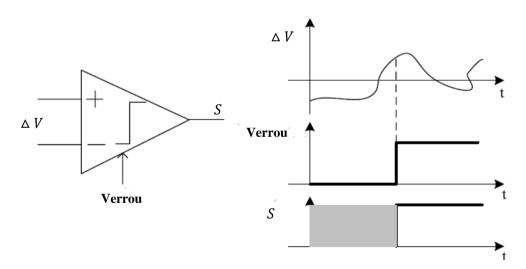

| IV.4.1.2.2.Comparateur à verrou                                            | 90.  |

| IV.4.1.2.2.2.1.Comparateur à verrou statique                               | 91.  |

| IV.4.1.2.2.2.Comparateur à verrou dynamique                                | 92.  |

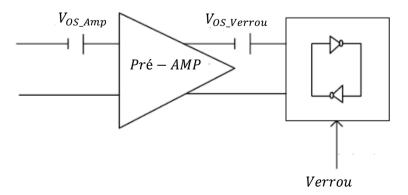

| IV.4.1.2.2.3.Combinant préamplifi cateur et verrou                         | 93.  |

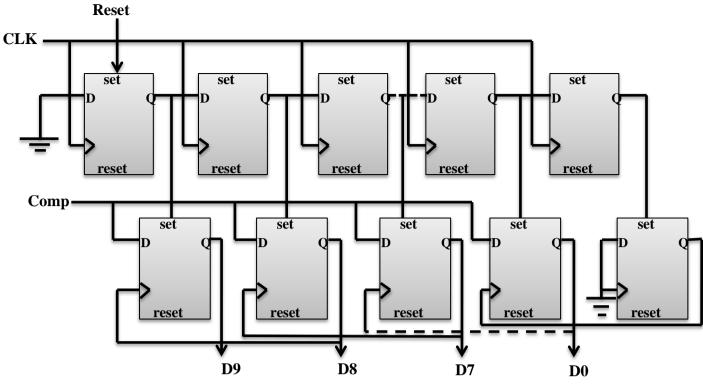

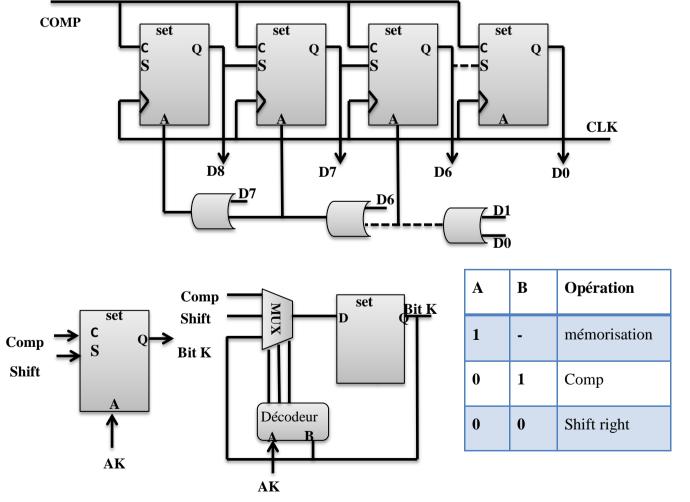

| IV.4.1.3. Registre à approximation successive (RAS)                        | 94.  |

| IV.5 Conclusion.                                                           | 96.  |

| Chapitre 5 : Simulation et Résultats                                       |      |

| V.1 Introduction                                                           | 98.  |

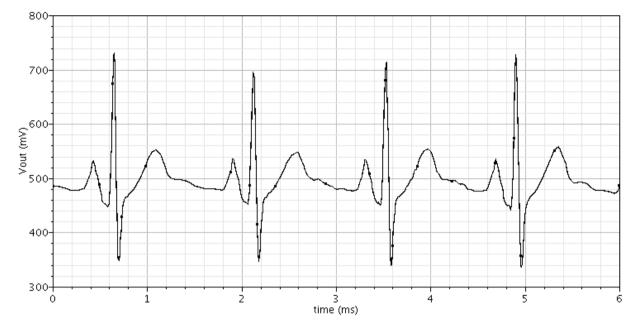

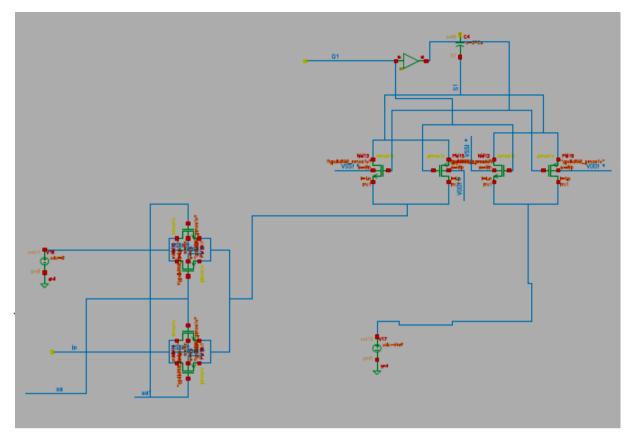

| V.2 Système d'acquisition de données pour signal ECG                       | 98.  |

| V.2.1 Signal ECG.                                                          | 99.  |

| V.2.2 Amplificateur opérationnel choper stabilisé pour Signal ECG          | 100. |

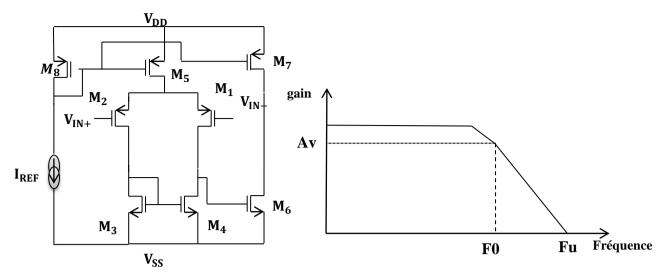

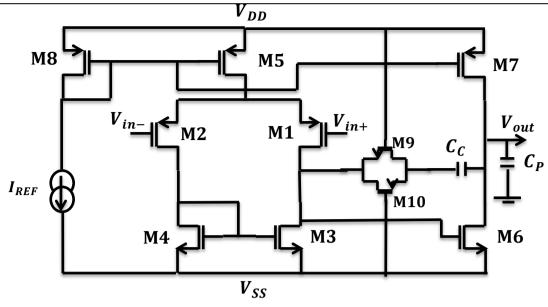

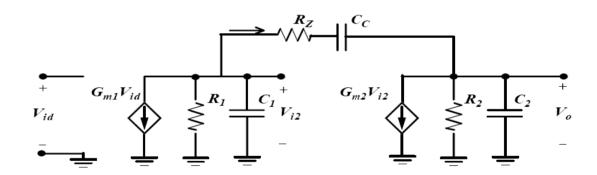

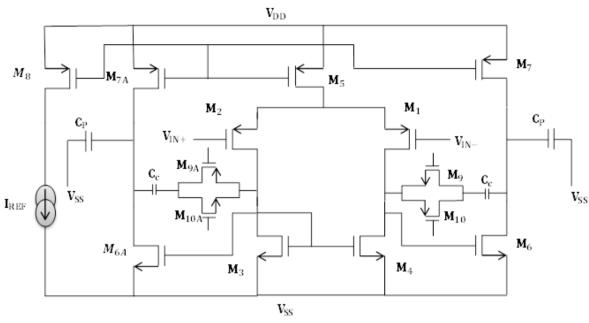

| V .2.2.1Conception et simulation l'Amplificateur opérationnel à deux étage | 100. |

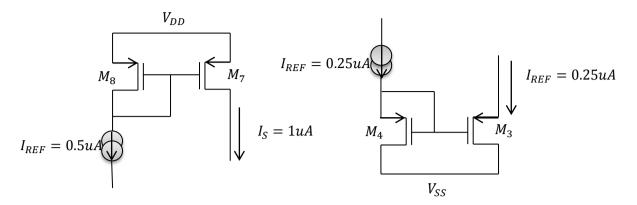

| V.2.2.1.1 Miroir de courant                                                | 100. |

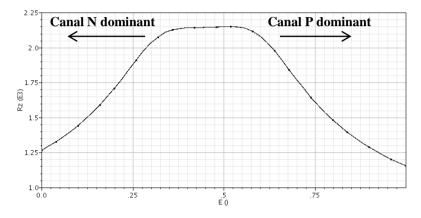

| V.2.2.1.2Résistance Active                                                 | 102. |

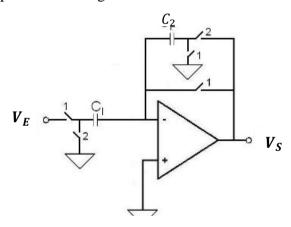

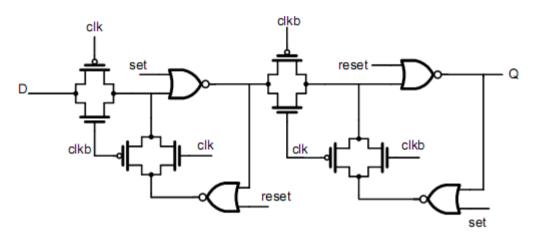

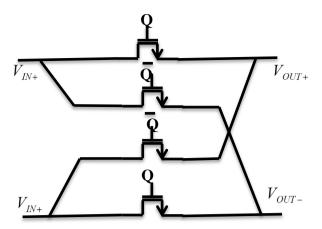

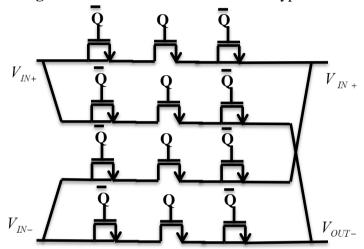

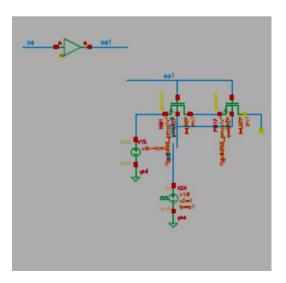

| V.2.3.Structure de chopper stabilisé                                       | 103. |

| V.3. Simulation et Discussion.                                             | 104. |

| V.3.1. Paramètresde dispositifs.                                           | 104. |

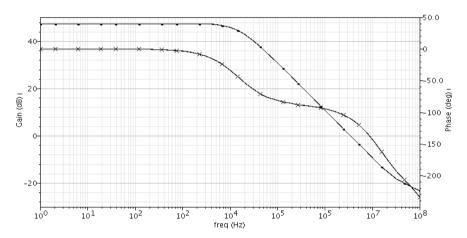

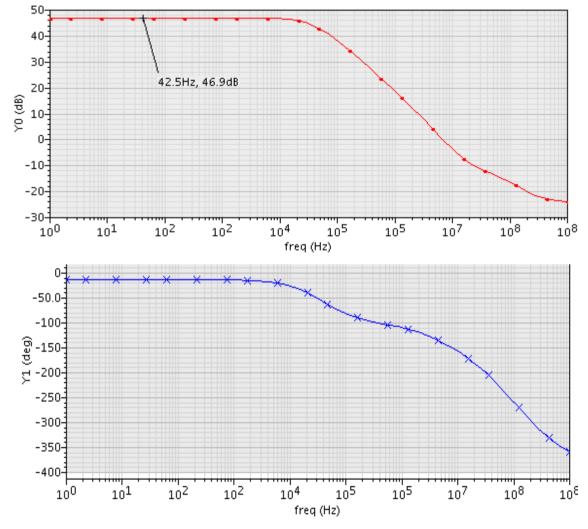

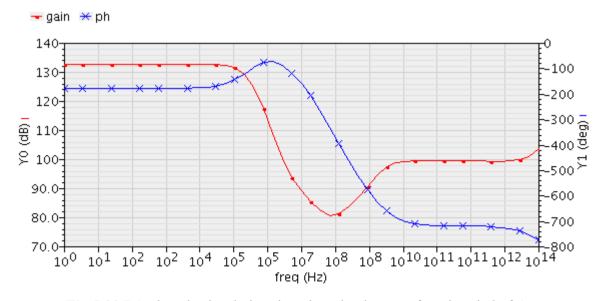

| V.3.2. Réponse en fréquence, Compensation.                                 | 105. |

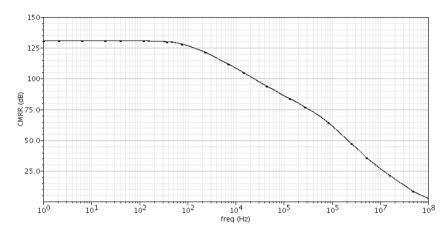

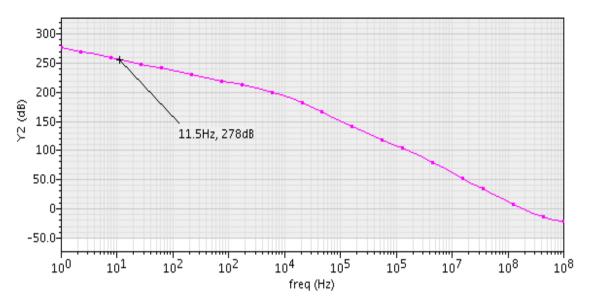

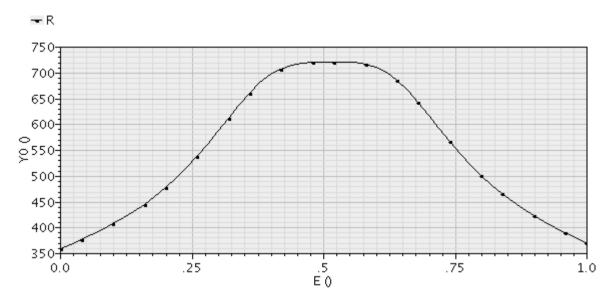

| V.3.3Taux de rejeten mode commun CMRR                                      | 107. |

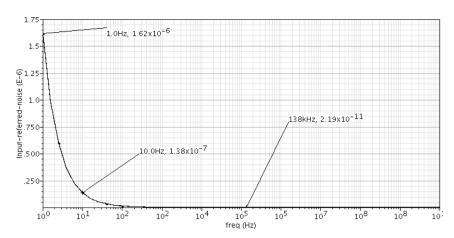

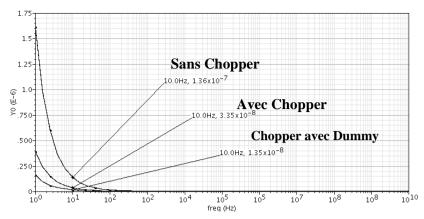

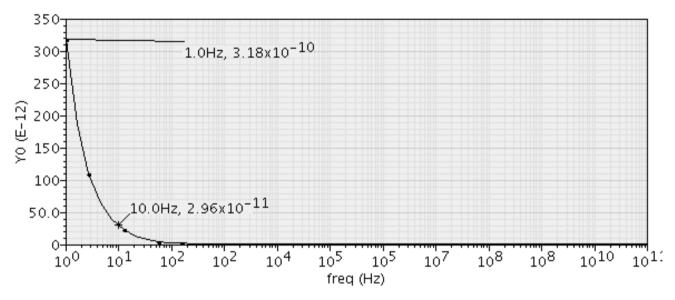

| V.3.4Performance du Bruit.                                                 | 108. |

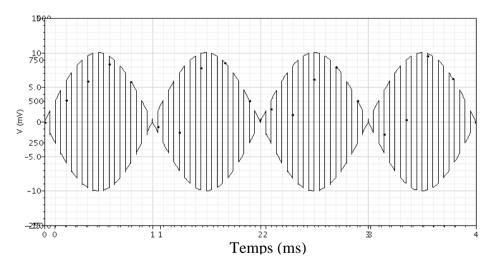

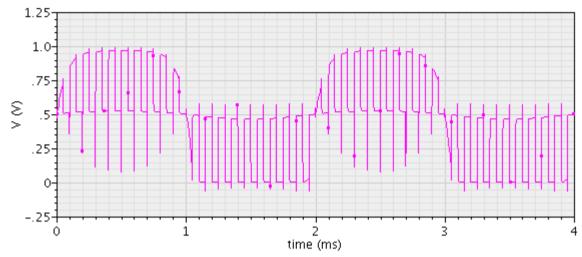

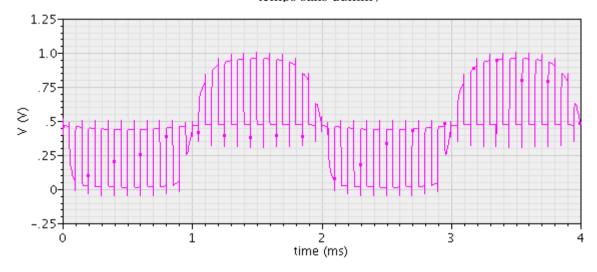

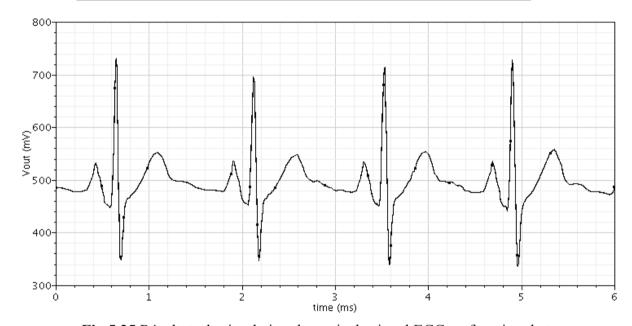

| V.3.5Performance de technique de découpage (Chopper)                       | 109. |

| V.3.6Performance globale de l'amplificateur opérationnel                   | 111. |

| V.4 Amplificateur Opérationnel entièrement différentiel                    | 112. |

| V.4.1 Performance du Taux de rejet en mode commun                          | 113. |

| V.4.2 Performance du Gain et de la Phase.                                  | 113. |

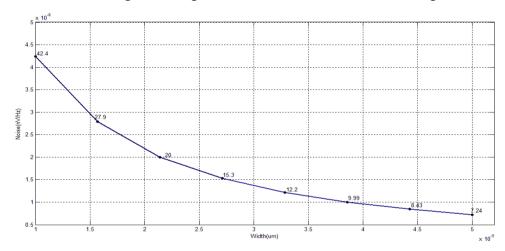

| V.4.3 Performance du Bruit.                                                | 115. |

| V.4.4.Performance globale de l'amplificateur opérationnel                  | 115. |

| V.5 Convertisseur Analogique Numérique SAR                                 | 116. |

| V.5.1 Convertisseur Numérique analogique CNA à réseaux capacitif pondérés  | 117. |

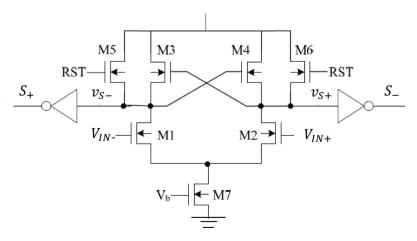

| V.5.2. Performance du comparateur.                                         | 118. |

| V.5.2.1. Performance du Gain et de la phase                                | 119. |

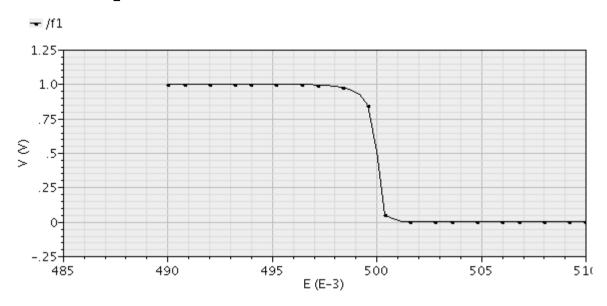

| V.5.2.2. Performance de la sortie.                                         | 120. |

| V.5.3. Performance du Commutateur                                          | 120. |

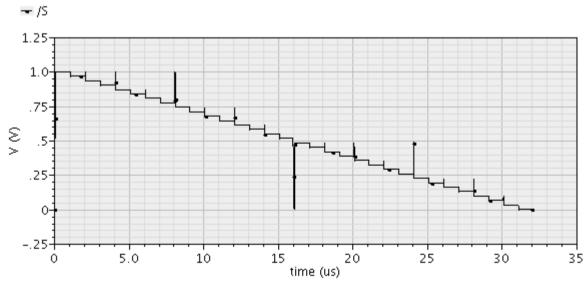

| V. 5.4. Performance de registre à approximation successive                 |

|----------------------------------------------------------------------------|

| V.5.5. Performance du Convertisseur Analogique Numérique CAN-SAR123.       |

| V.6. Conclusion.                                                           |

| Conclusion générale                                                        |

| Bibliographie                                                              |

| Chapitre 5                                                                 |

| Simulation et Résultats                                                    |

| V.1 Introduction                                                           |

| V.2 Système d'acquisition de données pour signal ECG                       |

| V.2.1 Signal ECG                                                           |

| V.2.2 Amplificateur opérationnel choper stabilisé pour Signal ECG          |

| V .2.2.1Conception et simulation l'Amplificateur opérationnel à deux étage |

| V.2.2.1.1 Miroir de courant                                                |

| V.2.2.1.2Résistance Active                                                 |

| V.2.3.Structure de chopper stabilisé                                       |

| V.3. Simulation et Discussion                                              |

| V.3.1. Paramètresde dispositifs                                            |

| V.3.2. Réponse en fréquence, Compensation                                  |

| V.3.3Taux de rejeten mode commun CMRR                                      |

| V.3.4Performance du Bruit                                                  |

| V.3.5Performance de technique de découpage (Chopper)                       |

| V.3.6Performance globale de l'amplificateur opérationnel                   |

| V.4 Amplificateur Opérationnel entièrement différentiel                    |

| V.4.1 Performance du Taux de rejet en mode commun                          |

| V.4.2 Performance du Gain et de la Phase                                   |

| V.4.3 Performance du Bruit                                                 |

| V.4.4.Performance globale de l'amplificateur opérationnel                  |

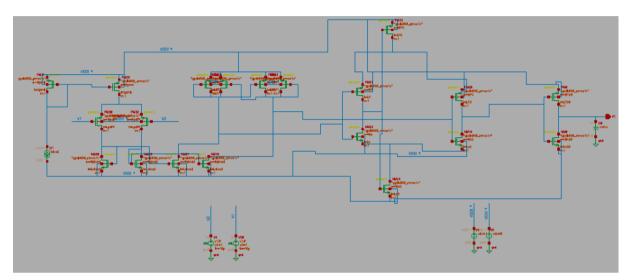

| V.5 Convertisseur Analogique Numérique SAR                                 |

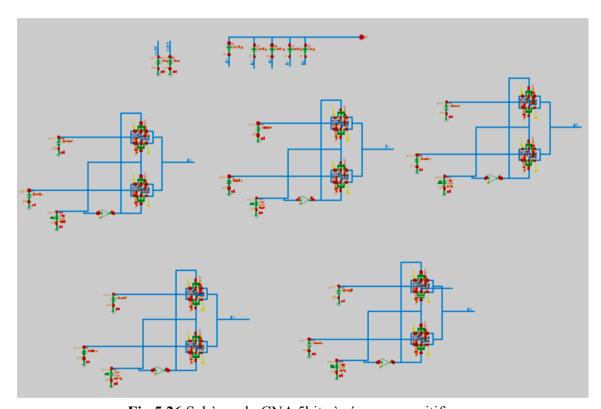

| V.5.1 Convertisseur Numérique analogique CNA à réseaux capacitif pondérés  |

| V.5.2. Performance du comparateur.                                         |

| V.5.2.1. Performance du Gain et de la phase.                               |

- V.5.2.2. Performance de la sortie.

- V.5.3. Performance du Commutateur

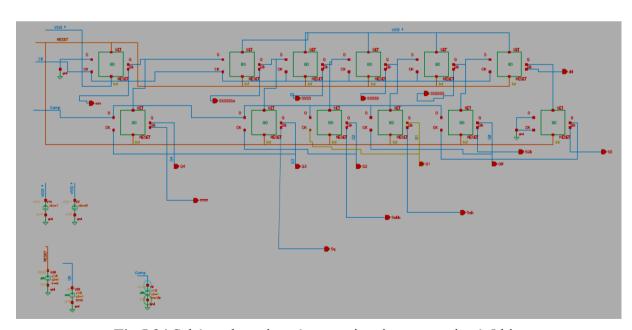

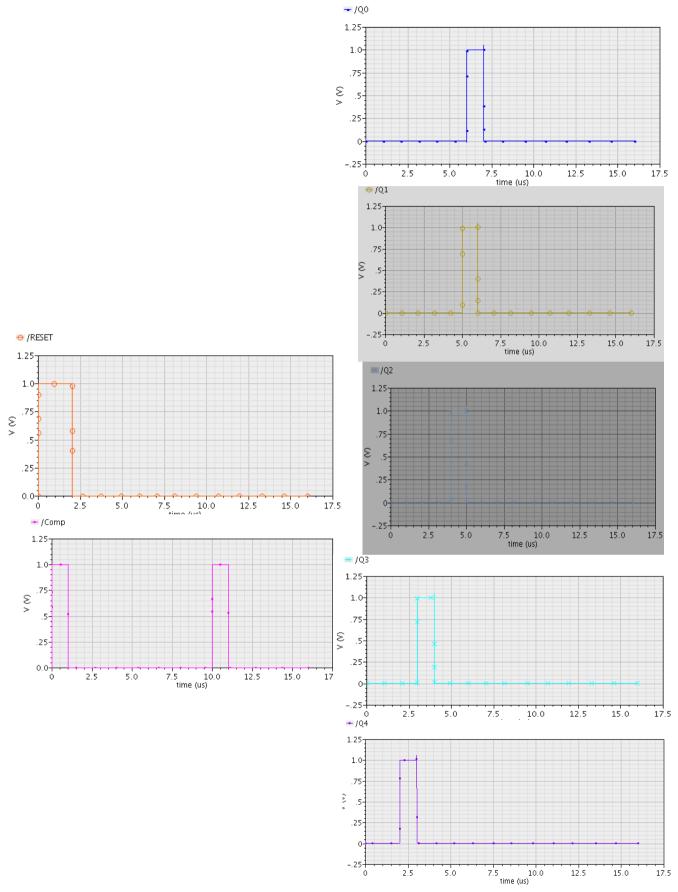

- V. 5.4. Performance de registre à approximation successive.

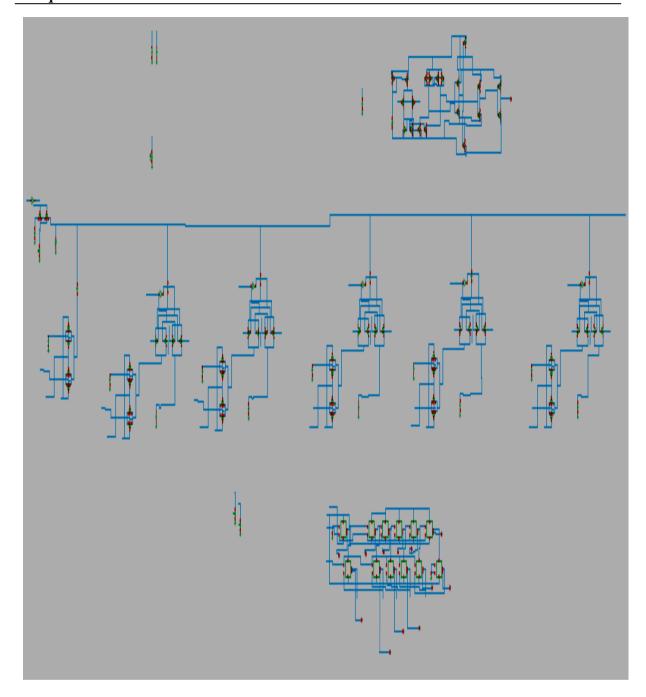

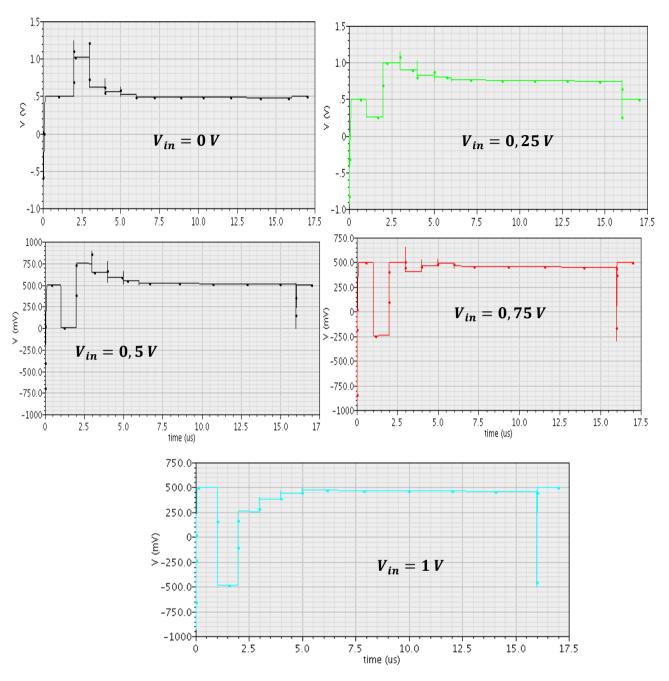

- V.5.5. Performance du Convertisseur Analogique Numérique CAN-SAR.

- V.6. Conclusion.

## Introduction générale

De nos jours, les fabricants de semi-conducteurs produisent des circuits intégrés (Integrated Circuits, **ICs**) de plus en plus complexes afin de répondre à la demande du marché. Ces circuits intégrés incluent, sur la même puce, des circuits analogiques, numériques et mixtes très performants.

Les progrès au cours des dernières années, dans le domaine de la microélectronique s'expliquent non seulement par le perfectionnement des procédés de fabrication des circuits intégrés, mais aussi par l'intervention de l'informatique à travers la Conception Assistée par Ordinateur (CAO). En effet, lors de la conception d'un circuit intégré, outre les principaux critères d'optimisation utilisés (surface de la puce, rapidité de fonctionnement, consommation...), le temps de conception lui-même est un paramètre très important. A mesure qu'augmente le nombre de transistors intégrés sur une puce, l'aide apportée par la CAO devient primordiale et la simulation du circuit avant fabrication incontournable. Or cette étape de simulation peut être considérablement ralentie en raison de la complexité croissante des circuits soumis aux logiciels de simulation [1].

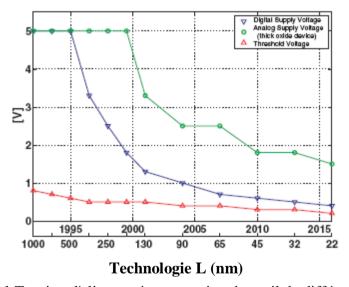

Avec la diminution de la longueur de Transistors (L) rapidement vers le bas (≈nm), conduisant à une augmentation du nombre de composants dans une même puce. Ces progrès continuent en électronique analogique et numérique impliquant également plusieurs inconvénients pour la conception des systèmes à faible consommation de puissance où la réduction de la tension d'alimentation interfère avec le courant d'attaque des transistors résultant dans des vitesses plus lentes [2] en plus à la complexité requise pour l'essai et la fabrication [3] [4][5].

Les concepteurs de circuits VLSI ont toujours pris comme métriques la vitesse, un grand gain et une petite surface en termes de performance. En général, une grande performance et une petite surface sont deux contraintes qui sont toujours en conflit. Les concepteurs de circuits intégrés cherchent un compromis entre ces contraintes [6]. En effet, les considérations de la puissance sont récentes, notamment dans les systèmes portables tels que les micro-ordinateurs, les téléphones sans fil, les montres et les différents systèmes implantables chez l'être humain (Stimulateur cardiaque : Pacemaker, implant visuel, implant urinaire, implant de rétine et implant cochléaire, .....etc.) [7] [8]. En outre, la demande pour les petits circuits à basse tension d'alimentation et faible consommation de puissance a considérablement augmenté dans le domaine des soins médicaux pour la surveillance des

soins de santé. L'objectif de toutes ces applications est la réalisation des fonctions à une faible consommation de puissance pour une longue période d'alimentation.

Actuellement, basse tension d'alimentation et faible consommation de puissance est devenue une contrainte importante dans la conception de circuits CMOS pour les circuits médicaux. Pour différentes raisons, parmi lesquelles nous citons:

- Les systèmes alimentés par une pile tels que: les systèmes implantables, les Microordinateurs portables, les agendas électroniques...etc. Le besoin grandissant de ces systèmes augmente le besoin de prolonger la durée de vie de la pile. Puisque la technologie des piles offre des améliorations limitées, les techniques de conception à faible puissance sont essentielles pour les dispositifs portables.

- L'effet de baisser la tension d'alimentation aux plus faibles niveaux possibles peut être très impressionnant en termes d'économie de consommation en énergie. Non seulement l'énergie consommée, mais aussi le poids et le volume des systèmes opérant avec des batteries seront réduits.

- Actuellement La conception de systèmes A faible consommation en énergie est devenue une performance très importante dans le domaine médical, tel est le cas de plusieurs applications, comme les systèmes portables alimentés par une pile, Par exemple: les implants médicaux. Ces systèmes représentent une importante augmentation dans le marché.

#### Implants médicaux en microélectroniques

Un implant médical électronique est défini comme tout type de dispositif médical qui implante des composants électroniques et est implanté à l'intérieur du corps pour obtenir une réponse physiologique. Le premier implant médical microélectronique était un stimulateur cardiaque (Pacemaker), dès 1970. Mais beaucoup d'autres implants sont actuellement en usage, comme neuro-stimulateurs et implantables pompes à perfusion de médicaments, implant urinaire, implant cochléaire etc.

Au cours des dernières années, l'utilisation de dispositifs médicaux implantables a augmenté. Les dispositifs médicaux utilisés pour le traitement de différentes maladies, ont des exigences et les spécifications différentes, néanmoins il existe plusieurs caractéristiques qui sont partagés par la plupart d'entre eux.

- Faible consommation de Puissance : Modification ou charger les batteries peuvent être inconfortables, difficile, coûteux et même risqué pour le patient, tous dispositifs médicaux implantables ont besoin de consommer le moins de puissance possible.

- ➤ Haute fiabilité : Une défaillance d'un dispositif médical implantable peut entraîner sur désagrément, douleur, dommages ou même la mort pour le patient.

- Signaux faible amplitude: La plupart des signaux physiques à l'intérieur d'un corps humain sont de l'ordre mV ou uV ce qui nécessite une attention particulière dans la détection et l'amplification.

- **Basses fréquences:** La durée de la fréquence naturelle des signaux biologiques varient à partir d'une fraction hertz à quelques kilohertz.

- Petite taille : Les dispositifs implantables doivent être aussi petit que possible, de manière être moins invasive pour le corps humain.

Le signal Electrocardiographie (ECG) est principalement utilisé dans la détection des maladies du cœur tel que maladies coronarienne, Maladies du muscle cardiaque, Maladies des valves cardiaques .....

Aujourd'hui, les techniques pour capturer et traiter le signal ECG sont utilisées dans des Systèmes médicaux.

Le signal ECG est une technique semi-invasive pour enregistrer des signaux électriques en plaçant des électrodes sur la peau. Les bio-potentiels électriques produits par l'activité cardiaque, peut être capturé par des systèmes stationnaires et ambulatoires ECG. Systèmes stationnaires sont utilisés principalement dans les hôpitaux ou cliniques; systèmes ambulatoires sont utilisés pour l'enregistrement du signal ECG.

La nécessité du signal ECG ambulatoire pour le système de dispositif médical et les tendances de la mise à l'échelle dans le canal en technologie CMOS conduire la nécessité d'élaborer des circuits travailler à basse tension d'alimentation. En outre, une faible consommation de puissance est essentielle dans ce système afin d'avoir une plus longue vie de la batterie.

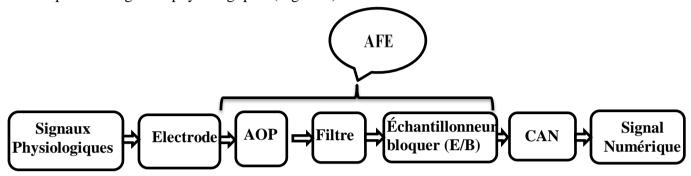

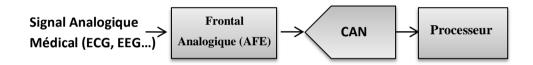

#### Système médical pour signaux physiologiques

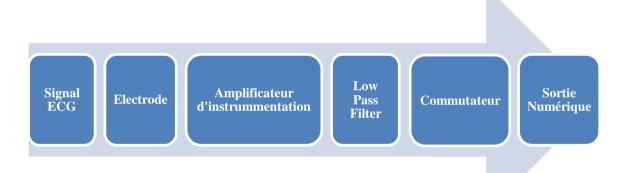

Figure 1 décrit le système d'acquisition des signaux physiologiques. Le Système est constitué deux éléments essentiels, le premier c'est le circuit frontal analogique (Analog Front End: AFE) et le deuxième c'est Convertisseur Analogique Numérique (CAN). Le signal

acquis par des électrodes placées sur la peau est amplifier par un amplificateur opérationnel basse tension puis convertie en un code numérique afin d'être traité.

#### Méthodologie de la recherche

Ce travail s'adresse la contribution à la conception des circuits en technologie CMOS pour des signaux physiologiques (Figure 1).

Fig. 1 Système d'acquisition des signaux physiologiques

Le système d'acquisition est un système critique, où les plus importants paramètres sont : le coût, la puissance, la résolution, le bruit et la surface. Les composants principaux d'un traditionnel système d'acquisition comprennent un amplificateur opérationnel (AOP), des filtres, les commutateurs analogiques et Convertisseur Analogique Numérique (CAN).

Les signaux d'entrées ont très faible d'amplitude et de basse fréquence, cependant, le signal médical est trop faible à détecter, par conséquent, nous avons besoin d'un amplificateur opérationnel (AOP) de gain élevé, un CMRR très élevé, un PSRR élevé, une impédance d'entrée élevée et une faible consommation de puissance pour réduire l'effet de bruit et pour amplifier le signal médical seulement. Puis le signal passé dans un filtre, échantillonneur bloqueur analogique et finalement dans le CAN pour devenir un signal numérique. Après cela, ces données numériques seront traitées dans les Processeurs. Un défi majeur dans les dispositifs médicaux implantables est la conception de l'efficacité des circuits à faible bruit et basse tension d'alimentation. Par exemple stimulateurs cardiaques (Pacemaker) détecté des signaux cardiaques de l'activité d'amplitude de dizaines millivolts à quelques millivolts, les signaux nerveux EEG vont de 1uV ou moins de 1mV. Il est bien connu en effet que dans la gamme de fréquences de signaux médicaux, les sources de bruit les plus fréquentes dans les circuits CMOS sont bruit 1/f et bruit thermique. Pour réduire le bruit 1/f en utilisant large transistor ou l'utilisation des techniques comme auto zéro technique ou chopper technique. L'efficacité des circuits faible bruit signifie qu'il est capable d'amplifier des signaux ayant le

moins bruit à une consommation de puissance donnée; la zone de circuit occupé peut aussi être une contrainte importante [9][10][11][12][13][14][15].

#### **Objectifs**

La conception des systèmes implantables (Implant), pour récupérer des fonctions perdues chez l'être humain constitue un domaine de recherche moderne, en pleine expansion, et très diversifié.

Les signaux bioélectriques sont en général lents et de faible amplitude. Ces amplitudes sont de l'ordre de 0.5mV. De ce fait, il est nécessaire de concevoir un amplificateur opérationnel afin d'augmenter les performances du circuit frontal analogique. Aussi un CAN pour convertir ces signaux et traité dans un PC, spécialement adapté à ce domaine de recherche se fait de plus en plus grandissant.

L'objectif de cette thèse est de concevoir des circuits en technologie CMOS 90nm dédiés à des systèmes implantables, opérant à une tension d'alimentation de 1V, servant d'interface entre l'organe du patient et la partie de contrôle d'un l'implant.

Ces circuits doivent être conçus à l'aide du procédé de la technologie CMOS 90nm et des outils Analog Artist de Cadence, en utilisant le simulateur Spectre. En outre, l'étage d'amplification opérationnel chopper stabilisé dans le circuit analogique frontal (AFE), devra avoir un gain élevé, occupant la plus petite surface possible, une consommation de puissance très faible, un niveau de bruit très faible, une bonne fiabilité et une bonne caractéristique de linéarité pour amplifier les signaux physiologiques tel que le signal ECG et les circuits qui sont constitués l'architecture de convertisseur analogique numérique SAR (Successive Analog Register) devront avoir des performances très élevées. Ces circuits viennent du fait que l'on travaille avec une tension d'alimentation de 1V et l'on désire optimiser en priorité la consommation de puissance et la surface occupée par le circuit tout en ayant des performances très élevé.

L'objectif principal du projet consiste la contribution à la conception de ces circuits analogique dans domaine médical Figure.1. Pour accomplir ces objectifs, les étapes suivantes ont été suivies :

- Une revue de littérature appropriée sur les différentes architectures d'amplificateur opérationnel, commutateur analogique, filtre et convertisseur analogique numérique, opérant à une basse tension d'alimentation:

- Etude détaillée des techniques de conception de circuits analogiques opérant à une basse tension d'alimentation;

Simulation des circuits CMOS pour application médicale en utilisant l'outil Analog

Artist de Cadence et le simulateur Spectre;

#### Organisation de la Thèse

- Après une introduction générale dans laquelle nous avons discuté, basse tension d'alimentation et la faible consommation de puissance, des applications de la faible consommation de puissance, de la méthodologie de conception des systèmes à faible consommation de puissance, Implants médicaux en microélectroniques, système médical pour signaux physiologiques et enfin de la méthodologie de la recherche.

- Cette thèse sera organisée en cinq chapitres. Le premier chapitre fait le principe de fonctionnement des signaux physiologiques et circuits médicaux.

- Le deuxième Chapitre : Détaille le principe du signal ECG et les interférences existées.

- Le troisième Chapitre: Représente les éléments nécessaire de l'interface analogique AFE permis ces éléments : les amplificateurs, Filtres, les commutateurs analogiques .....

- Le quatrième chapitre : Décrit la conception du convertisseur analogique numérique SAR.

- Le cinquième chapitre : Représente la simulation et résultats, des circuits amplificateur opérationnel chopper stabilisé pour circuit frontal analogique et les circuits de CAN SAR qui ont été choisis en technologie CMOS 90nm dans le domaine médical.

- Nous terminons notre travail par une conclusion générales, récapitule notre contribution et discute les améliorations qui peuvent être apportées. Les orientations futures du présent travail y sont également abordées.

## Chapitre 1

## Circuits et Signaux Médicaux

- I.1. Introduction

- I.2. Signaux médicaux

- I.3. Circuits médical

- I.3.1. Implant Cochléaire et prothèse auditive

- I.3.2. Implant urinaire

- I.3.3. Implant Intra-corticale prothèse visuelle

- I.3.4. Implant du Cerveau

- 1.3.5. Implant Pacemaker

- 1.4. Conclusion

#### Chapitre 1

## Circuits et Signaux Médicaux

#### I.1 Introduction

Puces semi-conducteur sont utilisées aujourd'hui, non seulement dans les systèmes de communication ou de commande, mais aussi dans nos corps, pour les signaux de diagnostic ou de surveillance, comme l'électroencéphalographe (EEG), l'électrocardiographie (ECG) et l'électromyogramme (EMG), pour comprendre l'activité électrique du cerveau, du cœur et du muscle et traiter à l'intérieur des circuits de l'implant. De nos jours, la conception de systèmes implantables pour récupérer les fonctions perdues chez l'être humain, constitue un domaine de recherche moderne, en plein expansion, et très diversifié. Les implants sont classés en deux grandes catégories : (1) les capteurs servant à surveiller l'évolution des paramètres biologiques et (2) les stimulateurs dédiés à la récupération des fonctions. La recherche se poursuit pour développer de nombreux différents types de dispositif électroniques médicaux qui peuvent donner des prothèses pour les traitements d'une série de large maladies, telles que la cécité, la quadriplégie, l'épilepsie, la maladie de Parkinson et les maladies des cœurs. Ces dispositifs électroniques sont utilisés en particulier dans des applications médicales. Ces caractéristiques sont indispensables parce que les appareils sont difficiles d'accès et la conséquence sont graves si le dysfonctionnement de ces dispositifs, ce qui exige une bon connaissance sur le comportement de la matière. [16][17].

#### I.2 Signaux Médicaux

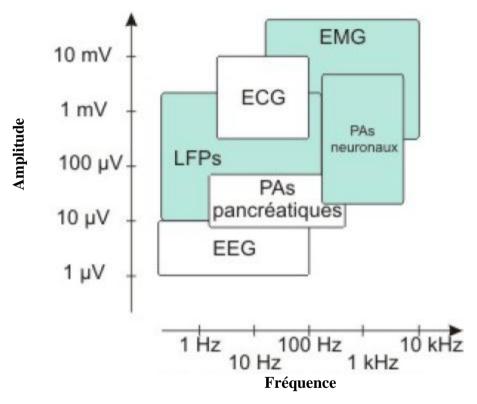

Les signaux bioélectriques sont, en général, lents et de faibles amplitudes de l'ordre uV ou mV tableau 1.1. De ce fait, on a besoin de concevoir des circuits en technologies CMOS spécialement adaptés au ce domaine.

| Signal | Fréquence  | Amplitude |

|--------|------------|-----------|

| ECG    | 0.05-250Hz | 5uV-8mV   |

| EEG    | 0.5-200Hz  | 2uV-200uV |

| EMG    | 0.01-10KHz | 50uV-10mV |

Table 1.1 caractéristique des signaux physiologiques

Pour acquérir et enregistrer des signaux bioélectriques, comme ECG, EEG et EMG pour aider à la compréhension des signaux de comportement du cerveau, du cœur et du muscle nécessite un traitement de signaux dans un circuit électronique intégré de l'implant [18]. En règle générale, le bruit est généré par de nombreuses applications courantes tels que les lignes électriques, les lampes fluorescentes, micro-ordinateur et moniteurs, et qui est ajouté et amplifié avec les signaux médicaux. La figure 1.1 propose un aperçu de la localisation et de la plage de tension/fréquence de certains signaux électriques médicaux mesurables dans le corps humain.

**Fig.1.1**. Localisation des principaux signaux électriques du corps humain. [17]

- Les Electrocardiogrammes (ECG) qui sont une représentation graphique du potentiel électrique qui commande l'activité musculaire du cœur.

- Les Electromyogrammes EMG qui représentent l'activité électrique des muscles.

- Les Potentiels d'action PAs neuronaux et LFPs (Local field potentials) qui correspondent à l'activité électrique des cellules nerveuses.

- Les PAs pancréatiques qui correspondent à l'activité électrique des cellules du pancréas.

Ces signaux représentent une activité électrique provenant de cellules ou d'organes représentative des nombreuses fonctionnalités du corps humain. Selon les méthodes

d'enregistrement ou la nature même de l'objet vivant étudié, l'activité électrique d'une cellule vivante diffère [17].

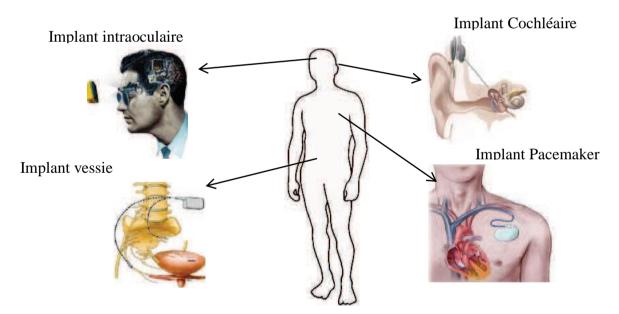

#### I.3 Circuits Médicaux

Avec le développement de la microélectronique, circuit intégré, technologies des matériaux et de la micromécanique, il y a eu un grand progrès dans l'électronique médicale. Les scientifiques et les ingénieurs de l'industrie et de l'université ont travaillé ensemble pour créer un nouveau équipement médical qui ne existait pas dans les fictions scientifiques dans le passé, tels que: Implant Cochléaire et prothèse auditive, Implant Pacemaker, Implant Intraoculaire, Implant urinaire, Implant du cerveau. Ces implants médicaux ont été récemment utilisés pour des applications médicales dans le corps humain, pour la surveillance ou l'enregistrement de signaux médicaux Figure 1.2. Principalement nous devons comprendre les troubles de comportement du corps tels que le cerveau et le cœur....., et les traiter dans le circuit de l'implant. Ces implants médicaux peuvent résoudre de nombreux troubles médicaux.

Fig.1.2. Applications des implants médicaux dans le corps humain [17]

#### I.3.1. Implant cochléaire et prothèse auditive

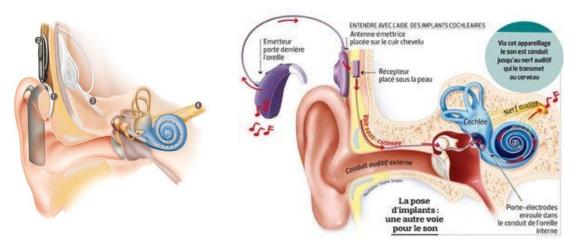

Un implant cochléaire est un appareil électronique ultra-miniaturisé médical qui remplace les fonctions endommagées de l'oreille interne c.-à-d. restaurer l'audition à des personnes souffrant d'une surdité profonde à sévère. Contrairement aux prothèses auditives qui amplifient les sons, les implants cochléaires remplissent les fonctions normalement prises en charge par les parties endommagées de l'oreille interne (cochlée) afin de fournir au cerveau des signaux sonores. Schématiquement, cet appareil se compose d'un microphone qui

capte les signaux sonores avant de les transmettre à un processeur vocal qui les traduira et les transmettra à des électrodes capables de stimuler le nerf auditif. La surdité "de transmission" est généralement traitée par des appareils externes, aides auditives, plus communément appelées prothèses auditives figure 1.3.

- 1. **Un processeur** porté derrière l'oreille ou sur le corps capte les sons et les transforme en un code numérique. Le processeur est équipé d'une pile qui alimente tout le système.

- 2. Le processeur transmet le son sous forme numérique à l'implant par le biais de

Fig.1.3 Implant cochléaire [19][20]

- 3. **L'antenne** positionnée sur votre tête.

- 4. **L'implant** convertit le son codé numériquement en impulsions électriques qu'il transmet au faisceau d'électrodes situé dans la cochlée (oreille interne).

- 5. Les électrodes de l'implant stimulent le **nerf auditif** de la cochlée, qui envoie les impulsions au cerveau où elles sont alors interprétées comme des sons.

Ils se composent tous d'une partie externe et d'une partie interne. La partie externe comporte un ou plusieurs microphones qui captent l'environnement sonore et transforment le son en signal électrique, un processeur qui filtre les informations sonores reçues, afin notamment de traiter en priorité la voix humaine, et les répartir sur différents canaux. Ce bloc rempli généralement l'arrière du pavillon de l'oreille. Les impulsions électriques sont dirigées ensuite vers le transmetteur à travers un fin fil conducteur. Ce transmetteur est maintenu par un aimant placé derrière l'oreille externe, c'est lui qui fournit à la partie interne de l'appareil et de manière sans fil l'énergie nécessaire à son fonctionnement ainsi que les signaux électriques traités par le processeur [20].

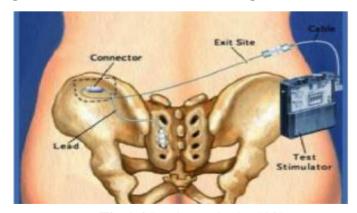

#### I.3.2. Implant urinaire

L'appareil urinaire est l'appareil permettant l'évacuation des produits du catabolisme du corps humain sous une forme liquide, l'urine II assure par conséquent l'épuration du sang ainsi que le maintien de l'homéostasie au sein de l'organisme. Il rentre dans la fonction physiologique de *nutrition* comme le système circulatoire (avec le cœur). Cet appareil est une succession d'organes: les deux reins, les deux uretères, la vessie et l'urètre. La continence urinaire nécessite un plancher pelvien fonctionnant correctement (muscles du périnée), une intégrité des sphincters (muscle à la base de l'urètre) et des commandes nerveuses agissant sur ceux-ci et sur le détrusor (muscle de la paroi de la vessie dont la contraction aboutit à sa vidange) Figure 1.4. Toute altération de l'une de ces structures peut conduire à l'incontinence. On distingue plusieurs types d'incontinence urinaire [20] [22]:

- 1. L'incontinence d'effort est la forme la plus fréquente. Elle est caractérisée par une fuite involontaire d'urine survenant à l'occasion d'un effort physique : toux, rire, exercice physique, rapport sexuel. Tout effort abdominal engendre une pression sur les muscles du plancher pelvien qui doivent être tendus pour assurer la fermeture de l'urètre. Si ces muscles sont faibles, ils ne peuvent pas maintenir la tension. Lorsque la tension est relâchée, l'urètre s'ouvre et un peu d'urine peut s'échapper.

- 2. Ensuite nous avons l'hyperactivité vésicale ou incontinence urinaire par urgence qui survient lorsque le besoin d'uriner se manifeste brusquement, sans donner le temps d'aller jusqu'aux toilettes. Cela correspond à une contraction involontaire de la vessie, qui entraîne une vidange partielle ou complète des urines. Les personnes peuvent fréquemment ressentir le besoin d'aller aux toilettes, le jour comme la nuit, sans pour autant souffrir de fuites urinaires.

- 3. Enfin le dernier type est l'incontinence mixte. Elle associe les symptômes de plusieurs types d'incontinence, généralement l'incontinence d'effort et l'urgence mictionnelle. L'une des deux composantes peut être dominante, et c'est celle-ci qu'il faudra traiter en priorité.

Fig.1.4 Implant urinaire [23]

Lors de l'incontinence urinaire d'effort on peut disposer d'un stimulateur de sphincter implantable. Il s'agit d'un stimulateur musculaire. Son rôle est généralement de faire travailler le muscle pour qu'il retrouve son tonus initial.

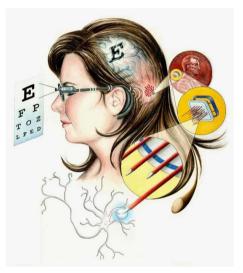

#### I.3.3. Implant Intra-corticale prothèse visuelle

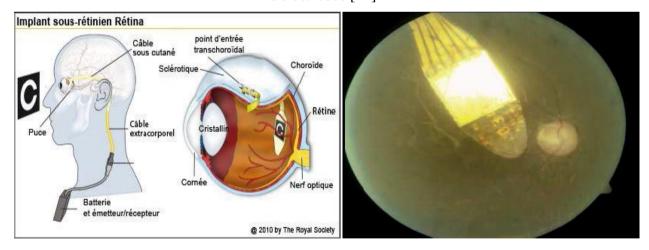

L'une des principales zones de croissance dans la demande de recherche est implant rétinien ou de la technologie de l'œil bionique, pour aider les patients aveugles ou souffrant de maladies de la rétine avec leur vue, et aider les gens à avoir une idée de leur environnement. Le dispositif de rétine artificielle s'adresse aux personnes dont les cellules photo-réceptrices ont dégénéré mais chez lesquelles les cellules nerveuses de la rétine et le nerf optique demeurent actifs [22] Figure 1.5.

**Fig.1.5**. Implant Intra-corticale prothèse visuelle [24]

L'implant rétinien est proposé au patient dont les pathologies susnommées sont tellement avancées qu'ils en ont perdu la vue. Gardons en tête qu'il s'agit d'implant au contact du SNC (Système Nerveux Central) donc avec fort risque de complication, c'est généralement le dernier espoir de recouvrer la vue. Cet implant fixé sur ou sous la rétine permet au patient de percevoir à nouveau des signaux lumineux. La rétine artificielle se substitue aux cellules pour stimuler les neurones résiduels de la rétine et rendre en partie la vue au patient. Il s'agit notamment d'un implant de 3x3 mm fixé sur ou sous la rétine et composé d'électrodes qui stimulent les neurones rétiniens. Les premiers essais ont débuté dans les années 1990 avec des dispositifs incluant 16 à 20 électrodes. Ils en comportent actuellement jusqu'à 1.500.

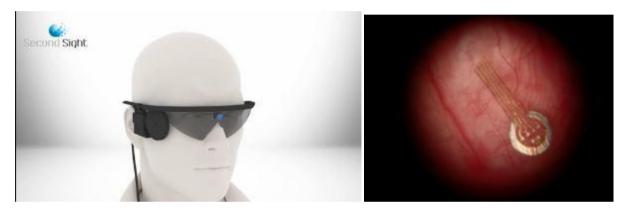

Il existe actuellement deux types de dispositifs qui offrent des résultats similaires. L'un est placé à la surface de la rétine, en contact avec les cellules ganglionnaires (Argus II, *Second Sight*, Etats-Unis) et l'autre est placé sous la rétine à la place des cellules photo-réceptrices (*Retina Implant* AG, Allemagne).

Dans le cas de l'implant américain, une caméra est fixée à une paire de lunettes Figure.

1.6. Elle transmet les images à un processeur placé dans la poche ou à la ceinture du patient.

Le processeur convertit les signaux lumineux en signaux électriques, les traites, puis les transmet par ondes radio à un récepteur placé sur l'œil. Celui-ci les communique grâce à un fil à l'implant composé de 60 électrodes et placé au contact de la rétine.

L'implant allemand fonctionne différemment. Il comprend 1.500 électrodes et autant de diodes sensibles à la lumière. Les diodes excitées par la lumière activent directement les électrodes au niveau de la rétine sans l'intermédiaire de lunettes ou de processeur Figure 1.7.

Dans les deux cas, une intervention chirurgicale est nécessaire pour la mise en place de l'implant au contact de la rétine, comprenant ainsi un certain nombre de risques.

**Fig.1.6** Implant épirétinal Argus II, *gauche:* dispositif externe *droite:* dispositif interne: matrice d'électrodes [22]

**Fig.1.7** Implant subrétinal Retina Implants. *gauche:* schéma d'installation du dispositif, *droite:* dispositif interne: diodes photo-réceptrices [22]

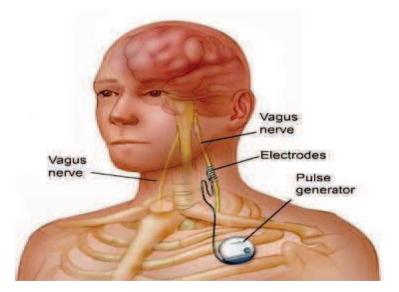

#### I.3.4 Implant du Cerveau

La stimulation cérébrale profonde (*Deep Brain Stimulation ou DBS*) est une procédure neurochirurgicale. On implante un dispositif médical dans le cerveau qui envoie des impulsions électriques à des zones spécifiques pour le traitement de certains troubles affectifs ou des troubles du mouvement. En effet pour certains troubles résistants au traitement médicamenteux la DBS a procuré des améliorations de l'état du patient (diminution des symptômes) notamment pour la maladie de Parkinson, le tremblement essentiel, la dystonie, la douleur chronique, la dépression majeure et le trouble obsessionnel compulsif [25]. Les zones stimulées du cerveau peuvent varier selon l'indication, et le mécanisme n'est pas très clair. En effet la stimulation peut tout aussi bien activer qu'inhiber l'activité des neurones. mais de manière générale on assiste à la diminution de l'activité spontanément oscillante du thalamus [26]. Son utilisation a été longtemps controversée et est encore actuellement un sujet de polémique [27]. Ses effets sont réversibles, elle a donc remplacé la lobotomie interdite à présent dans de nombreux pays et considérée comme une mauvaise pratique dans la médecine actuelle. Le dispositif décrit dans la Figure 1.8 consiste en un boîtier interne, appelé neurostimulateur, généralement situé sous la clavicule, qui sert de processeur et de source électrique. Il est réglable par le médecin selon la stimulation souhaitée grâce à une télécommande externe. Un ou plusieurs extenseurs partent du boîtier pour monter jusqu'au niveau du crane qui a été percé pendant l'opération. Depuis les extenseurs partent des fils semi rigides qui sont insérés dans le cerveau du patient jusque dans la zone recherchée (thalamus). Ces fils sont terminés par de petites électrodes qui serviront de contact avec le SNC. Notez que les fils porteurs des électrodes ne doivent pas être rigides comme des aiguilles car ils doivent pouvoir suivre les mouvements du cerveau lorsque la tête bouge, même en cas de choc. Cependant ils ne doivent pas être trop souples car ils doivent servir de support lors de l'implantation des électrodes proche du thalamus.

Fig.1.8 Dispositif de stimulateur du cerveau

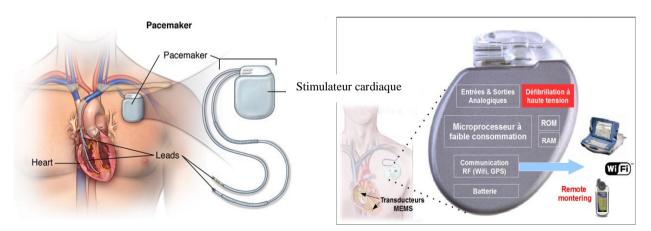

#### I.3.5. Implant Pacemaker (Stimulateur cardiaque)

Le stimulateur cardiaque, ou pacemaker, ou pile, est un dispositif implanté dans l'organisme fournissant des impulsions électriques destinées à stimuler les muscles cardiaques en permettant ainsi, par exemple, d'accélérer la pulsation du cœur lorsqu'il est trop lent. Au cours des dernières années il y a eu un taux élevé de la chirurgie des implants cardiaques artificiels et stimulateurs cardiaques pour surveiller et contrôler les rythmes cardiaques irréguliers, en particulier pour les bébés et les personnes âgées. Un cœur artificiel nouvellement développé est appelé le cœur artificiel à puce intelligente, créée en Afin de réaliser le traitement sûr et de contrôle efficace pour les patients [28].

Dans le cas de risque de fibrillations on peut insérer un Défibrillateur Automatique Implantable (DAI, implanté dès 1985). Ce dernier possède les fonctionnalités d'un stimulateur cardiaque classique (induit un rythme cardiaque correct) mais aussi la possibilité d'agir comme un défibrillateur automatique indispensable dans les cas de mort subite.

Le stimulateur cardiaque Figure 1.9 est composé d'un boîtier plat d'environ 3cm de diamètre et d'une ou plusieurs sondes. Le rôle du boîtier est d'assurer l'autonomie énergétique durant 5 à 7ans, le traitement des données (fréquence du rythme cardiaque et détection de fibrillation) et impulsions en cas de défaillance (mode sentinelle). Les sondes connectent le boîtier au cœur. Elles sont souvent vissées dans le myocarde pour rester toujours au contact du cœur en mouvement. Si le pacemaker a une fonction de défibrillateur, il est généralement bipolaire (ou à double chambre), c'est à dire qu'il a deux sondes connectées au boitier Figure 1.9, la première implantée dans le ventricule droite et la deuxième dans l'oreillette droite.

Fig.1.9 Implant pacemaker

#### **I.4 Conclusion**

Ce chapitre a montré un résumé sur les caractéristiques des signaux médicaux et aussi les fonctionnements des implants médicaux. Ces implants médicaux traitaient les troubles et maladies du corps humain telles que l'épilepsie, la paralysie, la maladie de Parkinson, et des troubles du cœur etc

## Chapitre 2

## Le signal ECG et les Interférences

| 77 | 1 | Intr  | 01  | 1104 | ion |

|----|---|-------|-----|------|-----|

| H. | • | Inter | oai | ист  | lOn |

- II.2 Système cardio-vasculaire

- II.2.1 Cœur

- II.2.2 Circulation sanguine

- II.3 L'électrophysiologie cardiaque

- II.3.1. Propriétés électro-physiologiques des cellules cardiaques

- II.3.2. Fonctionnement électrique du cœur

- **II.4**. L'électrocardiographie

- II.4.1. Système de Dérivations électrocardiographiques

- **II.4.1.1**. Dérivations périphériques

- II.4.1.1.1. Dérivations périphériques bipolaires

- II.4.1.1.2. Dérivations périphériques unipolaires

- II.4.1.2. Dérivations précordiales.

- II.4.1.2.1. Position des électrodes précordiales

- II.4.2. Signal électrocardiogramme

- II.4.2.1. Ondes enregistrées sur un ECG normal

- II.4.2.2. Segments et intervalles qui caractérisent un ECG normal

- **II.4.**3 Le rythme cardiaque

- II.5 Interférence

- **II.6** Conclusion

### Chapitre 2

## Le signal ECG et les Interférences

#### **II.1 Introduction**

Dans le monde occidental, la première cause de mortalité provient des maladies cardiovasculaires. Même si les connaissances acquises en cardiologie sont grandes, le cœur n'a pas encore dévoilé tous ses secrets. Pourtant les médecins disposent de nombreux moyens pour l'étudier et vérifier son bon fonctionnement. Notamment, ils utilisent l'électrocardiogramme, qui est une représentation graphique temporelle des différences de potentiels des forces électriques qui conduisent à la contraction musculaire cardiaque. L'électrocardiogramme contient énormément d'informations sur le fonctionnement et les éventuelles pathologies du cœur. Grâce à leur expérience, les médecins relèvent des pathologies éventuelles.

Toutefois, les enregistrements des électrocardiogrammes sont bien souvent bruités et parfois peu exploitables; c'est alors qu'intervient le domaine du traitement du signal. Il est possible de débruiter et d'analyser les électrocardiogrammes de façon automatique. L'importation des méthodes de traitement du signal appliquées à l'humain est en effet constituée d'un ensemble d'appareils (digestif, respiratoire, génital, urinaire et circulatoire) qui réalisent des fonctions de nutrition et de perpétuation de l'espèce. En réalité, l'examen ECG est un outil non invasif effectué par le médecin en vue d'explorer le fonctionnement du cœur par l'emploi des électrodes externes mises en contact de la peau. Il s'agit d'un signal qui reflète l'activité électrique du cœur. À partir du signal ECG, certains paramètres importants peuvent être extraits. En règle générale, les durées et les formes des différentes ondes sont considérés comme des signes indicateurs de certaines anomalies cardiaques. Par conséquence, les systèmes automatiques d'analyse du signal ECG, capables d'aider les médecins à faire le diagnostic, semble indispensable en raison du grand nombre de patients dans les unités de soins intensifs et de la nécessité d'une observation continue. C'est ainsi qu'apparu plusieurs systèmes automatiques d'aide au diagnostic cardiaque à travers le signal ECG. Ces systèmes devraient être facilement applicables, évolutifs, précis, robustes, et stables. Le signal ECG et la traduction de signal électrique fondement du muscle cardiaque. L'acquisition du signal ECG indolore et non invasive, s'effectue à travers d'électrodes cutanées, convenablement réparties sur le corps humain, et sensible au potentiel électrique qui commande l'activité musculaire du cœur. Cette acquisition peut s'effectuer en milieu hospitalier ou bien de façon ambulatoire, le patient vaquant alors à ses activités quotidiennes. [17] [29][30].

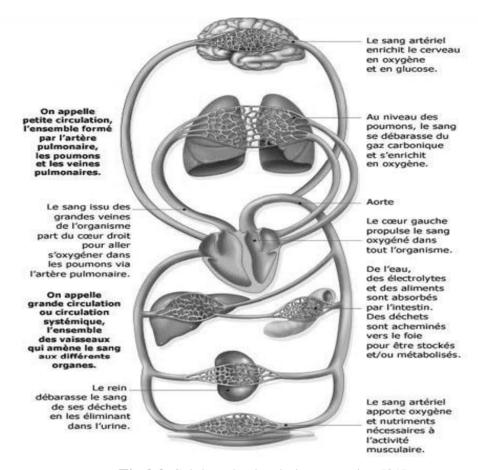

#### II.2 Système cardio-vasculaire

Le système cardio-vasculaire appelé aussi système circulatoire assure la circulation du sang d'une manière continue dans l'organisme. Il permet ainsi d'alimenter les tissus cellulaires en oxygène et en nutriments et d'évacuer les déchets vers les reins et le dioxyde de carbone vers les poumons. Ce système est composé d'un organe pompe, le cœur, et d'un réseau continu et fermé de conduits qui permettent le transport du sang, le système vasculaire (les veines et les artères).

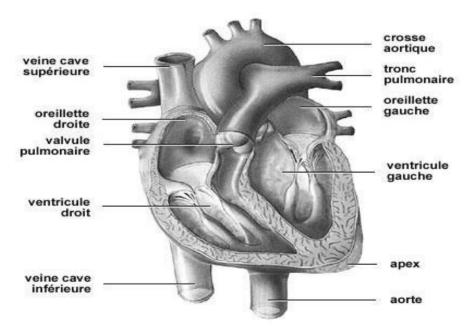

#### II.2.1 Cœur

Le cœur est un organe creux et musculaire comparable à une pompe, qui assure la circulation du sang dans les veines et les artères. Sa forme est similaire à un cône inversé (sa base vers le haut et à droite et son apex en bas et à gauche). Le cœur se situe dans le médiastin, c'est la partie médiane de la cage thoracique délimitée par les deux poumons, le sternum et la colonne vertébrale. Il se trouve un peu à gauche du centre du thorax. Le cœur pèse environ 300 grammes chez l'homme adulte, 250 grammes chez la femme. Il est capable de propulser, au repos, 4 à 5 litres de sang par minute figure 2.1.Le cœur est considéré comme une pompe musculaire subdivisée en quatre cavités : deux oreillettes et deux ventricules [31], permettant de propulser le sang vers toutes les cellules du corps humain. Les paires oreilletteventricule droite et gauche constituent respectivement les cœurs droit et gauche.

Fig.2.1. Schéma général du cœur [31]

#### **II.2.2** Circulation sanguine

L'oreillette droite récupère le sang pauvre en oxygène des veines caves supérieures et inférieure, et le propulse après contraction vers le ventricule droit Cette phase est la systole auriculaire. Cette phase systolique est suivie d'une autre diastolique, permettant d'envoyer le sang dans les poumons à travers les artères pulmonaires. Le dioxyde de carbone véhiculé par ce sang sera évacué par les poumons vers l'extérieur du corps, et par la suite sera rechargé en oxygène. Le sang revient ensuite au cœur dans l'oreillette gauche, puis passe dans le ventricule gauche là où il est envoyé vers les organes dans le réseau artériel à travers l'aorte [32]. L'ensemble de ces étapes forme la circulation sanguine illustrée sur la figure 2.2.

#### II.3 L'électrophysiologie cardiaque

Le cœur est un organe automatique. Il possède en lui-même tous les éléments de son fonctionnement. Cet automatisme est lié au tissu nodal (système de conduction cardiaque très spécialisé). Le cœur se contracte parce qu'un stimulus (ou onde de dépolarisation) prend origine au niveau de la paroi postérieure de l'oreillette droite. Ce stimulus traverse d'abord les deux oreillettes puis passe par la suite aux ventricules. En effet, le cœur comporte un réseau intrinsèque de cellules conductrices qui produisent et propagent des impulsions électriques, ainsi que des cellules qui répondent à ces impulsions par une contraction. Pour mieux comprendre l'origine des phénomènes électriques et mécaniques du cœur, les propriétés électro-physiologiques de la cellule cardiaque seront discutées tout d'abord.

#### II.3.1. Propriétés électro-physiologiques des cellules cardiaques

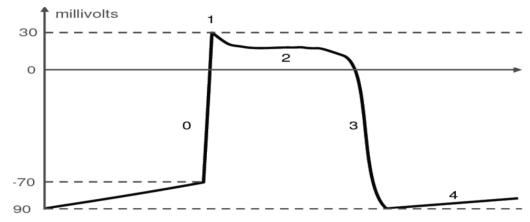

Les cellules cardiaques sont entourées d'une membrane qui permet le passage de différents ions, ce qui engendre des différences de concentration de part et d'autre de cette membrane cellulaire. Le sodium (Na+) est 10 fois plus concentré à l'extérieur qu'à l'intérieur de la membrane, par contre la concentration intracellulaire de potassium (K+) est 30 fois supérieure qu'à l'extérieur de la cellule et enfin le calcium (Ca++) est très concentré à l'extérieur par rapport a l'intérieur. Les différences de concentration de ces particules chargées électriquement aboutissent à des différences de potentiel entre l'intérieur et l'extérieur de la membrane cellulaire. Au repos, l'intérieur de la cellule est chargé négativement avec une différence de potentiel de -90mV ce qui est connu par le potentiel de repos. Lorsque la cellule est excitée par un stimulus électrique, mécanique ou chimique, des modifications transitoires de la membrane vont aboutir à une entrée brutale de sodium, suivie d'une entrée de calcium et d'une sortie de potassium. La différence de potentiel passe alors de -90mV à environ +20mV. C'est le potentiel d'action.

Lors de la contraction des cellules cardiaques, des échanges ioniques se déroulent et définissent ainsi le potentiel d'action, présenté sur la figure 3.3, qui comprend 5 phases successives :

Fig.2.2. Schéma de circulation sanguine [31]

La phase 0 ou dépolarisation rapide : après une excitation électrique au-dessus du seuil d'activation de la cellule, un afflux rapide d'ions Na+ rentre dans la cellule et inverse rapidement la polarité de la cellule.

La phase 1 ou début de repolarisation : elle est caractérisée par une repolarisation rapide et de courte durée, due à l'inactivation des canaux Na+ et au flux sortant d'ions de potassium K+.

La phase 2 ou plateau : elle correspond à la phase de repolarisation lente. Elle est due à l'entrée lente des ions Ca++ dans la cellule qui atténue l'influence des canaux K+ continuant à sortir, ralentissant ainsi la phase de repolarisation.

La phase 3 ou repolarisation : elle correspond à la phase de repolarisation finale, et se caractérise par la fermeture de canaux ioniques spécifiques qui ramène la cellule au potentiel de repos original. Durant cette phase, les ions K+ sont toujours sortants tandis que le potentiel de la cellule tend vers son seuil de repos.

La phase 4 : elle correspond au potentiel de repos, où la cellule est plus facilement excitable.

Dans un second temps les mécanismes servant à rétablir les différences de concentration vont se réactiver et rétablir les différences de concentration de part et d'autre de la membrane : c'est la phase de repolarisation de la cellule au cours de laquelle la cellule ne peut pas réagir à une nouvelle stimulation. C'est la période réfractaire.

Fig.2.3. Les cinq phases du potentiel d'action d'une cellule du muscle myocardique.

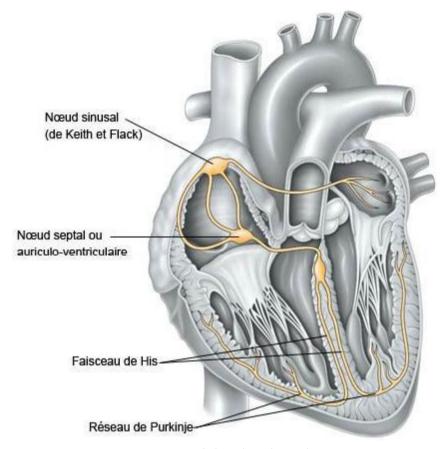

#### II.3.2. Fonctionnement électrique du cœur

Le cœur comprend un système de conduction électrique automatique qui assure chacun de ses battements. La contraction du muscle cardiaque est régie par une impulsion électrique qui prend sa naissance dans le nœud sinusal (ou de Keith et Flack) situé au niveau de la veine cave supérieure, dans l'oreillette droite comme illustré dans la figure 2.4. Ce nœud est constitué d'un ensemble de cellules auto-excitables qui génère un courant de dépolarisation 60 à 100 fois par minute. Ce nœud est considéré comme le "pacemaker" du cycle cardiaque. Cette excitation électrique se propage dans les deux oreillettes induisant la systole auriculaire et arrive au nœud auriculo-ventriculaire (ou d'Achoff-Tawara) seul point de passage entre les oreillettes et les ventricules situé dans le septum inter-ventriculaire (figure 2.4).

A ce niveau, l'excitation électrique marque une courte pause avant de passer au faisceau de His et par suite au réseau de Purkinje induisant la systole ventriculaire. Cette pause est très importante pour permettre une stimulation retardée par rapport aux oreillettes ce qui permet aux ventricules d'être complètement remplis au moment de la contraction auriculaire (illustré dans la figure 2.4). Ce système électrique explique la régularité du rythme cardiaque et assure la coordination des contractions auriculo-ventriculaires.

#### II.4. L'électrocardiographie

L'électrocardiographie est une technique relativement peu coûteuse permettant, à l'aide d'un simple examen et sans danger, de surveiller le bon fonctionnement de l'appareil cardiovasculaire. Cette technique est née pour la première fois en 1887 avec les travaux de Waller [34], elle est révélée à la communauté médicale par l'invention en 1901 du galvanomètre à cordes [35] [36], et qui a valut à son auteur, le Dr. Wilhem Einthoven, le prix Nobel de Médecine en 1924 [37]. Par la suite, l'électrocardiographie est devenue une technique incontournable et primordiale dans le domaine de cardiologie.

Le corps humain est considéré comme électriquement conducteur. Par conséquent, les potentiels d'actions générés au niveau des fibres cardiaques lors de l'activité mécanique cardiaque peuvent être recueillis par des électrodes métalliques placées sur la surface de la

Fig.2.4. L'activité électrique du cœur [31]

peau. L'enregistrement graphique de cette activité électrique du cœur est appelé signal électrocardiogramme ECG. Les positions des électrodes utilisées pour le recueil du signal ECG sont connues par dérivations électrocardiographiques. L'ECG standard est enregistré sur 12 dérivations (six dérivations périphériques et six précordiales).

#### II.4.1. Système de Dérivations électrocardiographiques

La dérivation en électrocardiographie se définie par deux points d'observation de l'activité électrique du cœur à partir desquels on mesure une différence de potentiel électrique.

Généralement les appareils électrocardiographiques peuvent enregistrer plusieurs différences de potentiels en même temps selon l'emplacement et le nombre d'électrodes réparties sur le corps. Chaque mesure de ces potentiels correspond alors à une dérivation de l'ECG. L'emplacement de ces électrodes est choisi de manière à explorer la quasi-totalité du champ électrique cardiaque résultant de la contraction du myocarde.

#### II.4.1.1. Dérivations périphériques

Les dérivations périphériques (ou dérivations des membres) permettent d'étudier l'activité électrique du cœur sur le plan frontal. Elles sont obtenues au moyen de 4 électrodes appliquées au bras droit, au bras gauche et à la jambe gauche, l'électrode de la jambe droite étant une électrode neutre destinée à éliminer les parasites électriques. Elles ont été déterminées par Einthoven en 1912 (Les dérivations périphériques bipolaires) et complétées par Goldberger en 1942 (Les dérivations périphériques unipolaires).

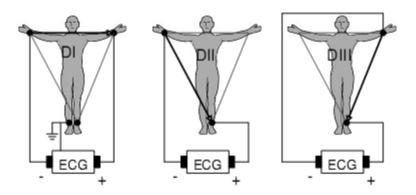

#### II.4.1.1.1 Dérivations périphériques bipolaires

Les dérivations bipolaires (DI, DII, DIII) ont été déterminées par Einthoven [38] au début du vingtième siècle et restent encore utilisées aujourd'hui. Ces dérivations utilisent trois électrodes placées sur le sujet. Les électrodes sont placées sur les bras droit et gauche et sur la jambe gauche pour former un triangle (triangle d'Einthoven).

Ces dérivations sont dites bipolaires parce qu'elles mesurent une différence de potentiel entre deux électrodes. Chaque côté du triangle formé par les trois électrodes représente une dérivation en utilisant une paire d'électrodes différente pour chacune des dérivations (voir figure 2.5).

Les trois dérivations sont :

- ➤ DI (dérivation I) avec DI = VL –VR

- ➤ DII (dérivation II) avec DII = VF VR

- ➤ DIII (dérivation III) avec DIII = VF VL

Avec : VL le potentiel sur le bras gauche

VR le potentiel sur le bras droit

VF le potentiel sur la jambe gauche

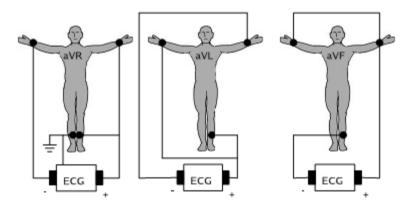

#### II.4.1.1.2. Dérivations périphériques unipolaires

Les dérivations unipolaires ont été introduites par Wilson. Dans son système, les dérivations sont obtenues entre une électrode exploratrice placée au sommet du triangle d'Einthoven et une borne centrale (électrode neutre ou indifférente, dont le potentiel est la moyenne des potentiels des trois sommets du triangle d'Einthoven). Cela a donné les dérivations unipolaires VL VR et VF. Plus tard, Goldberg [39] a modifié le système des

dérivations de Wilson pour obtenir trois dérivations unipolaires augmentées, appelées aVL aVR et aVF (illustré dans la figure 2.6). La lettre a (de l'anglais augmented) désigne le fait que les nouvelles dérivations amplifient les variations de potentiel des dérivations de Wilson par un facteur de 1,5.

Fig. 2.5 Montage d'Einthoven pour l'enregistrement des dérivations bipolaires des membres.

**Fig. 2.6** Montage de Goldberger pour l'enregistrement des dérivations unipolaires des membres.

#### II.4.1.2. Dérivations précordiales

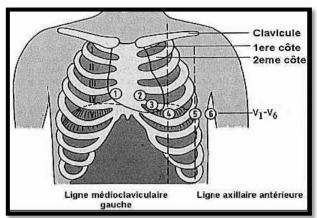

Pour mesurer les potentiels proches du cœur, Wilson a introduit les dérivations du plan horizontal V1, V2, V3, V4, V5, et V6. Ces six dérivations sont localisées du côté gauche du thorax comme illustré dans la figure 2.7. Les potentiels sont enregistrés à partir d'une électrode exploratrice (pôle positif) placée sur le thorax et l'électrode de référence (pôle négatif) connectée à la borne centrale de Wilson. Ce sont des dérivations rapprochées car l'électrode exploratrice est placée à faible distance des parois du ventricule droit et gauche.

# II.4.1.2.1. Position des électrodes précordiales

- ➤ V1: 4ème espace intercostal, bord droit du sternum (ligne parasternale)

- ➤ V2: 4ème espace intercostal, bord gauche du sternum (ligne parasternale)

- > V3: à mi-distance entre V2 et V4

- ➤ V4: 5ème espace intercostal, ligne médio-claviculaire gauche

- ➤ V5: à mi-distance entre V4 et V6, sur la ligne axillaire antérieure

- ➤ V6: même niveau horizontal que V4 et V5, ligne axillaire moyenne

Fig.2.7 la position des électrodes précordiales

# II.4.2. Signal électrocardiogramme

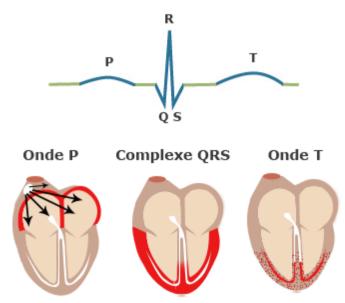

Comme introduit auparavant, l'électrocardiogramme ECG est obtenu à partir d'un appareil, l'électrocardiographe, qui enregistre l'activité mécanique du cœur sous forme d'un signal électrique. Ce signal électro-physiologique est recueilli par l'intermédiaire des électrodes métalliques bien placées sur la surface de la peau. L'information enregistrée dans l'ECG se présente comme une série d'ondes électriques, aux formes et durées particulières qui se répètent à chaque cycle cardiaque. En réalité ces ondes traduisent les différents phénomènes mécaniques relatifs au parcours du potentiel d'action de la stimulation cardiaque et dont les étapes sont successives comme illustré dans la Figure 2.8.

**Fig. 2.8** Étapes successives de dépolarisation/repolarisation du cœur qui se traduisent sur le plan électrocardiographique par différentes ondes P, QRS, et T.

# II.4.2.1. Ondes enregistrées sur un ECG normal

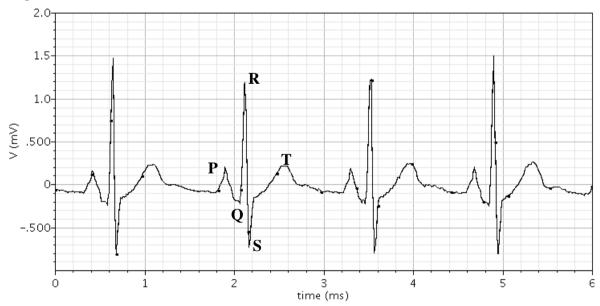

La figure III.9 montre la morphologie du signal ECG normal sur un cycle cardiaque.

**Fig. 2.9** Étapes successives de dépolarisation/repolarisation du cœur qui se traduisent sur le plan électrocardiographique par différentes ondes P, QRS, et T.

On observe dans un signal électrocardiographique ECG que le processus de contraction et de décontraction du myocarde se présentent comme une séquence de déflexions positives et négatives superposées à une ligne de potentiel zéro (ligne de base) qui correspond à l'absence des phénomènes cardiaques comme illustré dans la Figure 2.9. Par convention, on attribue aux ondes principales de l'ECG les lettres P, Q, R, S, T et U :

#### L'onde P:

C'est la première onde détectable. Elle apparaît quand l'impulsion électrique se propage à partir du nœud sinusal pour dépolariser les oreillettes (voir Figure 2.8). Sa masse musculaire relativement faible entraîne une variation de potentiel faible (moins de 0.25 mv). La progression de l'onde de dépolarisation dans les oreillettes est beaucoup plus lente que dans les ventricules. Par conséquent, la région des oreillettes autour du nœud sinusal est dépolarisée très en avance par rapport aux régions plus éloignées. Puis, le front de repolarisation prend le même sens que celui de la dépolarisation et le vecteur résultant instantané est orienté vers le nœud sinusal. Cela produit une onde de repolarisation à l'inverse de l'onde de dépolarisation P. Normalement, l'onde de repolarisation des oreillettes apparaît au moment où le complexe QRS est produit. Comme ce signal est beaucoup plus intense que le premier, l'onde de repolarisation est cachée.

# Le complexe QRS:

C'est un ensemble de déflexions positives et négatives qui correspondent à la contraction des ventricules. Pour un cas normal, il a une durée inférieure à 0.12 seconde et son amplitude variable est comprise entre 5 et 20 mV.

Il est constitué de trois ondes :

- L'onde Q : première déflexion négative

- L'onde R : première déflexion positive

- L'onde S : défection négative qui suit l'onde R

Sa forme est variable selon les dérivations utilisées (emplacement des électrodes) ou une arythmie donnée.

#### L'onde T:

Elle correspond à la repolarisation ventriculaire. Elle est normalement de faible amplitude et ne témoigne d'aucun événement mécanique. Cette onde succède au complexe QRS après retour à la ligne isoélectrique.

#### L'onde U:

Dans certaines occasions, une onde, dite onde U, peut être observée après l'onde T. C'est une onde de faible amplitude et elle est visible dans certaines dérivations notamment chez les athlètes. L'onde U est souvent associée aux processus de repolarisation ventriculaire tardive, mais le mécanisme de sa genèse est encore discuté

En général, un tracé d'un électrocardiogramme normal se présente comme illustré dans la figure.2.9. La caractérisation d'un ECG concerne les durées, les amplitudes et la morphologie des ondes P, QRS et T ainsi que d'autre paramètres temporels qui sont les segments PR et ST, et les intervalles PR, QT et ST.

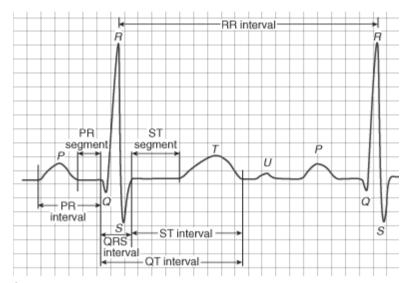

# II.4.2.2. Segments et intervalles qui caractérisent un ECG normal

En plus des différentes ondes qui sont les paramètres de base pour une bonne caractérisation d'un signal ECG, il existe un certain nombre d'intervalles et de segments qui portent des informations très utiles sur la vitesse de conduction de l'impulsion électrique dans les différentes parties du cœur.

Les intervalles et les segments les plus importants sont :

#### **Intervalle RR:**

L'intervalle RR correspond au délai entre deux dépolarisations des ventricules. C'est cet intervalle qui permet de calculer la fréquence cardiaque.

**Segment PR**: (pause du nœud AV)

Le segment PR correspond au délai entre la fin de la dépolarisation des oreillettes et le début de celle des ventricules. C'est le temps pendant lequel l'onde de dépolarisation est bloquée au niveau du nœud AV.

**Intervalle PR**: (durée de conduction auriculo-ventriculaire)

L'intervalle PR correspond à la durée de propagation de l'onde de dépolarisation du nœud sinusal jusqu'aux cellules myocardiques ventriculaires.

**Intervalle QT :** (durée de systole ventriculaire)

Cet intervalle correspond au temps de systole ventriculaire, qui va du début de l'excitation des ventricules jusqu'à la fin de leur relaxation.

**Segment ST :** (durée de stimulation complète des ventricules)

Le segment ST correspond à la phase pendant laquelle les cellules ventriculaires sont toutes dépolarisées, le segment est alors isoélectrique.

Une présentation détaillée des caractéristiques de l'ECG normal, leur interprétation physiologique ainsi que plusieurs méthodes de calcul de l'axe électrique du complexe QRS peut être trouvée dans [40][41][42]

# II.4.3 Le rythme cardiaque

Le rythme cardiaque est en relation à la fois du lieu de genèse de l'activité électrique du cœur et de la régularité ou non de sa propagation. Ainsi, on parle de rythme sinusal régulier lorsqu'il est :

- régulier : l'intervalle R-R est quasi-constant sur tout le tracé, avec des complexes QRS similaires

- sinusal : l'activité électrique est générée par le nœud sinusal. L'analyse du rythme cardiaque à partir du signal électrocardiogramme est accomplie par la vérification de la régularité du rythme et de son origine qui peut être :

- 1. Sinusal (du nœud sinusal : une onde P précède chaque complexe QRS)

- Jonctionnel (du nœud auriculo-ventriculaire : complexes QRS fins et onde P rétrograde)

- 3. Ventriculaire (myocytes ventriculaires : complexe QRS élargi et sans onde P)

- 4. Ectopique (issu des cellules musculaires auriculaires : onde P anormale et complexe QRS normal)

- 5. Artificiel (pacemaker)

Dans le cas du pacemaker, le rythme cardiaque est imposé par un stimulateur cardiaque implanté au voisinage du cœur.

#### II.5 Interférence

Il est à prévoir que n'importe quel système de reconnaissance ECG devra fonctionner dans un environnement hospitalier bruyant. Le signal ECG est normalement corrompu avec différents types de bruit. Souvent les informations ne peuvent pas être facilement extraites du signal brut, qui doit être traité en premier pour obtenir un résultat utile. Il existe de nombreuses sources de bruit dans un environnement clinique qui peut dégrader le signal ECG. Les sources communes de bruit pour le signal ECG sont [43][44] [45][46].

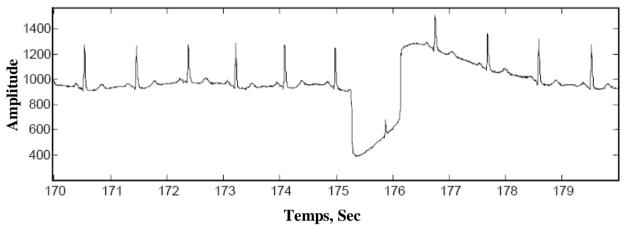

#### II.5.1. Interférences dues à l'alimentation (60 ou 50 Hz)

Le bruit 50Hz (60Hz) est un bruit qui provient de l'alimentation par le réseau de distribution électrique. Il contamine le signal électrocardiographique ECG avec des oscillations dont l'harmonique fondamentale est à 50 Hz (60Hz). Généralement, ce bruit est présent dans tous les enregistrements et il peut être assez fort, Généralement, ce type de bruit est supprimé en moyennant un filtre passe-bas du fait qu'il est un bruit de haute fréquence. Ce type de bruit est illustré dans la figure 2.10.

Fig.2.10 Interférences électriques du secteur.

# II.5.2. Interférences dues à l'activité électrique musculaire

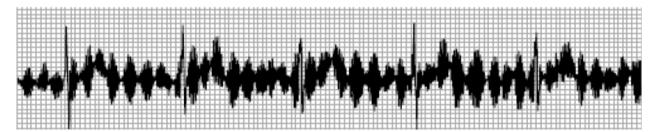

Ces bruits sont généralement causés par l'activité électrique due aux muscles en contraction. Ces oscillations de hautes fréquences sur le tracé de l'ECG, la Figure. 2.11, apparaîtront lorsque le patient bouge ou frissonne. Leur présence est très endommageant du fait qu'ils puissent noyer les différentes ondes du signal ECG et nuire ainsi à l'information utile.

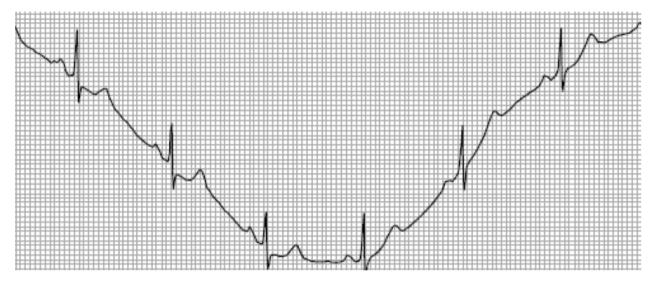

#### II.5.3. Dérive de la ligne de base

La dérive de la ligne de base est due essentiellement à la respiration du patient, Figure. 2.12. L'énergie spectrale des oscillations de ce bruit est située aux basses fréquences. Leur présence ne représente pas un grand problème et leur suppression est assurée par des filtres simples de type passe-haut.

Fig.2.11 Interférences dus aux activités électriques musculaires.

Fig.2.12 Dérive de la ligne de base du signal ECG.

#### II.5.4 Interférences dues au mauvais contact électrode-peau

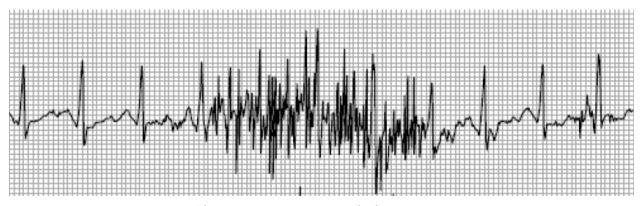

Lorsque les électrodes utilisées pour le recueil du signal ECG se détachent ou le gel entre l'électrode et la peau se sèche, cela peut provoquer un bruit qui provoque des changements brusques de l'amplitude du signal d'ECG (Figure 2.13) ainsi que de faibles changements de fréquence de référence.

De plus, une mauvaise conductivité entre les électrodes et la peau peut avoir un effet sur le signal EGC qui peut aller d'une simple diminution d'amplitude à l'apparition des pics qui peuvent parfois être confondus avec les ondes du tracé normal. Ce type de bruit est difficile à éliminer car son énergie se trouve dans la même gamme de fréquence que celle des complexes QRS.

#### II.5.5 Interférences d'instrumentation

Ces Interférences générée par des dispositifs électroniques utilisés dans le traitement du signal, ils affectent chaque composant d'un appareil, à savoir la source, le transducteur

d'entrée, les systèmes de traitement du signal et le transducteur de sortie. De plus, le bruit de chacun de ces éléments peut être de plusieurs types et résulter de causes variées. Par conséquent, les composantes du bruit observé sont complexes et difficiles à caractériser de manière complète. Certaines espaces de bruit instrumental néanmoins caractéristiques : (1) le bruit thermique, (2) le bruit de grenaille, (3) le bruit de scintillation ou bruit en 1/f......

Fig.2.13 Bruit dû au mauvais contact électrode-peau

#### **II.6 Conclusion**

Malgré une forte évolution technologique dans le domaine de l'instrumentation médicale, l'électrocardiographie reste un examen indispensable en cardiologie depuis de longues années. Cette technique permet de faire un monitorage de l'activité électrique du myocarde depuis l'extérieur du corps. Ceci est achevé par l'utilisation des électrodes collées à la surface de la peau pour récupérer un signal sous forme électrique appelé signal électrocardiogramme ECG. L'étude menée dans ce deuxième chapitre sur l'anatomie cardiaque ainsi que les propriétés électro-physiologiques des cellules cardiaques ont permis de mieux comprendre la nature et l'origine du signal ECG.

Nous avons aussi présenté certains types des bruits affectant le signal ECG et qui peuvent constituer des obstacles devant l'exploitation adéquate de ce signal.

# **Chapitre III**

# Cellules analogiques

| TTT  | 1 T  |      | 1   | , •  |    |

|------|------|------|-----|------|----|

| III. | I II | ntro | 111 | CTIO | n  |

| 111. |      | uu   | u   | cuv  | 11 |

- III.2 Techniques de conception basse tension en technologie CMOS

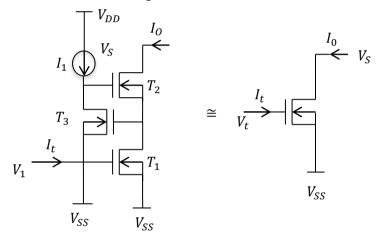

- III.2.1 Transistor composite

- III.2.2 Latéral BJT

- III.2.3 Polarisation direct Bulk-Source

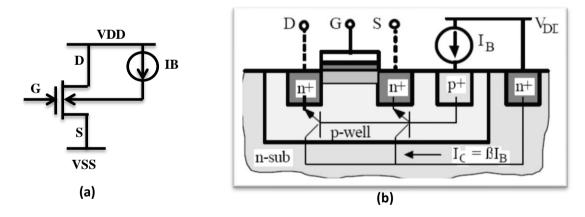

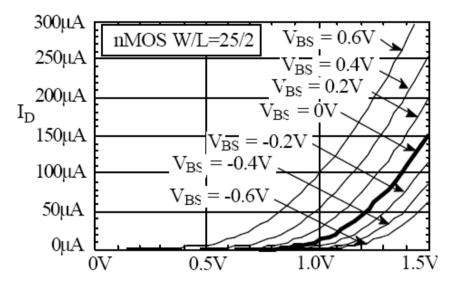

- III.2.4 Bulk-Driven MOSFET

- III.3 Limitations de circuits en inversion forte travaillé avec alimentation basse tension

- III.4 Technologie CMOS 90nm GPDK

- III.5 Régimes de transistor MOSFET

- III.5.1 Courant de drain en régime ohmique

- III.5.2.Courant de drain en régime de saturation

- III.6 Bruit électrique Basse Fréquence dans le transistor MOSFET

- III.6.1 Bruit thermique

- III.6.2.Bruit en 1/f

- III.7 Circuit portative pour le signal ECG

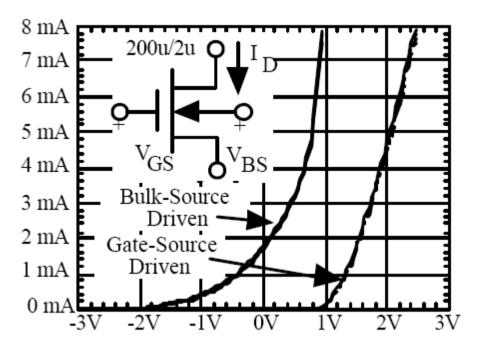

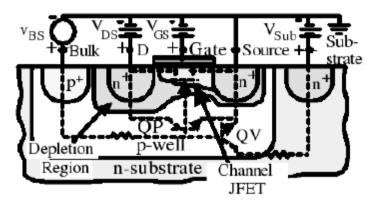

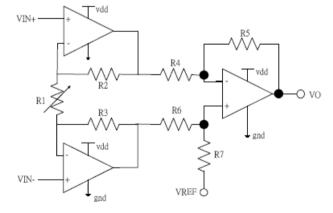

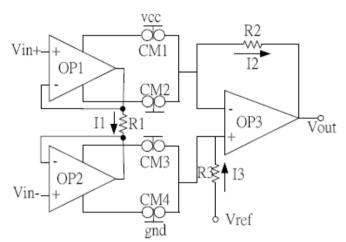

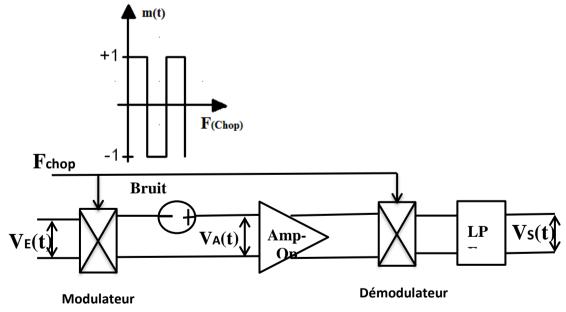

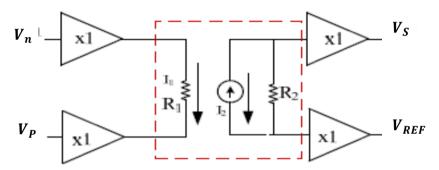

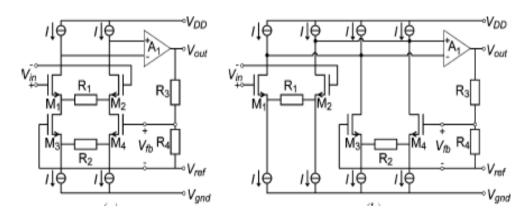

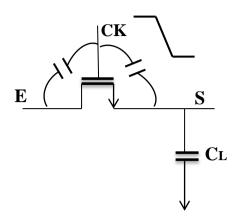

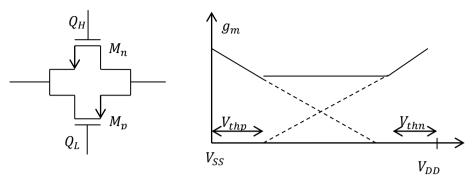

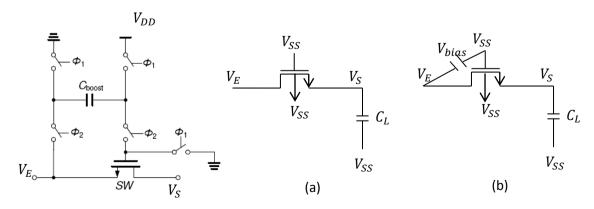

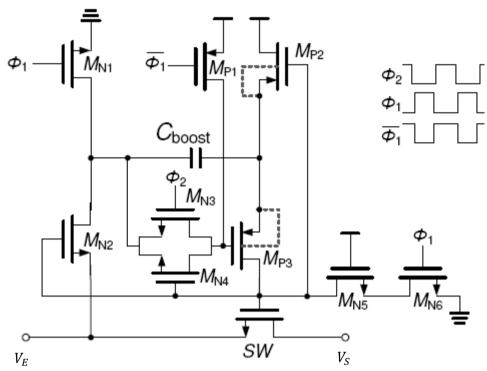

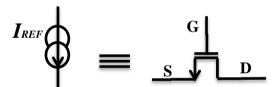

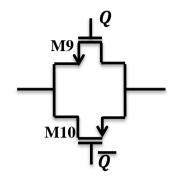

- III.7.1 Amplificateur opérationnel d'instrumentation