# REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

# UNIVERSITE DE BATNA FACULTE DE TECHNOLOGIE DEPARTEMENT D'ELECTRONIQUE

#### Mémoire

Présenté en vue de l'obtention du diplôme de Magister en Électronique

# **Option**

Micro-électronique IC-Design

# **Présenté par** YOUSFI Abderrahim

#### **THEME**

# Étude et modélisation de l'effet de la grille sur les performances électriques du transistor nanométrique à grille enrobée

# Devant le jury constitué de :

| Pr. MAHAMDI Ramdane  | Prof. Univ. Batna | Président   |

|----------------------|-------------------|-------------|

| Dr. DJEFFAL Fayçal   | M.C.A Univ. Batna | Rapporteur  |

| Dr. BOURIDAH Hachemi | M.C.A Univ. Jijel | Examinateur |

| Pr. DIBI Zohir       | Prof. Univ. Batna | Examinateur |

#### Remerciements

Je souhaite remercier ici un certain nombre de personnes qui ont contribué à l'aboutissement de ce travail de mémoire de Magister.

Un premier merci à mon directeur du mémoire **DJEFFAL Fayçal** qui par ses encouragements, son positivisme et sa franchise a su m'accompagner lors de ces deux années. Son aide permanent et son soutien m'ont permis de mener à bien cette recherche. Ce fut un plaisir de travailler avec lui.

J'exprime ma profonde et respectueuse gratitude à Monsieur MAHAMDI Ramdane professeur à l'Université de Batna pour m'avoir fait l'honneur d'accepté la présidence du jury de soutenance.

J'adresse mes sincères remerciements à Monsieur **BOURIDAH Hachemi** Maître de Conférence à l'Université de **Jijel** pour m'avoir fait l'honneur de juger cette thèse.

Mes remerciements s'adressent également à Monsieur **DIBI Zohir**, professeur à l'Université de **Batna**, qui m'honore de sa présence dans ce jury.

Je remercie enfin tous les membres du laboratoire de la Poste graduation d'électronique ainsi que tous ceux qui ont participé de prés ou de loin à la réalisation de ce travail.

#### Je dédie ce travail à :.

# A Mon Père,

En vous, je voie un père dévoué à sa famille.Ta présence en toute

circonstance m'a maintes fois rappelé

le sens de la responsabilité.

# A Ma Mère,

En vous, je voie la maman parfaite, toujours prête à se sacrifier pour le bonheur de ses enfants.

A Toute ma famille et tous mes collègues.

Merci pour tout.

# Table des notations

| $\mathcal{E}_{ox}$ | La permittivité électrique de l'oxyde             |

|--------------------|---------------------------------------------------|

|                    | La permittivité électrique du silicium            |

| $\mathcal{E}_{si}$ |                                                   |

| μ                  | Mobilité de porteurs dans le canal                |

| $t_{si}$           | épaisseur du Silicium                             |

| $t_{ox}$           | épaisseur de l'oxyde de grille (SiO2)             |

| $\psi_s$           | Le potentiel de surface                           |

| $\mu_n$            | Mobilité des électrons                            |

| $\mu_p$            | Mobilité des trous                                |

| q                  | Charge élémentaire électrostatique                |

| $c_{ox}$           | Capacité d'oxyde                                  |

| CMOS               | Complementary Metal-Oxide-Semiconductor           |

| MOSFET             | Metal-Oxide-Semiconductor Field Effect Transistor |

| DG MOSFET          | Double Gate MOSFET                                |

| GAA MOSFET         | Gate All Around MOSFET                            |

| nMOSFET            | Transistor à canal n                              |

| pMOSFET            | Transistor à canal p                              |

| L                  | Longueur du canal                                 |

| $N_A$              | Concentration en dopants de type P                |

| $N_D$              | Concentration en dopants de type N                |

| $n_i$              | Densité de porteur intrinsèque                    |

| T                  | Température                                       |

| Si                 | Silicium                                          |

| $SiO_2$            | Oxyde de silicium (isolant)                       |

| $V_{ds}$           | Tension Drain-Source                              |

| $V_{gs}$           | Tension grille-Source                             |

| $V_{g}$            | Polarisation de grille normalisée                      |

|--------------------|--------------------------------------------------------|

| $oldsymbol{V_g^*}$ | Représente la tension de la grille normalisée          |

| $V_{bi}$           | Potentiel aux jonctions source/drain-canal normalisé   |

| $V_{th}$           | Tension de seuil                                       |

| VLSI               | Intégration à très grande échelle                      |

| ZCE                | Zone de charge d'espace                                |

| x                  | Affinité électronique                                  |

| $X_{si}$           | Affinité électronique du silicium                      |

| $\phi_{ms}$        | Différence des travaux de sortie métal-semi-conducteur |

| ECC                | Effet Canaux Courts                                    |

# **Constantes fondamentales**

| Constante de Planck                           | h                            | $=6.62618.10^{-34} Js$     |

|-----------------------------------------------|------------------------------|----------------------------|

| Module de la charge élémentaire de l'électron | e                            | $=1.602189.10^{-19}C$      |

| Permittivité diélectrique du vide             | $\boldsymbol{\mathcal{E}}_0$ | $=8.854.10^{-12}  F  /  m$ |

| Energie du Gap à 300K                         | $E_g$                        | = 1.12 eV                  |

| Affinité électronique                         | $x_{si}$                     | = 4.01 eV                  |

| Permittivité relative                         | $\mathcal{E}_{si}$           | = 11.9                     |

# **Table des Matières**

| Introdu                                            | ıction générale                                                                                                                                                                                                                             | 1                                      |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Chapitre I                                         | TECHNOLOGIE DU TRANSISTOR                                                                                                                                                                                                                   |                                        |

| I                                                  | Introduction                                                                                                                                                                                                                                | 4                                      |

| I.1                                                | L'ère du transistor MOS                                                                                                                                                                                                                     | 5                                      |

| I.2                                                | Transistor MOS                                                                                                                                                                                                                              | 6                                      |

| I.3                                                | Principe de fonctionnement du MOSFET                                                                                                                                                                                                        | 8                                      |

| I.3.1                                              | Régimes de fonctionnement du transistor MOSFET                                                                                                                                                                                              | 9                                      |

| I.4                                                | Quelles applications.                                                                                                                                                                                                                       | 12                                     |

| I.5                                                | Miniaturisation des transistors                                                                                                                                                                                                             | 13                                     |

| I.5.1                                              | Pourquoi réduire la taille des transistors                                                                                                                                                                                                  | 13                                     |

| I.6                                                | Effets canaux courts                                                                                                                                                                                                                        | 14                                     |

| I.6.1                                              | Partage de charge de déplétion (CS)                                                                                                                                                                                                         | 14                                     |

| I.6.2                                              | DIBL (abaissement de la barrière de potentiel induit par le drain)                                                                                                                                                                          | 14                                     |

| I.6.3                                              | Courant sous seuil                                                                                                                                                                                                                          | 16                                     |

| I.6.4                                              | Tension de seuil                                                                                                                                                                                                                            | 18                                     |

| I.7                                                | Modélisation de l'effet de High-k (HfO2)                                                                                                                                                                                                    | 18                                     |

| I.8                                                | Conclusion                                                                                                                                                                                                                                  | 20                                     |

|                                                    |                                                                                                                                                                                                                                             |                                        |

| Chapitre II                                        | TRANSISTOR A GRILLE MULTIPLE                                                                                                                                                                                                                |                                        |

| II                                                 | Introduction                                                                                                                                                                                                                                | 22                                     |

| II.1                                               | Construction du MOSFET                                                                                                                                                                                                                      | 23                                     |

| II.1.1                                             | matériau de grille                                                                                                                                                                                                                          | 23                                     |

| II.1.2                                             | Grilles métalliques                                                                                                                                                                                                                         | 24                                     |

| II.1.3                                             | Déplétion de grille                                                                                                                                                                                                                         | 24                                     |

| II.1.3.1                                           | Amélioration du contrôle de la grille sur la charge de déplétion                                                                                                                                                                            | 25                                     |

| II.2                                               | Déférents structure du transistor                                                                                                                                                                                                           | 25                                     |

| II.2.1                                             | Structure double grille                                                                                                                                                                                                                     | 25                                     |

| II.2.2                                             | Structure triple grille                                                                                                                                                                                                                     | 26                                     |

| II.2.3                                             | Structure triple + grille                                                                                                                                                                                                                   | 27                                     |

| II.2.4                                             | Structure quadruple grille                                                                                                                                                                                                                  | 27                                     |

| 11.2.7                                             | Structure quadruple grine                                                                                                                                                                                                                   | 41                                     |

| II.3                                               | Structure quadruple grille  Transistors à grille enrobée                                                                                                                                                                                    | 28                                     |

|                                                    | Transistors à grille enrobée.  L'architecture MOSFET à grille enrobée.                                                                                                                                                                      |                                        |

| II.3                                               | Transistors à grille enrobée                                                                                                                                                                                                                | 28                                     |

| II.3<br>II.4                                       | Transistors à grille enrobée                                                                                                                                                                                                                | 28<br>30                               |

| II.3<br>II.4<br>II.5                               | Transistors à grille enrobée  L'architecture MOSFET à grille enrobée  Différentes catégories de la technologie GAA MOSFET                                                                                                                   | 28<br>30<br>32                         |

| II.3<br>II.4<br>II.5<br>II.5.1                     | Transistors à grille enrobée  L'architecture MOSFET à grille enrobée  Différentes catégories de la technologie GAA MOSFET  Transistor GAA MOSFET rectangulaire                                                                              | 28<br>30<br>32<br>32                   |

| II.3<br>II.4<br>II.5<br>II.5.1<br>II.5.2           | Transistors à grille enrobée  L'architecture MOSFET à grille enrobée  Différentes catégories de la technologie GAA MOSFET  Transistor GAA MOSFET rectangulaire  Transistor GAA MOSFET triangulaire                                          | 28<br>30<br>32<br>32<br>32<br>32       |

| II.3<br>II.4<br>II.5<br>II.5.1<br>II.5.2<br>II.5.3 | Transistors à grille enrobée.  L'architecture MOSFET à grille enrobée.  Différentes catégories de la technologie GAA MOSFET.  Transistor GAA MOSFET rectangulaire.  Transistor GAA MOSFET triangulaire.  Transistor GAA MOSFET cylindrique. | 28<br>30<br>32<br>32<br>32<br>32<br>32 |

| Chapitre III     | ALGORITHMES GENETIQUES                                |            |

|------------------|-------------------------------------------------------|------------|

| III              | Introduction                                          | 35         |

| III.1            | Algorithmes évolutionnaires                           | 36         |

| III.1.1          | Algorithmes génétiques (AGs)                          | 36         |

| III.1.1.1        | Principe des algorithmes génétiques                   | 37         |

| III.1.1.2        | Caractéristiques des algorithmes génétiques           | 38         |

| III.1.1.3        | Codage                                                | 38         |

|                  | Codage binaire                                        | 38         |

|                  | Codage réel                                           | 38         |

|                  | Codage de Gray                                        | 39         |

| III.1.1.4        | Espace de recherche des solutions                     | 40         |

| III.1.1.5        | Fonction d'évaluation (fitness) et le hasard          | 40         |

| III.1.1.6        | Concepts et formalismes d'opérateurs génétiques       | 41         |

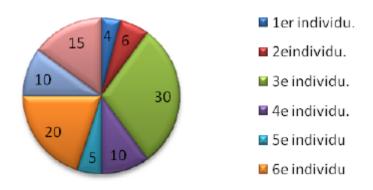

| III.1.1.6.a      | Sélection                                             | 41         |

|                  | Roulette                                              | 41         |

|                  | Tournoi                                               | 42         |

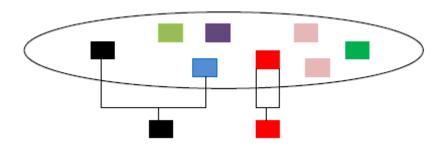

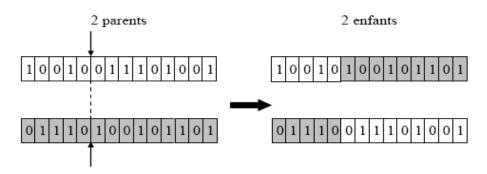

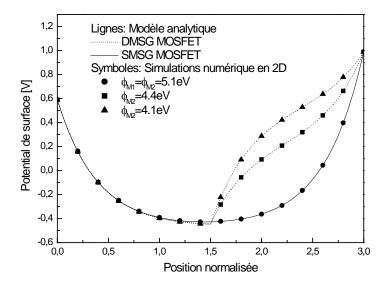

| III.1.1.6.b      | Croisement                                            | 42         |

| III.1.1.6.c      | Mutation                                              | 43         |

| III.1.1.6.d      | Elitisme                                              | 43         |

| III.1.1.7        | Critères de convergence                               | 44         |

| III.1.1.8        | Grandes étapes de l'algorithme génétique              | 44         |

| III.1.2          | Avantages et inconvénients des algorithmes génétiques | 45         |

| III.1.2.1        | Avantage des AGs                                      | 45         |

| III.1.2.2        | Inconvénients des AGs                                 | 45         |

| III.1.2.3        | Caractéristiques de l'optimisation génétique          | 46         |

| III.1.2.4        | Optimisation Multi objectifs                          | 46         |

| III.1.2.4.1      | Introduction                                          | 46         |

| III.2            | Conclusion.                                           | 48         |

| CI '4 TY         | MODELIGATION DU DINGC MOCEET NA NOMETRIQUE            |            |

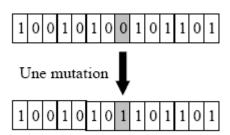

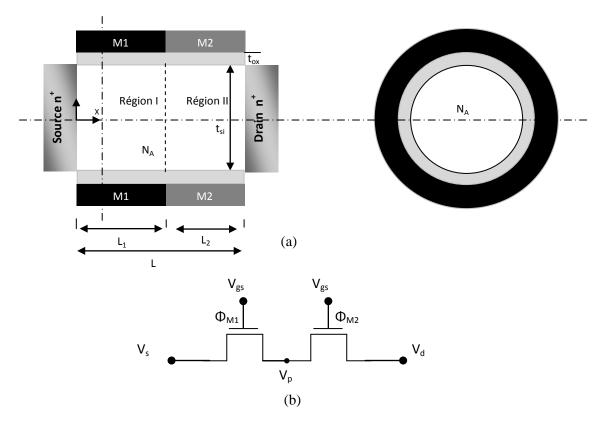

| Chapitre IV IV.1 | MODELISATION DU DMSG MOSFET NANOMETRIQUE Introduction | <i>5</i> 0 |

| IV.1             | Structure du transistor DMSG MOSFET                   | 50         |

| IV.2<br>IV.3     |                                                       | 51         |

| IV.3.1           | Modélisation analytique                               | 51         |

|                  | Potentiel de surface $\psi_s(x)$                      | 52         |

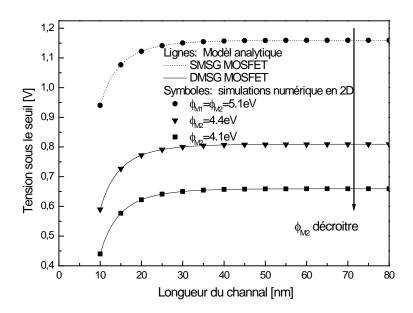

| IV.3.2           | Tension de seuil $V_{th}$ (Threshold voltage)         | 60         |

| IV.3.3           | Modélisation du <i>DIBL</i>                           | 62         |

| IV.3.4           | Facteur sous le seuil S                               | 64         |

| IV.4             | Conclusion.                                           | 66         |

| Cl               |                                                       |            |

| Chapitre V       | OPTEMISATION MULTI OBJECTIFS DU TRANSISTOR            | <b>CO</b>  |

| V.1              | Introduction                                          | 68         |

| V.2                 | Algorithme génétique multi objectifs (MOGA) | 77 |

|---------------------|---------------------------------------------|----|

| V.3                 | Optimisation basée sur MOGA                 | 78 |

| V.4                 | Conclusion.                                 | 73 |

| Conclusion générale |                                             | 75 |

# Introduction générale

Depuis les années 1950, le transistor à effet de champ MOSFET (Metal Oxyde Semi conductor Field Effect Transistor), en tant que brique de base des circuits intégrés, est le moteur principal de l'industrie du semi-conducteur. Son architecture et son principe de fonctionnement sont restés pratiquement inchangés à ce jour, mais ses dimensions physiques n'ont cessé de décroître, suivant la loi de Moore. Cependant, depuis le début des années 2000, la réduction de la taille des composants ne suffit plus à garantir de meilleures performances tout en réduisant le coût de fabrication. L'industrie des semi-conducteurs est dans une période clef de son développement, car elle passe du monde de la microélectronique à celui de la nanoélectronique. Afin de poursuivre l'augmentation des performances tout en maintenant l'architecture « classique » des transistors MOSFETs, plusieurs solutions existent. Entre autres, l'utilisation de substrats Silicium sur Isolant (SOI pour « Silicon-On-Insulator ») permet d'isoler électriquement la partie active des transistors (le canal de conduction) du substrat. L'incorporation d'une contrainte mécanique dans le canal est considérée comme la voie principale d'amélioration des MOSFETs, au même titre que la miniaturisation.

Les contraintes, si elles sont non intentionnelles, peuvent induire des défauts cristallins et notamment des dislocations pouvant générer des courants de fuite et des disfonctionnements importants des transistors. Par contre, leur contrôle permet d'augmenter la vitesse de fonctionnement des transistors. L'application de cette contrainte mécanique contrôlée ainsi que la compréhension de ses effets sur les propriétés physiques est ainsi l'un des enjeux de l'industrie des semi-conducteurs avec la réduction des dimensions des dispositifs. L'objectif de ce travail de thèse est de progresser dans la compréhension, la prévision et la quantification des effets canaux courts dans le transistor MOSFET.

Les algorithmes évolutionnistes ou algorithmes évolutionnaires, sont une famille d'algorithmes s'inspirant de la théorie de l'évolution pour résoudre des problèmes divers. Leur principe est de simuler l'évolution d'une population d'individus divers auquel on applique différents opérateurs génétiques et que l'on soumet à chaque génération à une sélection. Ces algorithmes sont de plus en plus utilisés dans l'industrie car ils sont particulièrement adaptés aux problèmes d'optimisation comportant de nombreux paramètres.

Le domaine de la modélisation et la simulation des composants microélectroniques peuvent être considéré comme un champ important d'applications des techniques évolutionnaires.

Par conséquent, l'étude de la possibilité d'utilisation de ces techniques dans le domaine de la microélectronique, notamment sous forme des optimisateurs et des simulateurs des composants microélectroniques, s'avère nécessaire. En ce sens, les techniques évolutionnaires sont considérées comme un outil supplémentaire entre les mains de l'ingénieur et du chercheur, plutôt que comme un substitut aux méthodes plus classiques. Ces outils sont susceptibles d'apporter des éléments de réponse là où les procédures analytiques montrent leurs limites.

# CHAPITRE 1 TECHNOLOGIE DU TRANSISTOR

#### I. Introduction

Ce premier chapitre présente le contexte de ces travaux de mémoire. En effet, le transistor MOS (Métal Oxyde Semi conducteur) à effet de champ (FET) atteint aujourd'hui des dimensions nanométriques. Dans une première partie, nous introduisons ce transistor MOS qui nous intéresse particulièrement. Nous verrons aussi dans une deuxième partie, qu'avec la diminution des dimensions, des effets parasites négligeables jusqu'à présent sont apparus. Pour pouvoir poursuivre cette miniaturisation sur les prochaines générations de transistor, il convient de développer de nouvelles architectures et introduire de nouveaux matériaux. C'est sur cet aspect, plus spécifique à l'objet de cette thèse.

#### I.1.L'ère du transistor MOS

De 1920 à nos jours Le transistor MOS, tirant son appellation de sa structure verticale (Métal/Oxyde/Semi-conducteur), est aujourd'hui la brique élémentaire des circuits intégrés constituant la plupart des dispositifs microélectroniques qui nous entourent. Aussi appelé transistor à effet de champ, MOSFET (MOS Field Effect Transistor), son principe de base fut énoncé pour la première fois dans les années 1920 par J. E. Lilienfield [1], mais il fallut attendre 1960 pour en voir la première réalisation [2] (Figure I.1).

L'échec des nombreuses tentatives provenait à l'époque de la difficulté à contrôler l'état d'interface entre l'isolant et le semi-conducteur du canal. C'est dans les années 1960, avec l'utilisation de l'oxyde de silicium thermique (SiO2), que les technologies CMOS (Complementary MOS) et planaires imposèrent le transistor MOS comme l'élément incontournable de la microélectronique.

Figure I.1: Premier transistorMOSFET réalisé par M. M. Atalla, D.Kahng et E. Labate en 1959[2]

En effet, la technologie CMOS consiste à associer 2 types de transistor MOS (nMOS et pMOS) en tirant partie de leur régime de fonctionnement complémentaire afin de former l'élément de base de tous les circuits logiques : l'inverseur. De plus, la technologie planaire permet de fortes densités d'intégration. Ainsi le premier processeur vit le jour chez INTEL en 1971, constitué de 2300 transistors nMOS de 10μm de longueur de grille et fonctionnant a une fréquence d'horloge de 108kHz.

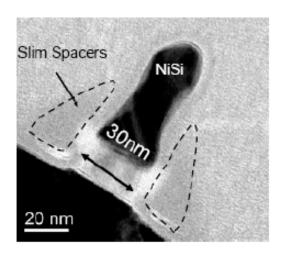

Aujourd'hui, les processeurs comportent 140 millions de transistors de 45nm de longueur de grille et fonctionnent à une fréquence d'horloge supérieure à 4GHz [3] (Figure I.2).

Figure I.2: Coupe TEM d'un transistor de longueur de grille 30nm[3]

#### **I.2 Transistor MOS**

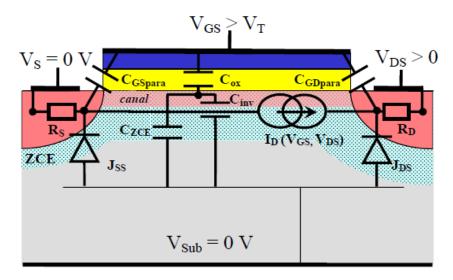

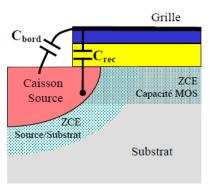

La figure (I.3) présente le schéma électrique équivalent d'un transistor MOSFET intrinsèque dans le régime d'inversion ( $V_{GS} \succ V_T$ ). Cette modélisation inclut les différentes résistances et capacités parasites habituelles. La superposition du schéma électrique et de la coupe du transistor met en évidence les origines physiques de ces éléments parasites [4]. Les caissons source et drain sont des zones fortement dopées, les porteurs qui les traversent y subissent donc un grand nombre d'interactions avec les impuretés dopantes ionisées. Les résistances d'accès intrinsèques  $R_S$  et  $R_D$  de ces caissons peuvent être non négligeables si elles deviennent du même ordre.

Figure I.3: Schéma électrique équivalent superposé à un schéma en coupe d'un MOSFET en inversion[4].

On a vu précédemment que l'effet de champ crée un canal de porteurs libres par l'intermédiaire de la capacité MOS. La longueur et la largeur de l'oxyde de grille étant très grandes devant son épaisseur (W et  $L_G \succ t_{OX}$ ), les effets de bord sont négligeables en première approximation.

La capacité MOS n'a donc qu'une seule dimension et on ne va considérer que des grandeurs surfaciques. La variation de charges surfaciques commandée par la grille  $\Delta Q(V_{GS})$  se repartit dans le semi-conducteur entre le canal d'inversion  $\Delta Q_{inv}$  et la zone de charge d'espace  $\Delta Q_{ZCE}$  soit :

$\Delta Q(V_{GS}) = \Delta Q_{inv} + \Delta Q_{ZCE}$ . Cette capacité MOS est modélisée par une capacité d'oxyde  $C_{ox}$  en série avec un montage en parallèle d'une capacité d'inversion  $C_{inv}$  et d'une capacité de substrat  $C_{ZCE}$ . La capacité surfacique d'oxyde  $C_{OX}$  est reliée à la structure métal de grille/isolant :  $C_{OX} = \varepsilon_{ox}/t_{ox}$ . La tension à ses bornes est égale à la différence de potentiel aux limites de l'oxyde. La capacité surfacique  $C_{inv}$  est liée à la variation, sous l'effet de la tension de grille, de la charge d'inversion formée par les porteurs libres du canal  $\Delta Q_{inv}$ . En outre, on montre que pour  $V_G \succ V_T$ , la charge surfacique d'inversion  $Q_{inv}$  est donnée par :

$$Q_{inv} = C_{ox}.(V_G - V_T).$$

La capacité surfacique  $C_{ZCE}$  correspond à la variation de charge surfacique de la zone de charge d'espace du substrat, d'extension  $T_{ZCE}$ , commandée par la grille donc  $C_{ZCE} = \varepsilon_{si} / T_{ZCE}$  avec  $\varepsilon_{si}$  permittivité diélectrique du silicium.

Pour augmenter le contrôle de la grille sur le canal,  $\Delta Q_{ZCE}$  et donc la capacité  $C_{ZCE}$  doit rester les plus faibles possibles pour ne pas dégrader les caractéristiques du transistor, en particulier sous le seuil.

Les capacités  $CGS_{para}$  et  $CGD_{para}$  modélisent des phénomènes capacitifs supplémentaires qui se rajoutent, côté drain et côté source, à ceux de la structure MOS idéale. Chacune de ces capacités peut inclure différents types de couplage électrostatique comme illustré en Figure (I.4). Tout d'abord, il peut exister un couplage dû à des effets de bord nommé  $C_{bord}$ : des lignes de champ (à 2 dimensions) se propagent entre l'électrode de grille et les caissons dans l'espace au-dessus des caissons. Dans le cas d'un recouvrement par la grille des caissons, il y a création, en régime d'inversion du canal, d'une zone d'accumulation dans les caissons et apparition de la capacité  $C_{recd}$  associée qui peut être très pénalisante. De plus, si la grille

recouvre les ZCE de jonction caisson/substrat, il y a compétition entre les ZCE commandées par la grille et la source. Cela se traduit par une modification de la capacité surfacique  $C_{\it ZCE}$  près des caissons.

Figure I.4: Décomposition de la capacité parasite  $CGS_{para}$  de la Figure I.3 en capacité  $C_{bord}$  et capacité de recouvrement  $C_{rec}$  grille/caisson[4].

Enfin, on constate la présence des jonctions N<sup>+</sup>/P Source/Substrat et aussi Drain/Substrat qui induisent des comportements résistifs et capacitifs susceptibles de détériorer aussi le comportement dynamique du transistor.

#### I.3 Principe de fonctionnement du MOSFET

Le principe de fonctionnement d'un transistor MOS repose sur "l'effet de champ électrique", qui consiste à moduler de façon électrostatique une densité de charges mobiles dans un semi-conducteur.

Fig. I.5: Cycle de croissance de l'industrie des semi-conducteurs [5].

Le transistor à effet de champ (MOSFET) repose sur l'action d'un champ électrique vertical. Ce champ permet de moduler localement la concentration des porteurs dans une zone semiconductrice appelée canal de conduction ou canal d'inversion, située entre deux réservoirs de charges (la source et le drain). Le champ électrique est régi par une électrode de commande, appelée grille, à travers une couche isolante que constitue le diélectrique de grille (Figure I.3). Le fonctionnement de cette électrode s'apparente à un interrupteur contrôlant le passage de l'état passant à l'état fermé. Cette propriété explique son utilisation massive, principalement dans la conception des circuits logiques.

On distingue deux types de transistors MOSFETs:

Les nMOS dont le canal d'inversion est constitué d'électrons. Le canal est alors dopé de type P et les zones de source et de drain sont dopées N.

Les pMOS dont le canal d'inversion est constitué de trous. Le canal est dopé N et les zones de source et de drain sont dopées P.

Ces deux types de transistors ayant un fonctionnement symétrique, on ne détaillera que le transistor nMOS par la suite.

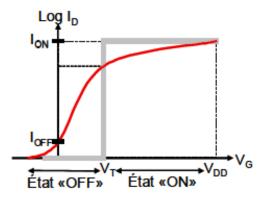

Figure I. 7: Caractéristique de sortie  $I_D(V_G)$  idéale (en trait gras) et réelle (en trait fin) d'un transistor nMOSFET [6]

Dans un cas idéal, lorsque la tension appliquée sur la grille est nulle  $(V_G=0v)$ , le champ électrique est nul, il n'y a aucun porteur dans le canal et le courant de drain  $(I_{ds})$  équivalant au courant de fuite  $(I_{OFF})$ : le transistor est bloqué. Au contraire, quand la polarisation de grille  $V_G$  est égale à celle du drain  $V_D$ , un champ électrique est créé, les porteurs affluent dans le canal, et peuvent alors transiter librement d'un réservoir à l'autre, générant un courant de drain non nul  $I_{DGT}$ : le transistor est alors passant (Figure I. 7). Le passage de l'état bloqué à l'état passant est effectif lorsqu'un nombre suffisant de porteurs est présent dans le canal, c'est-à-dire pour une tension  $V_G=V_T$ .

#### I.3.1 Régimes de fonctionnement du transistor MOSFET :

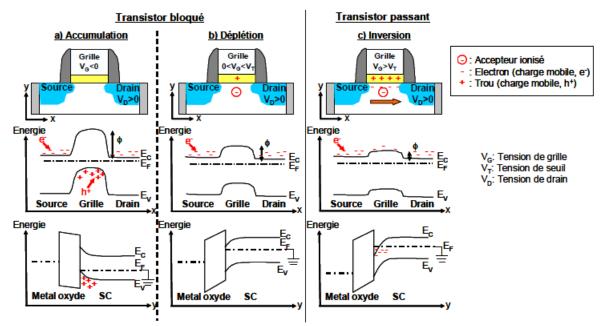

Pendant le fonctionnement du transistor, la tension entre la source et le drain est positive, créant un champ électrique horizontal pouvant mettre en mouvement les porteurs dans le canal, ou les dopants étant de nature différente dans le canal et les zones de source et de drain, une barrière énergétique, de hauteur  $\phi$ , apparaît entre le canal et les extensions. Cette barrière empêche le passage des porteurs entre la source et le drain si aucune polarisation n'est appliquée sur le dispositif. L'ensemble source/substrat/drain peut être vu comme une jonction npn. On peut distinguer alors trois situations en fonction de la tension  $V_G$  appliquée sur la grille (Figure I. 8).

Figure I. 8: Description schématique des différents états de fonctionnement d'un transistor nMOS. La première ligne est une représentation schématique du MOS. La seconde représente une coupe longitudinale de l'énergie le long du canal, et la dernière représente l'énergie suivant une coupe transverse au canal dans les régions Métal, Oxyde et Semi-conducteur [7]

Dans ce cas, la tension de drain est aussi la tension nominale d'alimentation  $V_{\scriptscriptstyle DD}$

$$V_G = V_D = V_{DD}$$

.

#### Régime d'accumulation

Une valeur largement négative de la tension de grille  $V_G$  crée un appel de trous (porteurs majoritaires du substrat) en surface du canal. On est en régime d'accumulation. L'énergie potentielle dans le canal est supérieure à celle de la source créant une barrière de potentiel. Le transistor est bloqué (Figure I.8.a).

#### Régime de désertion

A faible potentiel  $V_G$ , les trous (porteurs majoritaires) dans le substrat, sont repoussés en profondeur, ne laissant que les accepteurs ionisés (charges fixes de type opposé) dans le canal. Il apparaît alors une zone de charge d'espace où les charges fixes dues aux dopants créent une capacité de désertion ( $C_{DEP}$ ). Cela se traduit par une courbure de la bande de conduction en surface vers le niveau de Fermi. Le potentiel du canal demeure alors inférieur à celui de la source et le courant ne passe pas même si la barrière se voit déjà diminuée (Figure I.8.b).

#### Régime d'inversion forte et tension de seuil

Si l'on augmente encore le potentiel de grille $V_G$ , la bande de conduction est encore plus fortement courbée vers le niveau de Fermi: la barrière de potentiel source-canal  $\phi$  est quasi nulle (Figure I.8.c). La tension de seuil ( $V_T$ ) correspond alors à la tension de grille ( $V_G$ ) pour laquelle le régime du transistor passe de l'inversion faible à l'inversion forte. Cette notion de tension de seuil est fondamentale dans le fonctionnement du transistor MOS car elle gouverne la mise en conduction de celui-ci. La condition d'inversion forte est obtenue lorsque le potentiel de surface dans le canal est égal à deux fois la différence  $\phi_F$  entre le niveau de Fermi et le niveau intrinsèque du silicium (Figure I.6). Cette condition assure que le canal contienne des porteurs de même type que la source et le drain.

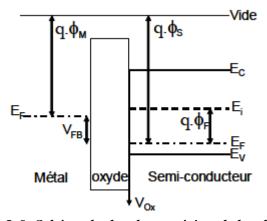

Figure I. 9: Schéma des bandes en régime de bande plates. Définition de la tension de bande plate  $(V_{FB})$ .  $V_G = V_{FB}$  [8].

Si l'on se place en régime de bande plate (Figure I.9) [8], où le potentiel de surface dans le canal est égal à celui dans le volume, il faut alors, pour amener le transistor en conduction, appliquer sur la grille une tension de seuil  $V_T$  telle que :

$$V_T = V_{FB} + V_{OX} + 2\phi_F \tag{I.1}$$

$V_{OX}$  étant la chute de potentiel dans l'oxyde et  $V_{FB}$  étant défini comme la tension de bande plate prenant en compte la différence  $\phi_{ms}$  des travaux de sortie du silicium et du matériau de l'électrode de grille ainsi que la présence de charges dans l'oxyde.

Ces charges pouvant être des charges fixes  $(Q_F)$  et des charges piégées à l'interface  $(Q_{SS})$ , la tension de bande plate peut alors s'écrire:

$$V_{FB} = \varphi_{ms} - \frac{Q_{SS}}{C_{OY}} - \frac{Q_F}{C_{OY}}$$

(I.2)

#### I.4 Quelles applications :

Le transistor MOS est principalement utilisé dans deux types d'applications :

Les applications à haute performance (HP) qui sont essentiellement les puces MPU (Micro Processor Unit) des ordinateurs de bureaux et des serveurs. La vitesse de calcul y est privilégiée au détriment de la consommation électrique qui est non négligeable que ce soit en fonctionnement ou en état de veille.

Les applications à basse consommation comme les dispositifs portables (ordinateur, téléphone). On y distingue les dispositifs opérant à faible puissance (LOP – Low Operating Power) pour les applications mobiles nécessitant une vitesse de calcul relativement grande et des batteries de large capacité (ordinateurs portables par exemple) et les dispositifs à très faible puissance de veille (LSTP – Low STandby Power) ayant de plus faibles courants de fuite avec des performances moindres.

A l'heure actuelle, de nombreuses applications demandent de plus en plus de puissance avec une portabilité toujours croissante. Les systèmes d'exploitation et autres applications logicielles sont de plus en plus gourmands en capacité de calcul. Il en résulte une course effrénée des industriels à l'augmentation de la puissance des dispositifs. Nous verrons par la suite que cette augmentation des performances passe par une miniaturisation des composants et que l'industrie des semi-conducteurs se trouve aujourd'hui face à des barrières technologiques: les constructeurs doivent innover pour continuer à améliorer les performances.

#### I.5 Miniaturisation des transistors

#### I.5.1 Pourquoi réduire la taille des transistors ?

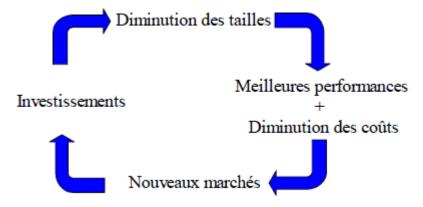

La croissance de l'industrie des semi-conducteurs dépend pour l'instant de sa capacité à miniaturiser les transistors. L'objectif de la démarche est de délivrer de meilleures performances à moindre coût [5].

Des circuits plus petits réduisent la surface globale de la puce électronique et permettent donc de produire plus de transistors sur un même wafer sans impacter sur le prix de fabrication. Le coût des circuits diminue ainsi d'un facteur deux tous les 18 mois. Les performances électriques des composants sont également améliorées (tableau (1.1)). En diminuant la dimension des MOSFETs, le temps de passage de l'état "off" à l'état "on" diminue linéairement du fait de l'évolution du temps de réponse intrinsèque ≈ longueur de canal/vitesse des porteurs.

Un autre avantage est la réduction de la consommation de puissance, utile pour augmenter la durée d'autonomie des systèmes mobiles mais aussi pour améliorer la fiabilité des systèmes hautes performances. Des puces plus petites consomment moins de puissance, donc moins d'énergie, sont utilisée pour chaque opération. En conséquence, le produit puissance temps de réponse est réduit. Enfin, la rapidité de transmission de l'information dans un circuit intégré est limitée par la vitesse de l'impulsion électrique. Pour pouvoir augmenter la rapidité globale d'une opération, il faut réduire les distances géométriques, et empiler un maximum de données d'information dans un minimum d'espace pour les rapprocher. Cette évolution permet à un large public d'accéder à des services plus performants, moins chers et souvent nouveaux. Des objets technologiques innovants sont ainsi produits et créent de nouveaux marchés dont les retombées financières sont réinvesties dans la course à l'intégration (Tab (I.1))

| Année                                               | 2004 | 2007 | 2010 | 2013 | 2016 |

|-----------------------------------------------------|------|------|------|------|------|

| Nœud technologique (nm)                             | 90   | 65   | 45   | 32   | 22   |

| Longueur de grille physique (nm)                    | 37   | 25   | 18   | 13   | 9    |

| Tension d'alimentation (V)                          | 1.2  | 1.1  | 1    | 0.9  | 0.8  |

| Epaisseur d'oxyde équivalent (nm)                   | 1.2  | 0.9  | 0.7  | 0.6  | 0.5  |

| Tension de seuil en saturation (V)                  | 0.2  | 0.18 | 0.15 | 0.11 | 0.10 |

| Courant de fuite nominal des NMOS ( $\mu A/\mu m$ ) | 0.05 | 0.07 | 0.1  | 0.3  | 0.5  |

| Courant conducteur nominal des NMOS (μA/ m)         | 1110 | 1510 | 1900 | 2050 | 2400 |

| Temps de réponse intrinsèque des NMOS (ps)          | 0.95 | 0.64 | 0.39 | 0.26 | 0.15 |

Tab I.1: Prévisions ITRS des caractéristiques des MOSFETs ultimes [9].

#### I.6 Effets canaux courts

De manière générale, les effets canaux courts que nous noterons SCE (Short Channel Effects) [10] – constituent tous des effets parasites qui influent sur les Deux effets parasites sont prédominants lorsque l'on atteint des dimensions très faibles : le partage de charge CS (Charge Sharing) et le DIBL (Drain Induced Barrier Lowering).

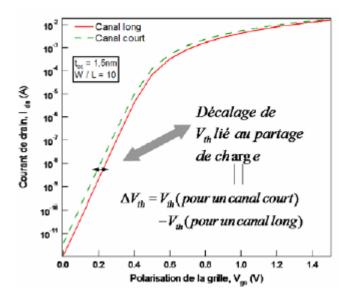

#### I.6.1 Partage de charge de déplétion (CS)

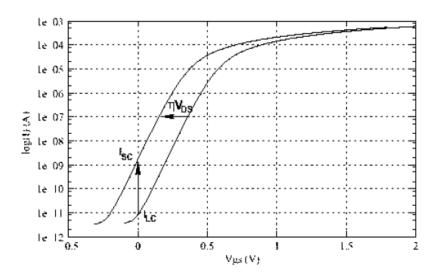

L'effet de partage de charge (CS) apparaît lorsqu'une partie significative du canal n'est plus contrôlée par la grille à cause de l'influence des jonctions de source et de drain. Quand  $V_{ds}$  augmente, la quantité de charge contrôlée par la grille diminue en dessous de sa valeur obtenue pour  $V_{ds} = 0v$ . Cet effet se traduit par une diminution de la tension de seuil et par une augmentation de la pente sous le seuil SS ainsi que du courant. Ce résultat s'observe bien sur la caractéristique  $I_d - V_g$  en échelle logarithmique de la figure (I.10).

En plus de cet effet canal court, on assiste à un effet canal étroit [11]. La région de déplétion effective créée par la tension de grille sous l'oxyde de grille s'étend latéralement. Cependant, contrairement à l'effet du canal court, cet effet dû au canal étroit conduit à une diminution de la valeur du courant et, ainsi, à une augmentation de la tension de seuil.

Fig. I.10 : Influence de l'effet du partage de charge sur la caractéristique du courant du transistor MOS pour  $V_d = 1v$  [11].

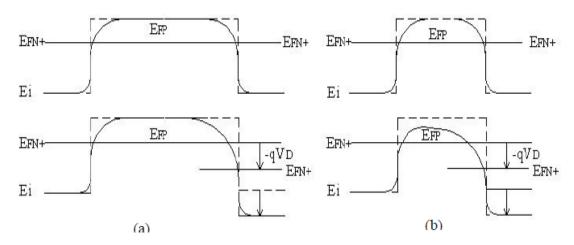

#### I.6.2 DIBL (abaissement de la barrière de potentiel induit par le drain)

Le phénomène de *DIBL* (« surface *DIBL* ») est pris en compte lorsque le transistor travaille en régime sous seuil (ou faible inversion) et concerne le potentiel de surface. En

faible inversion, le potentiel de surface dans le canal pour des dispositifs à canal long est à peu près constant et le courant est dû à la diffusion des porteurs minoritaires (Cette diffusion est due au gradient de concentration longitudinal aux jonctions). Le courant de drain dépend exponentiellement de la tension de grille. Il existe également, en régime de faible inversion, une barrière de potentiel à la jonction entre la source et le canal qui résulte de l'équilibre entre le courant de diffusion et de dérive (cas similaire à une jonction PN à l'équilibre). Si la tension au drain augmente [12], [13], la couche de déplétion s'étend de plus en plus dans le canal vers la source et il se produit un abaissement de la barrière source-canal.

L'abaissement de la barrière à la source permet l'injection d'électrons au travers du canal (en surface) et ceci indépendamment de la tension de grille. Comme conséquence, en régime sous seuil, la grille perd le contrôle du courant de drain. Un courant sous seuil important peut être observé quand la longueur du canal est inférieure à 1.5 µm. Cet effet est d'autant plus marqué que la tension de drain augmente et que la longueur de canal diminue (Figure I.11) [14].

Figure I.11: Profile du potentiel de surface pour des transistors n-MOS à canal (a)long et (b) court[12].

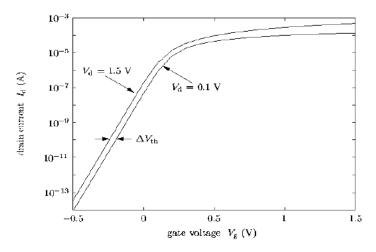

L'effet DIBL est habituellement mesuré par le décalage de la courbe de transfert en régime sous seuil  $\Delta V_{th}$  divisé par le  $\Delta V_D$  entre deux courbes résultant de deux tensions de drain différentes :

$$DIBL = \frac{\Delta V_{th}}{\Delta V_{D}} \left( \frac{mv}{v} \right) \tag{I.3}$$

Figure I.12: Courbes de transfert pour des tensions de drain de 0.1V (Régime linéaire) et 1.5V (régime de saturation) [13].

Il faut remarquer que le phénomène de *DIBL* se produit avant que la zone de déplétion du côté du drain (plus en profondeur dans le substrat) ne rencontre celle du côté de la source sous l'effet d'une augmentation de la tension de drain.

En vue d'atténuer les effets de canal court, il est courant d'augmenter le dopage du canal.

Ceci permet de réduire l'extension de la zone de charge d'espace et donc réduit l'interaction entre le drain et la source.

#### I.6.3 Courant sous seuil

Le courant sous seuil est un courant qui circule entre le drain et la source du transistor [15], alors que la tension de grille  $V_{GS}$  est inférieure à la tension de seuil $V_T$ .

Le comportement de ce courant a évolué au fur et à mesure de l'apparition des technologies submicroniques; c'est pourquoi, il convient de distinguer deux cas selon la longueur du canal du transistor.

Dans une approximation au premier ordre, pour les transistors à canaux longs, le courant sous seuil est donné par l'équation suivante:

$$I_{DS} = \mu C_{OX} \frac{W}{L} \phi_t^2 \exp^{\left(\frac{V_{GS} - V_t}{\phi_t}\right)} \left(1 - \exp^{\left(\frac{V_{DS}}{\phi_t}\right)}\right)$$

(I.4)

Où

$$\phi_t = \frac{KT}{q}$$

$$n = 1 + C_D / C_{OX}$$

Avec:

$C_D$ : la capacité de la couche déplétée.

$C_{ox}$ : la capacité de l'oxyde de grille.

Comme la tension de polarisation inverse,  $V_{DS}$  est grande devant  $\phi_t$  (=25mv à 300K), l'expression (I.4) peut se mettre sous la forme mieux connue de (I.5):

$$I_{DSth} = \mu C_{OX} \frac{W}{L} \left(\frac{KT}{q}\right)^2 \exp^{\left(\frac{q(V_{GS} - v_t)}{nKT}\right)}$$

(I.5)

La caractéristique du courant sous seuil est généralement représentée par une échelle semi-logarithmique ( $\log 10(I_{DSth})$ ) en fonction de  $V_{GS}$ . Cette caractéristique est par conséquent une droite. L'inverse de la pente sous seuil (output swing) est donnée par:

$$S = \frac{nKT}{q}\ln(10) \tag{I.6}$$

Plus le facteur S est petit, plus le courant sous seuil sera négligeable pour une tension de grille donnée. Il faut donc minimiser le coefficient d'effet de substrat  $n(n=1+C_D/C_{OX})$  c'est-à-dire n proche de 1. On peut minimiser l'effet de substrat en réduisant  $C_D$ , c'est-à dire en diminuant le dopage du substrat (Formule I.7 et I.8).

$$C_D = \frac{\mathcal{E}_{si}}{W_D} \tag{I.7}$$

$$W_D = \sqrt{\frac{4\varepsilon_{si}\phi}{qN_D}} \tag{I.8}$$

Où

$W_D$ : est l'épaisseur de la couche de déplétion dans le substrat.

$\phi$  : est le potentiel de Fermi dans le substrat.

$N_D$ : la concentration en impureté du substrat.

Habituellement, on mesure la valeur de la pente de la partie linéaire de la courbe correspondant à la conduction sous la tension de seuil. Plus la pente est élevée, plus le courant de fuite sera faible.

Pour les transistors à canal court (géométries fortement submicroniques), l'effet d'abaissement de la barrière de potentiel induite par le drain intervient, le courant sous seuil devient :

$$I_{DS} = \mu C_{OX} \frac{W}{L} \phi_t^2 \exp^{\left(\frac{V_{GS} - V_t + \eta V_{DS}}{n\phi_t}\right)} \left(1 - \exp^{-\left(\frac{V_{DS}}{\phi_t}\right)}\right)$$

(I.9)

On obtient également (pour  $V_{\mathit{GS}} \succ \succ \phi_{\scriptscriptstyle{t}}$ ), l'expression simplifiée:

$$I_{DS} = \mu C_{OX} \frac{W}{L} \left(\frac{KT}{q}\right)^2 \exp^{\left(\frac{V_{GS} - V_t + \eta V_{DS}}{n\frac{KT}{q}}\right)}$$

(I.10)

Le facteur  $nV_{DS}$  diminue la valeur effective de  $(-V_t)$  et par conséquent augmente la valeur du courant de fuite. Ceci équivaut à une réduction de la tension de seuil et donc à décaler la courbe  $\log (I_{DSth})$  en fonction de  $V_{GS}$  (Figure I.13) vers la gauche.

La figure (I.13) montre que la réduction de la longueur du canal augmente le courant sous seuil et par conséquent une dégradation au niveau de fonctionnement du transistor MOSFET sera observée.

Figure I.13: Effet canal court sur le courant sous seuil [15].

#### I.6.4 Tension de seuil

La tension de seuil est l'un des paramètres essentiels [16] de fonctionnement du transistor MOS. Elle est définie comme étant la tension à appliquer à la grille pour obtenir la forte inversion, c'est-a-dire :

$$\psi_s = 2.\phi_F \tag{I.11}$$

$$V_{th} = V_{FB} + 2.\phi_F + \frac{\sqrt{4.e.N_A \varepsilon_{si}.\phi_F}}{C_{OVI}}$$

(I.12)

$$V_{FB} = \phi_{M} - \phi_{si}$$

$\phi_M$  sont tels que  $e.\phi_M$  et  $e.\phi_{si}$  représentent respectivement les travaux de sortie de la grille et du silicium,  $\varepsilon_{si}$  est la constante diélectrique du silicium, et enfin  $C_{ox1} = (\varepsilon_{ox}/t_{ox})$  désigne la

capacité de l'oxyde. Cette expression de  $V_{th}$  (I.12) est valable pour le transistor MOS à canal long.

#### I.7 Modélisation de l'effet de High-k (HfO<sub>2</sub>)

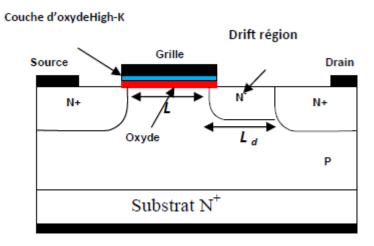

L'oxyde d'hafnium HfO<sub>2</sub> avec sa permittivité relative  $\varepsilon_r$  de l'ordre de 20-80, son gap relativement grand de l'ordre de 5,65eV, et enfin sa relative stabilité thermodynamique sur le silicium semble être un bon candidat pour être utilisé avec la couche l'oxyde [17].

La figure (I.14) montre que l'implémentation d'une couche d'oxyde de valeur de permittivité élevée High-k entre la couche d'oxyde et la grille joue un rôle important pour la réduction de l'effet de l'auto-échauffement sur le fonctionnement du transistor LDMOSFET et par conséquence l'amélioration des performances de notre transistor.

Figure (I.14): Coupe schématique d'un LDMOS de type N avec une couche d'oxyde de valeur de permittivité élevée High-k[17].

#### **I.8 Conclusion:**

Pour conclure, nous pouvons souligner que le transistor MOS double grille est intéressant compte tenu des performances électriques qu'il offre la difficulté majeure dans son développement se situe au niveau technologique. Plus précisément, concernant le transistor MOS double grille planaire, la difficulté est l'alignement des deux grilles.

# CHAPITRE 2 TRANSISTOR A GRILLE MULTIPLE

#### **II. Introduction**

Dans ce contexte, de nouveaux dispositifs émergent comme alternatives pour les prochaines générations technologiques. Ces dispositifs sont divers et variés. Nous pouvons citer les transistors sur substrat *SOI* (*Silicon On Insulator*) ainsi que les dispositifs multi grilles: les FinFETs, les MOSFETs Double Grille (*DG MOSFET*), Triple Grille et à Grilles Enrobantes (*GAA : Gate All Around*).

#### **II.1 Construction du MOSFET**

#### II.1.1 Matériau de grille

Le principal critère pour le matériau de grille, c'est qu'il est un bon conducteur. Silicium poly cristallin fortement dopé est conducteur acceptable un mais certainement pas idéal, et souffre également de quelques lacunes plus techniques dans son rôle en tant que matériau de grille standard. Néanmoins, il plusieurs va raisons favorisant l'utilisation de silicium poly cristallin:

La tension de seuil (et par conséquent le drain à la source aliment le courant) est modifié par la différence entre la fonction de travail matériau de grille et le matériel de canal, par ce que le silicium poly cristallin est un semi-conducteur, sa fonction de travail peut être modulée en ajustant le type et le niveau de dopage. Par ailleurs, en raison de poly silicium est la bande interdite même que le canal de silicium sous-jacent, il est assez simple de régler la fonction de travail pour atteindre des tensions de seuil bas pour les deux transistors NMOS et PMOS périphériques. En revanche, les fonctions de travail des métaux ne sont pas facilement modulées, donc la fonction de syntonisation de travail pour obtenir des tensions de seuil bas devient un défi important. De plus, l'obtention à bas seuil sur les deux appareils et dispositifs PMOS NMOS nécessiterait probablement l'utilisation de métaux différents pour chaque type d'appareil, introduire de complexité supplémentaire pour le processus de fabrication.

L'interface silicium SiO<sub>2</sub> a été bien étudiée et est connu pour avoir des défauts relativement peu nombreux. En revanche de nombreuses interfaces métal-isolant contiennent des niveaux importants de défauts qui peuvent conduire à niveau de Fermi épinglage, de chargement, ou d'autres phénomènes qui dégradent la performance du dispositif en fin de compte. Dans le processus de fabrication MOSFET, il est préférable de déposer le matériau de grille avant certaines étapes à haute température afin de réaliser des transistors plus performants. Ces étapes à haute température feraient fondre certains métaux, limitant les types dans métal qui peut être utilisé un processus de métal porte-base. Alors que les portes de poly silicium ont été la norme de facto pour les vingt dernières années, ils ont quelques inconvénients qui ont conduit à leur remplacement futur probable par des portes métalliques. Ces inconvénients sont:

Poly silicium n'est pas un grand chef d'orchestre (environ 1000 fois plus résistant que les métaux) qui réduit la vitesse de propagation du signal à travers le matériau. La résistivité peut être abaissée en augmentant le niveau de dopage, mais même poly silicium fortement dopé n'est pas aussi conductrice que la plupart des métaux. Afin d'améliorer la conductivité

d'autres, parfois un métal à haute température tels que le tungstène, titane, cobalt, de nickel et plus récemment est allié avec les couches supérieures du silicium poly cristallin. Un tel matériau est appelé mélange de siliciure. La combinaison siliciure-silicium poly cristallin a de meilleures propriétés électriques de poly silicium seul et n'a toujours pas fondu dans le traitement ultérieur. Aussi la tension de seuil n'est pas significativement plus élevée qu'avec poly silicium seul, parce que le matériel siliciure n'est pas près du canal. Le processus dans lequel siliciure est formé sur les deux l'électrode de grille et la source et de drain est parfois appelé salicide, auto-alignés siliciure.

Lorsque les transistors sont extrêmement réduits, il est nécessaire de faire la couche de diélectrique de grille très mince, d'environ 1 nm dans l'état de l'art des technologies. Un phénomène observé ici est l'épuisement dit poly, où une couche d'ozone est formée dans la couche silicium poly cristallin de grille à côté de diélectrique de grille lorsque le transistor est dans l'inversion. Pour éviter ce problème, un portail en métal est souhaité. Une variété de portes en métal comme le tantale, le tungstène, le nitrure de tantale et de nitrure de titane sont utilisés, généralement en conjonction avec diélectriques high-k. Une alternative est d'utiliser les portes de poly silicium entièrement siliciuré, un processus connu sous le nom FUSI.

#### II.1.2 Grilles métalliques

L'utilisation du poly-silicium de grille provoque la déplétion des porteurs au sein du poly-silicium en régime d'inversion. Ainsi les porteurs dans la grille sont repoussés de l'interface grille-oxyde [18]. Il se crée donc une capacité parasite dans la grille qui diminue la capacité totale de la structure MOS et la rapidité des dispositifs. Ce phénomène de déplétion de grille peut être éliminé par l'utilisation d'une électrode métallique, laquelle offre également une plus grande flexibilité sur l'ajustement de la tension de seuil des dispositifs.

#### II.1.3 Déplétion de grille

L'utilisation du poly-silicium de grille provoque la déplétion des porteurs au sein même du poly-silicium en inversion. Ce phénomène est connu sous le nom de déplétion du poly-silicium de grille [18–20]. Cette déplétion entraı̂ne la diminution du courant de saturation  $I_{on}$  et l'augmentation effective de l'épaisseur d'oxyde. Ceci a pour conséquence directe, une diminution du contrôle de la grille sur le potentiel dans le canal. Le phénomène de déplétion de grille peut être éliminé par l'utilisation d'une électrode métallique, laquelle offre, en outre, la possibilité d'ajuster la tension de seuil des dispositifs. L'ajustement de la

tension de seuil se fait par le biais de l'ajustement du travail de sortie de la grille métallique. Parmi les matériaux métalliques potentiellement au cœur des recherches dans ce domaine, se trouvent les matériaux de type midgap dont les travaux de sortie sont identiques à celui du silicium. Nous pouvons citer le  $T_iN$  comme exemple de matériau de ce type.

#### II.1.3.1 Amélioration du contrôle de la grille sur la charge de déplétion

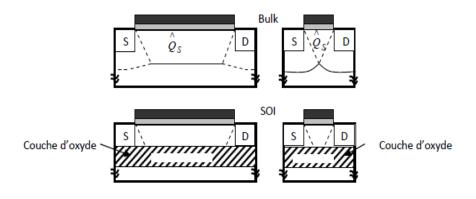

Ainsi que nous l'avons signalé dans la première section, les modèles de séparation de charge fournissent la proportion de la charge de déplétion contrôlée par la grille par rapport à celle contrôlée par la source et le drain. Si nous comparons le transistor MOS bulk au transistor SOI, avec des dimensions identiques  $(L, W, t_{ox}, X_j)$ , nous constatons que le rapport entre la charge de déplétion contrôlée par la grille et le drain (ou la source) est beaucoup plus important en technologie SOI. Comme la montre la figure (II.1), ce phénomène est d'autant plus marqué que la longueur du canal diminue.

Fig. II.1 : Distribution de la charge de déplétion pour le MOSFET bulk et le SOI [21]

#### II.2 Défférentes structures du transistor

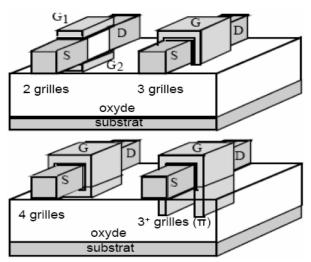

#### **II.2.1 Structure double grille:**

Le transistor MOS double grille (DG) est constitué de deux grilles placées sur le plan horizontal. La figure II.2 en présente l'architecture. Chaque grille exerce un contrôle sur le ou les canaux. Il existe une autre structure qui appartient à la catégorie du double grille bien qu'elle possède trois grilles ; elle est souvent appelée dans la littérature, le FinFET. Cette structure dispose d'une « troisième grille » reliant les deux autres grilles. Par rapport à un dispositif MOSFET double grille planaire, l'avantage d'un transistor FinFET est l'auto-alignement intrinsèque des deux grilles. La « troisième grille» se trouve sur une couche

d'oxyde de grille d'une épaisseur importante. De ce fait, elle n'effectue aucun contrôle sur le canal. Ainsi, seules les deux grilles latérales créent et contrôlent un canal d'inversion [22].

De plus, on observera qu'au niveau de la structure MOSFET double grille planaire, il existe deux variantes. Suivant la manière dont le dispositif est polarisé, nous assistons à des modes de fonctionnement différents. Nous avons ainsi le MOSFET double grille en mode de fonctionnement symétrique et le MOSFET double grille en mode de fonctionnement asymétrique.

#### II.2.2 Structure triple-grille:

Cette structure dispose de trois grilles (TG), dont une au-dessus de l'oxyde et une sur chaque face latérale (Fig II.2). Les couches d'oxyde au contact de chacune des grilles ont une épaisseur suffisamment faible pour permettre la formation de trois canaux à l'intérieur du film de silicium [22].

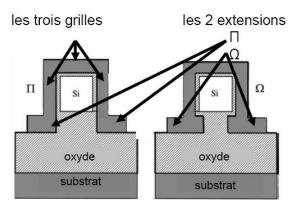

Fig. II.2: Les différentes structures multi-grilles : SOI double-grille (2), SOI triple-grille (3), SOI quadruple-grille/Surrounding-gate (4), et grille en forme  $\Pi$  ou  $\Omega$  (3+)[22]

Suivant la forme de ces extensions, l'architecture diffère [23]. Si ces extensions se développent verticalement dans l'oxyde enterré, soit suivant la continuité des grilles latérales, nous parlons de structure  $\Pi$  FET. Si ces extensions se développent horizontalement, soit perpendiculairement aux grilles latérales, nous parlons de  $\Omega$  FET.

Ces extensions sont généralement obtenues en sur-gravant l'oxyde dans la phase de définition des zones actives. Leur rôle consiste à améliorer considérablement le contrôle électrostatique de la grille.

# **II.2.3** Structure triple <sup>+</sup> grille :

Ces transistors sont représentés dans la Figure (II.3). Ils sont constitués non seulement de trois grilles positionnées au-dessus de l'oxyde de grille et sur les faces latérales, mais également de deux extensions [23].

# II.2.4 Structure quadruple-grille:

Ce composant possède quatre grilles (QG). La structure est décrite à la figure (II.2) Le film de silicium est recouvert de grille sur les quatre faces, d'où leur autre nom : "surrounding-gate" [24]. Des études restent encore à mener pour déterminer tous les avantages de ce type de composant.

L'idée d'ajouter de plus en plus de grilles repose sur le fait que, si l'épaisseur du film actif de silicium entre les différentes grilles est suffisamment faible, ces grilles polarisées peuvent commander le volume global de silicium entre la source et le drain. La conduction s'effectuant alors de manière volumique et non plus surfacique, on s'attend à des effets avantageux pour la valeur du courant de drain. De plus, la prise de contrôle du canal se révélant plus importante, on s'affranchit des effets canaux courts liés à l'influence de  $V_{ds}$ : la diminution drastique de l'épaisseur d'isolant devient moins cruciale. Enfin, par leurs dispositions, les grilles font enseigne de bouclier contre les lignes de champs créées par la polarisation du drain et qui influent sur la circulation des électrons. Finalement, les performances sont nettement améliorées avec de telles architectures multi-grilles.

A cet effet, elles font l'objet actuellement de recherches intenses dans de nombreux laboratoires.

Fig. II.3: L'extension des grilles conduisant aux structures  $\Pi$  et  $\Omega$  SOI MOSFETs [24]

L'un des inconvénients de ces structures est l'accroissement des résistances des extensions source et drain. De plus, les dimensions de la zone active étant réduites à moins de quelques dizaines de nanomètres dans toutes les directions, de multiples questions se posent quant à la

physique du transport dans ces dispositifs : importance du transport balistique ou par effet tunnel entre source et drain. Finalement, le point qui reste de loin le plus critique réside, bien entendu, dans leur fabrication qui nécessite la mise en œuvre de procédés plus que délicats.

# II.3 Transistors à grille enrobée

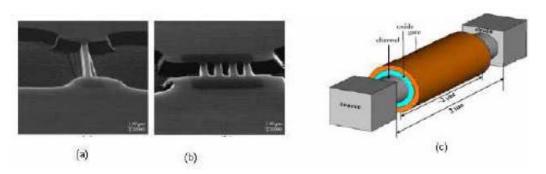

Le transistor à grille enrobée SG (Surrounding Gate) ou GAA (Gate All Around) MOSFET (figure II.4) représente la structure qui théoriquement offre la meilleure contrôlabilité de la grille sur le canal et donc la meilleure intégrité électrostatique possible [25].

Le premier SG MOSFET fut fabriqué en enveloppant l'électrode de grille autour d'une pile verticale de silicium. Les structures à grille enrobée incluent des composants tels que le CYNTHIA (à section circulaire) et le SG MOSFET en colonne (à section carrée). Des SG SOI MOSFETs d'une longueur de grille inférieur à 5nm ont montré une totale fonctionnalité. Plus récemment, des SG MOSFET planaire à section circulaire ou carrée ont été rapportés.

Figure II.4: Vue TEM (a) d'un et (b) de 4 canaux de MOSFETs à grille enrobée, (c) vue 3D d'un nanofile MOSFET [26].

Néanmoins, la structure à section cylindrique est plus avantageuse compte tenu de l'absence d'angles droits ou de coins, il a été montré qu'une inversion prématurée peut survenir au niveau des coins, ce qui dégrade les caractéristiques sous seuil et crée une déformation indésirable dans la courbe de transconductance versus tension de grille [27]. Une comparaison entre les deux structures a été effectuée dans [28], les résultats de simulation ont confirmé l'avantage de la structure à section cylindrique avec une diminution considérable du courant  $\mathbf{I}_{nff}$ , et une réduction du *DIBL* et de l'inverse de la pente sous seuil.

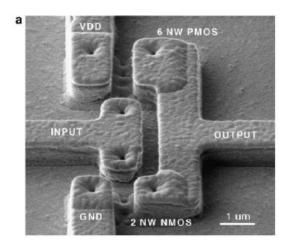

Figure II.5: Image SEM (a) de l'inverseur en GAA nanofile, (1x2) canalNMOS et (3x2) canal PMOS, (b) multiple nanofiles en rangée d'une excellente symétrie [29].

Les transistors à grille cylindrique se sont très bien adaptés à la technologie CMOS et à la l'intégration à très large échelle. Dans [30], un inverseur à base de nanofiles submicroniques d'environ 300nm et d'une épaisseur de 5nm a été réalisé avec succès (figure II.5). Une très bonne performance a été enregistrée tant au niveau de l'inverseur qu'à celui des nanofiles.

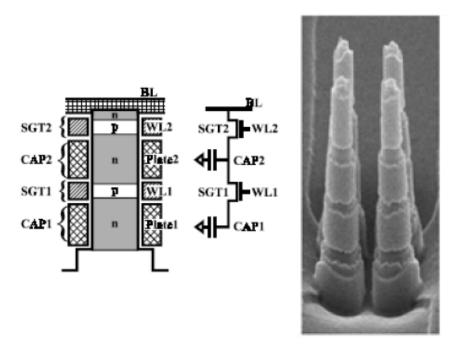

Les SG MOSFETs planaires submicroniques voir nanométriques permettent de réduire la surface unitaire des circuits, cependant, une disposition verticale des transistors permet une plus dense intégration. Dans [30], une structure de DRAM à base de transistors SG empilés (Stacked SGT) a été proposée (figure II.6), la simulation du procédé de fabrication a montré que l'empilement permet de réduire la taille de la cellule de moitié par rapport à une cellule SGT conventionnelle.

Le transistor VSG MOSFET représente la structure la plus optimale qui allie performance électrique et grande densité d'intégration.

Figure II .6 : (a) structure de la S-SGT DRAM(b) circuit équivalent (c) image SEM de cellule S-SGT [30].

# II.4 L'architecture MOSFET à grille enrobée

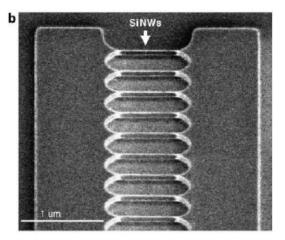

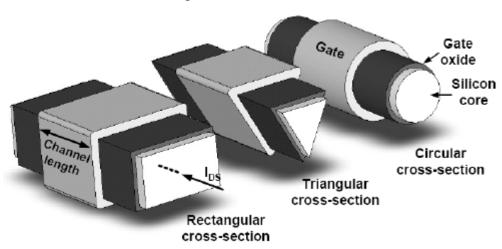

Le transistor MOSFET à grille enrobée SGT "surrounding gate transistor " [31] (gate all- around, GAA) [32] est une architecture MOSFET avancée ou le canal en silicium est complètement entouré par la grille. Comme le montre la figure (II.7), trois différentes formes de section sont représentées [33]. Les transistors GAA seront décrits en détail dans ce rapport de thèse parce que c'est la géométrie choisie pour la modélisation neuronale et la modélisation et simulation des circuits nanométriques.

Figure II.7 Trois architectures du transistor GAA MOSFET avec des sections différentes [33]

Les transistors GAA sont des excellents dispositifs, en termes de SCE, DIBL, pente sous le seuil et le rapport  $I_{ON}/I_{OFF}$ . L'inconvénient principal du dispositif GAA est généralement pour le moment consiste aux procédés de fabrication qui sont très difficile. Cette fabrication est souvent basée sur la réalisation de nano fils de silicium. La section du canal est également cruciale pour le fonctionnement du dispositif. Les coins dans le canal (en forme rectangulaire ou triangulaire) contribuent dans les effets de coin, et sont considérés comme des parasites (tension de seuil double) ou parfois des effets bénéfiques (tension de seuil basse, inversion volumique local).

Les transistors GAA à nano fils de silicium sont également des structures très convenables dans les dispositifs à un seul électron (SET) [33].

De 1990 à 2000, les auteurs ont surtout été intéressés à la modélisation des propriétés électroniques utilisant la mécanique quantique, et de nombreuses publications sont encore déconnectées de toutes les demandes de dispositif [34].

Le calcul de la bande interdite de silicium dans un fil quantique de silicium a été proposé la première fois en 1993 par *M.-Y*. Shen [35].

Le premier transistor GAA sur SOI a été présenté en 1990 par *J.-P*. Colinge [36]. Malgré ces grandes dimensions (W/L=3μm/3μm) et une épaisseur de 50 nm d'oxyde de grille, ces dispositifs pionniers présentent des caractéristiques correct. La fabrication du dispositif est très simple. Un fil SOI mince est défini par lithographie et gravure, cette étape est suivie par la formation du fil de l'oxyde enterré.

La grille utilisée est du LPCVD poly silicium.

Un autre remarquable GAA transistor MOS a ensuite été proposé en 1997 par E. Leobandung et al [37]. C'est l'un des premiers rapports qui comprend une description complète des performances GAA. Les dimensions du nano-fil sont en accord avec les prédictions de l'ITRS en 1997. Le fil a une section transversale rectangulaire (hauteur x largeur 50 nm 35-75nm), la longueur de fil minimum est 70 nm et l'épaisseur de l'oxyde de grille est 11nm. Le poly silicium est aussi utilisé comme matériau d'oxyde de grille. Les caractéristiques extraites sont bonnes, avec une pente sous seuil 90mV/dec. Une conception multi-canal est également proposée.

Depuis lors, de nombreux designs optimisés ont été rapportés.

Nous pouvons nous référer à *J. Y. Song* et al [38]. et *S. D. Suk et al.* [39]Qui ont effectues deux excellents rapports sur la technologie GAA CMOS. L'article [40]fait une comparaison entre les deux géométries double grille et GAA, et montre comment GAA augmente les

performances. En second lieu, ce rapport fait également une comparaison entre une forme rectangulaire et un canal de section circulaire, montrant que un canal en silicium cylindrique a un courant IOFF beaucoup plus réduit et les effets SCE et DIBL plus faible, en raison de l'absence des effets de coin. Les résultats publiés par ont également un grand intérêt et présente un processus pour l'intégration des MOSFET à double nano fils de silicium (twin silicon nanowire MOSFET). Ils ont obtenu des dispositifs GAA circulaire de 5-10 nm de diamètre avec une longueur de grille de 30nm, avec un courant Ion remarquablement élevé pour les transistors type n de  $2.64 \, mA/\mu m$ .

#### II.5 Différentes catégories de la technologie GAA MOSFET

Les transistors à grille enrobée GAA MOSFET peuvent être classés suivant des critères géométriques (la forme du canal) ou des critères électriques (la direction du transport électronique et la direction du champ de grille par rapport au plan du substrat qui est le plan horizontal) ou aussi le nombre des canaux qu'ils possèdent. Ainsi, pourrons-nous distinguer :

# II.5.1Transistor GAA MOSFET rectangulaire

L'architecture du transistor GAA MOSFET rectangulaire est basée sur celle du SOI à triple grilles (tri-gate) on ajoutant une grille d'où il tire le nom de quadruple-grille (quadruple gate [41]). La coupe du canal d'un tel transistor est sous forme d'un rectangle [42-44]. On note ici qu'il dérive de cette architecture deux autres nominations, GAA MOSFET à canal cubique [41] et GAA MOSFET carré [44] (voir figure (II.7)).

#### **II.5.2** Transistor GAA MOSFET triangulaire

Le transistor GAA MOSFET triangulaire [45-46] tire son nom de la section de son canal qui est sous la forme d'un triangle (voir figure (II.7)).

#### II.5.3 Transistor GAA MOSFET cylindrique

Le nom du transistor GAA MOSFET cylindrique découle de la forme de son canal qui est sous la forme d'un cylindre [39-40] et il porte aussi le nom de transistor à canal circulaire. La figure II.10.a illustre cette architecture (voir figure (II.7))

#### **II.6 Conclusion**

La miniaturisation des transistors MOS a permis d'augmenter la densité d'intégration et la vitesse de fonctionnement des circuits. Cette réduction des dimensions a engendré des phénomènes parasites qui dégradent les caractéristiques des composants. Ainsi, une solution alternative au transistor MOS bulk devient-elle progressivement nécessaire. Tout comme il y a soixante ans, lors de l'avènement de l'électronique sur semi-conducteur au détriment des tubes à vide, de nouveaux dispositifs permettant d'améliorer, voire de remplacer la technologie MOSFET bulk,

# CHAPITRE 3 ALGORITHMES GENETIQUES

#### **III. Introduction**

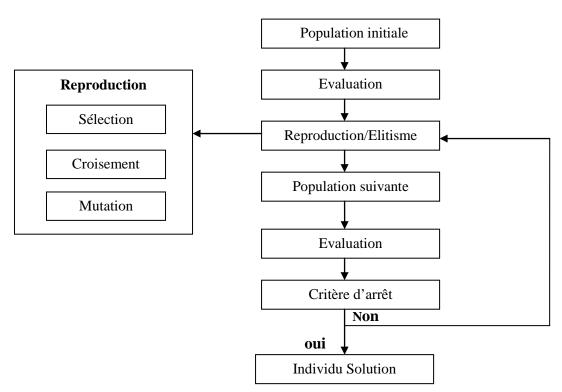

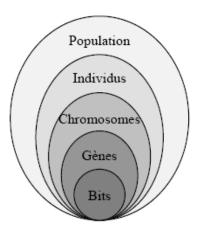

Les algorithmes génétiques sont des algorithmes d'exploration fondés sur les mécanismes de la sélection naturelle et de la génétique et sur la théorie de l'évolution des espèces de Charles Darwin [49]. Ils utilisent à la fois les principes de la survie des structures les mieux adaptées, et les échanges d'information pseudo-aléatoires, pour former un algorithme d'exploration qui possède certaines des caractéristiques de l'exploration humaine. Ils sont une transcription directe du processus naturel d'évolution au monde de l'informatique.

Les possibilités espérées des mécanismes d'évolution ont conduit quelques chercheurs des années 1950 à vouloir les simuler pour les appliquer à l'ingénierie. Mais ces travaux n'ont pas été probants en raison des connaissances insuffisantes, à l'époque, de la génétique naturelle et aussi en raison des faibles performances des calculateurs alors disponibles. Mais depuis le début des années 60, la quantité de travaux sur les algorithmes évolutionnaires suit une croissance exponentielle Les premier travaux de John Holland remontent aux années 1960 et ont trouvé un premier aboutissement en 1975 avec la publication de « Adaptation in Natural and Artificial Systems » [50]. C'est cependant l'ouvrage de David Goldberg qui a largement contribué à développer les algorithmes génétiques [51].

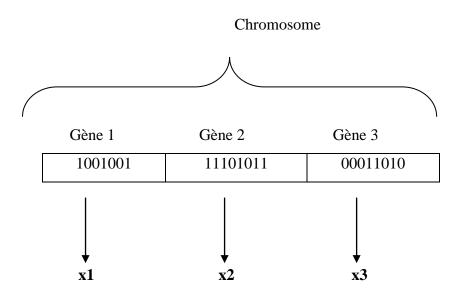

En effet, les AGs ont des propriétés qui en font des candidats de choix pour résoudre des problèmes d'optimisation dans lesquels la taille de l'espace de recherche est importante. Les AGs sont fondés sur :

- Une représentation chromosomique des solutions du problème.

- Une méthode pour générer une population initiale de solutions.

- Une méthode d'évaluation qui classe les solutions selon leurs aptitudes.

- Des opérateurs génétiques, qui définissent la manière dont les caractéristiques des parents sont transmises aux descendants.

#### III.1 Algorithmes évolutionnaires

Les Algorithmes Evolutionnaires (AE) sont des algorithmes stochastiques d'optimisation inspires du paradigme de l'évolution darwinienne des populations. Selon Darwin, les individus les plus aptes survivent à la sélection naturelle et se reproduisent et ceci se répète d'une génération à l'autre, menant à l'adaptation de la population des individus à l'environnement au cours de l'évolution. En termes d'optimisation, l'évolution se traduit par un processus itératif de recherche de l'optimum dans l'espace de décision.

Le critère pour définir les éléments les "plus aptes" d'un sous-ensemble fini de cet espace correspond, naturellement, à l'objectif d'optimisation. L'adaptation à l'environnement est réalisée par le fait de trouver à chaque itération suivante des solutions potentielles meilleures, la performance des solutions étant évaluée à la base des valeurs correspondantes de la fonction objective. Cependant, plusieurs techniques ont été inclues dans les algorithmes évolutionnaires telle que les Algorithmes génétiques qui sont l'objectif de la prochaine section.

# III.1.1 Algorithmes génétiques (GAs)

Le développement des techniques de solution de problèmes basées sur les principes d'héritage et d'évolution naturelle a été mis en évidence au courant des années soixante dix.

Parmi ces techniques ressort l'algorithme génétique. Cet algorithme a démontré de très bons résultats dans la résolution de problèmes d'origine combinatoire.

Les méthodes classiques d'exploration sont de trois types : les méthodes directes et indirectes (fondées sur le calcul), les méthodes énumératives et les méthodes aléatoires.